GPIO的内部结构与功能解析

一、GPIO总体结构

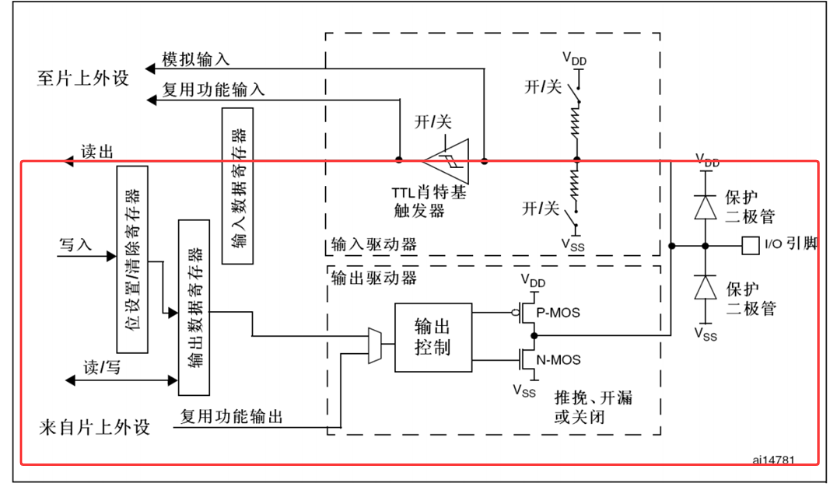

总体构成

1.APB2(外设总线)

APB2总线是微控制器内部连接CPU与外设(如GPIO)的总线,负责CPU对GPIO寄存器的读写访问,支持低速外设通信

2.寄存器

控制GPIO的配置(输入/输出模式、上拉/下拉等)和状态读取(输入电平、输出电平等)

3.驱动器

GPIO驱动器负责将寄存器中设置的电平信号转换为实际的电压输出,驱动外部负载。同时,驱动器也对输入信号进行缓冲和整形,确保信号稳定传输到输入寄存器,有着数据预处理作用

二、内部构造

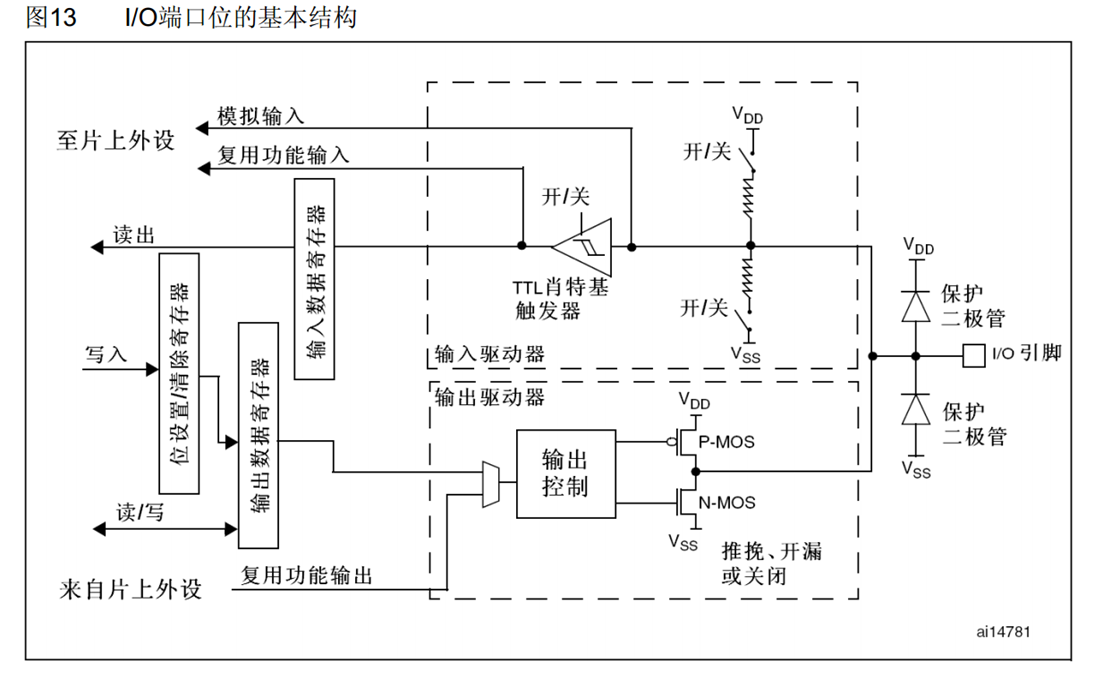

某一个端口内部的结构

1.保护二级管

二极管具有单项导通性,在输入情况下,当引脚电平低于Vss,Vss与引脚之间二极管导通,防止从GPIO内部汲取电流,同理,当引脚电平高于Vdd,引脚与Vdd之间二极管导通,防止GPIO内部电流过载。

2.上拉电阻和下拉电阻

为了解决引脚悬空导致输入电平不确定的状态,以接上拉电阻为例,可以保证默认输入电压为高电平,为什么呢,因为GPIO内部的等效电阻非常大,与上拉电阻串联,根据串联分压可以知道电阻的压降很小,所以输入等价于固定在高电平。那么为什么需要接上拉电阻呢,直接去掉不行吗?我的理解是:如果去掉上拉电阻,那么当输入引脚为0,那么输入驱动器内部的Vdd与输入引脚之间就短路,进而可能会导致元器件损坏。

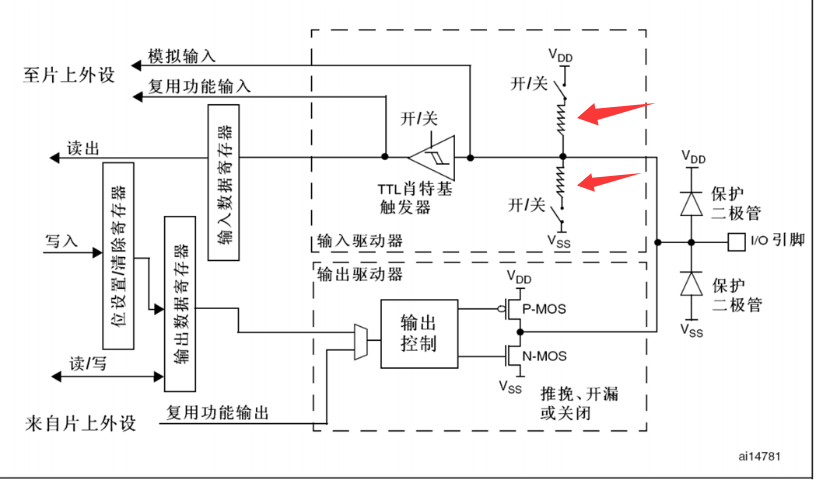

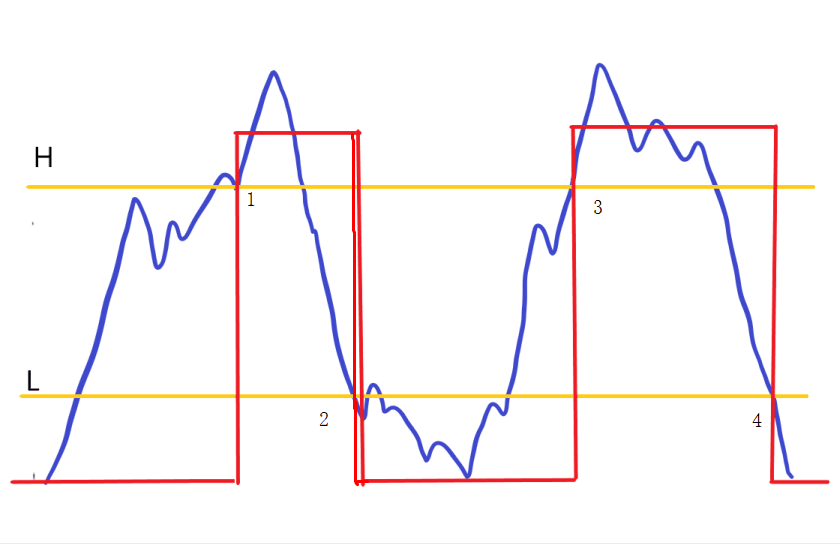

3.施密特触发器(如图中肖特基触发器,翻译错误)

用于对输入电压进行整型,提高输入的稳定性,图中输入到输入寄存器中的某一位,如下图所示,只有电压低于下线low或者高于上线low才会变化。同时由于片上外设ADC需要接受模拟量,因此可以在施密特触发器整型之前获取输入的模拟量。

4.端口输出

输入设置如下,经过二路选择器来选择输出的是GPIOx寄存器的指定比特位or复用功能信号。位设置/清楚寄存器可以用来操作寄存器中的某一位,而不影响其他位(输出数据寄存器只能整体读写)。输出控制,根据输出寄存器的位信息,当输出低电平,P-MOS导通,N-MOS截止,输出高电平,反之输出低电平。

GPIO的八种工作模式

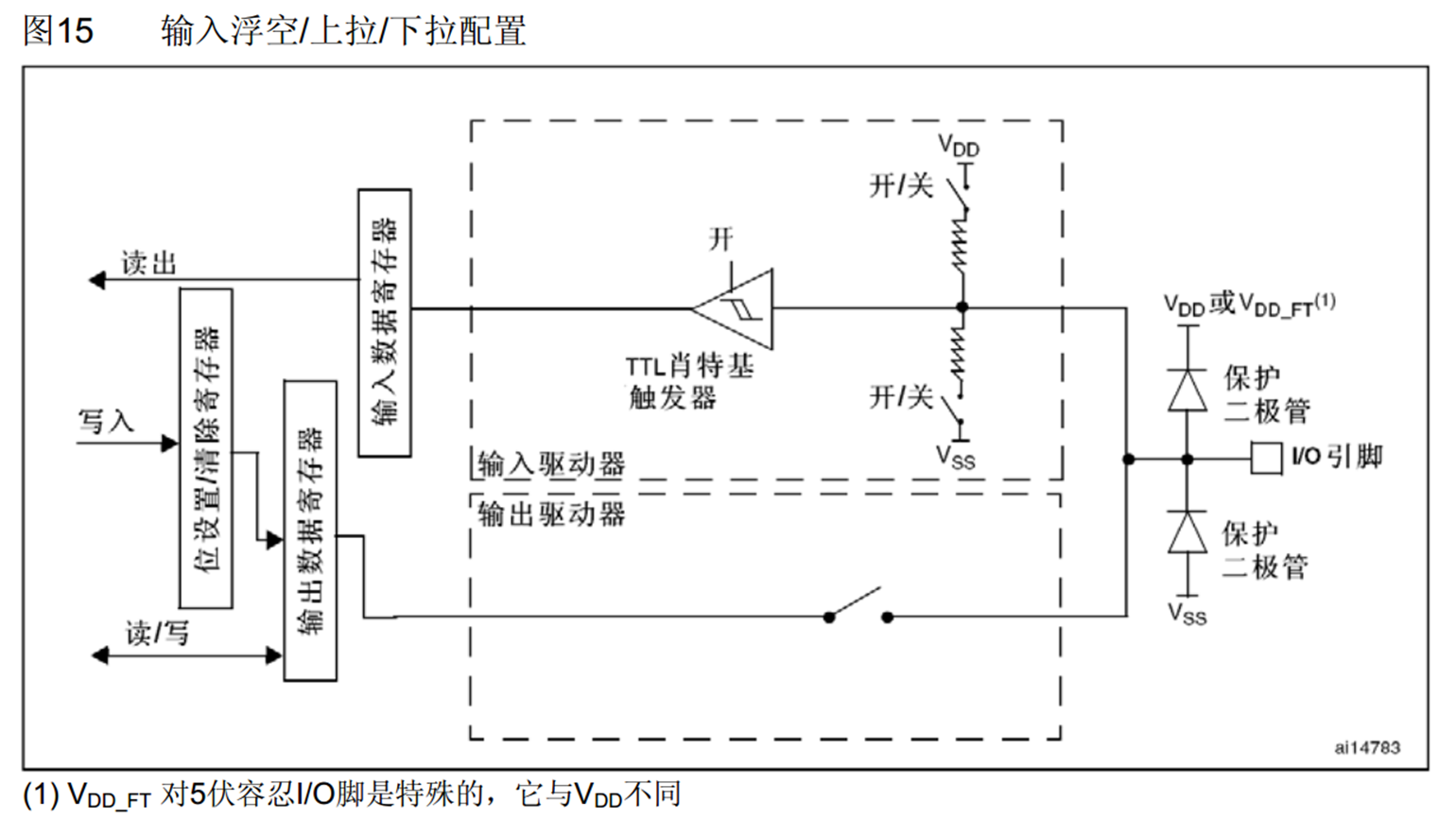

1.浮空输入、上拉输入、下拉输入

三种输入方式在于是否连接上拉电阻和下拉电阻,这种模式下输出控制断开,只进行输入。当引脚悬空时,浮空输入电平不确定,上拉输入电平默认高电平,下拉输入电平默认低电平。

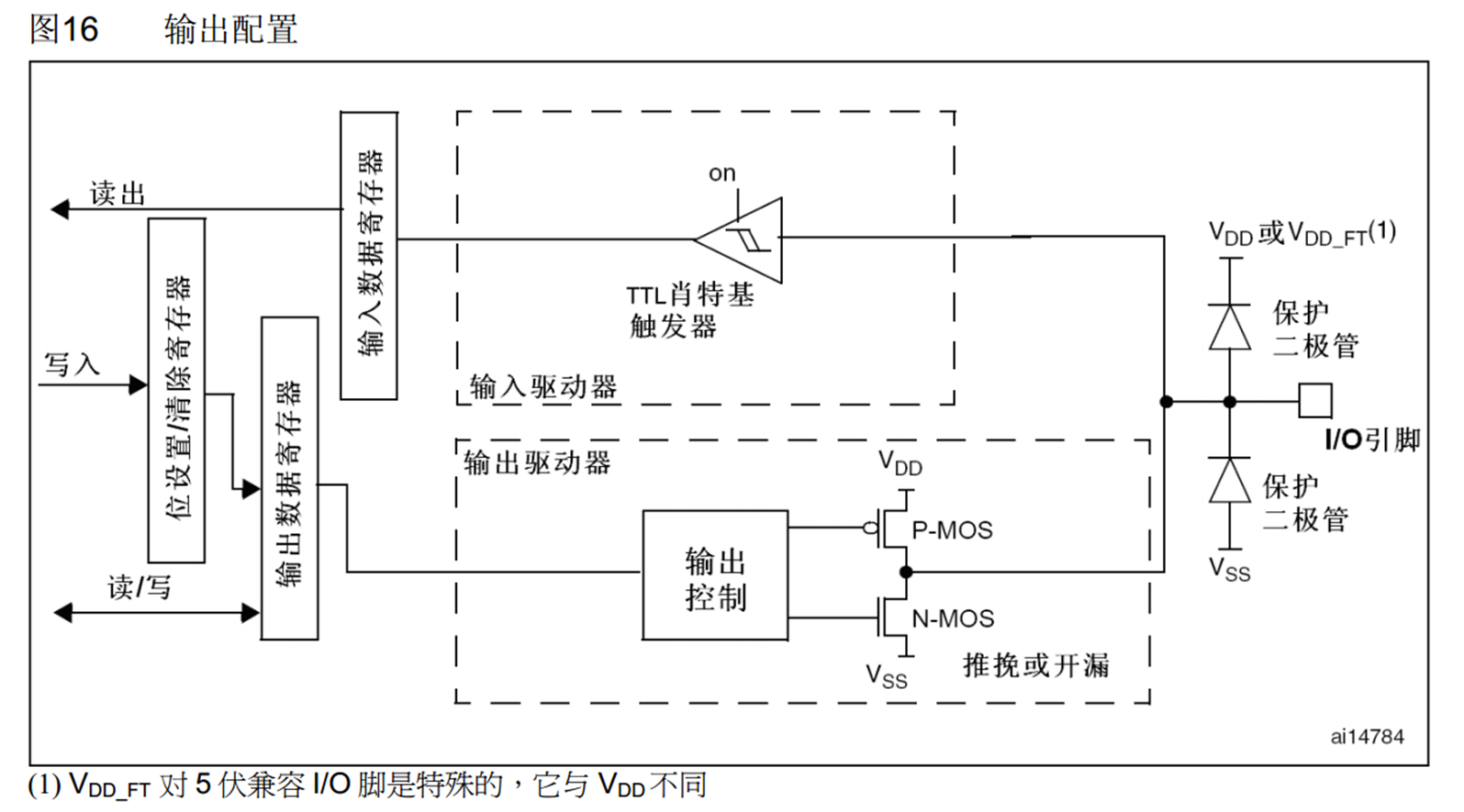

2.模拟输入

模拟输入时,不连接上拉电阻和下拉电阻。

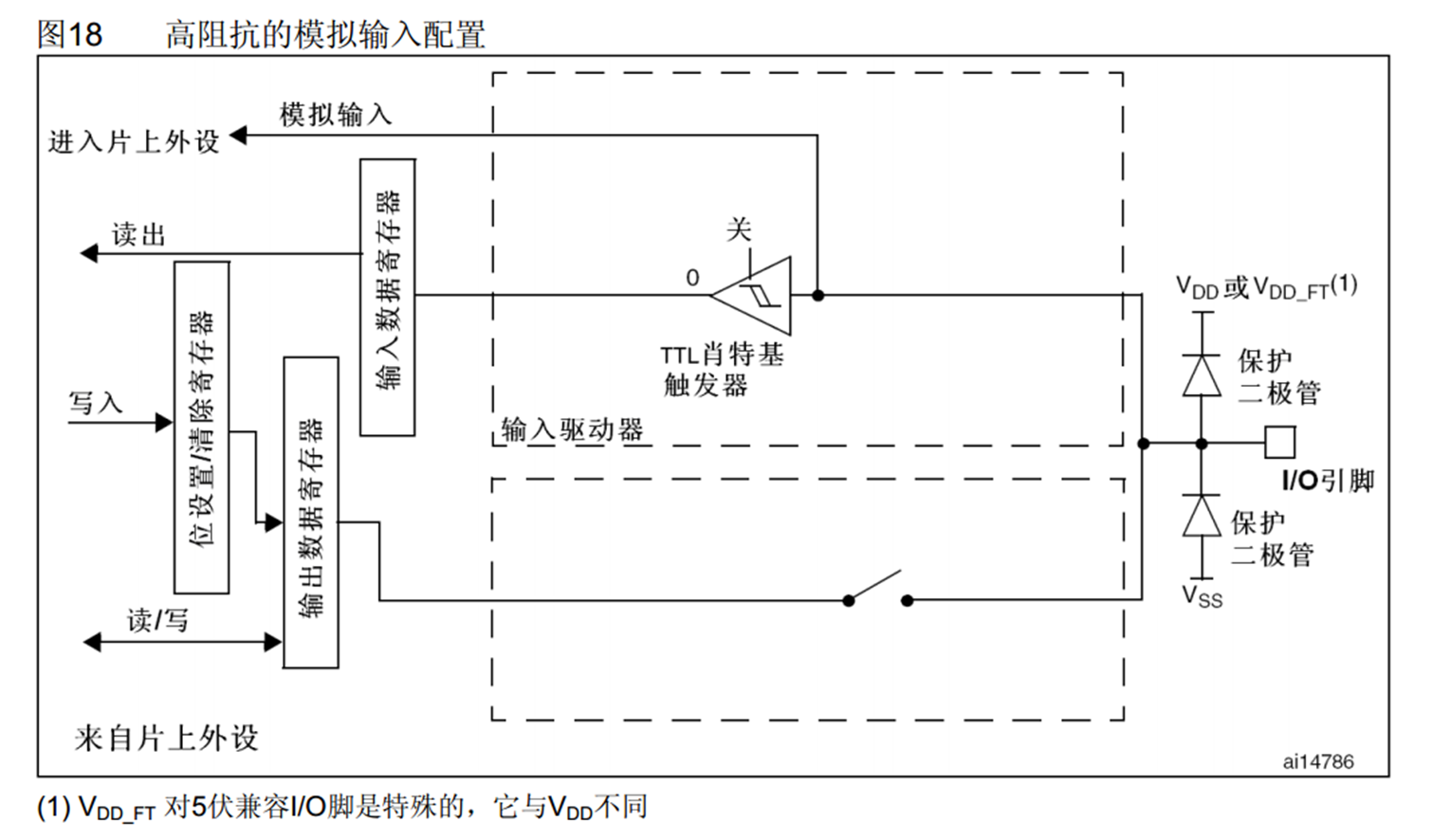

3.开漏/推挽输出

当P-MOS无效,N-MOS有效,就是开漏输出,这时候高电平为高阻态,这可以兼容不同的部件的高电平电压值,把高电平值交给连接的部件决定(上拉输入)。同时输出情况下,可以保持正常读的功能,感知输出值,但是输入情况下不能输出,可能因为防止输出高电平,输入低电平导致短路。

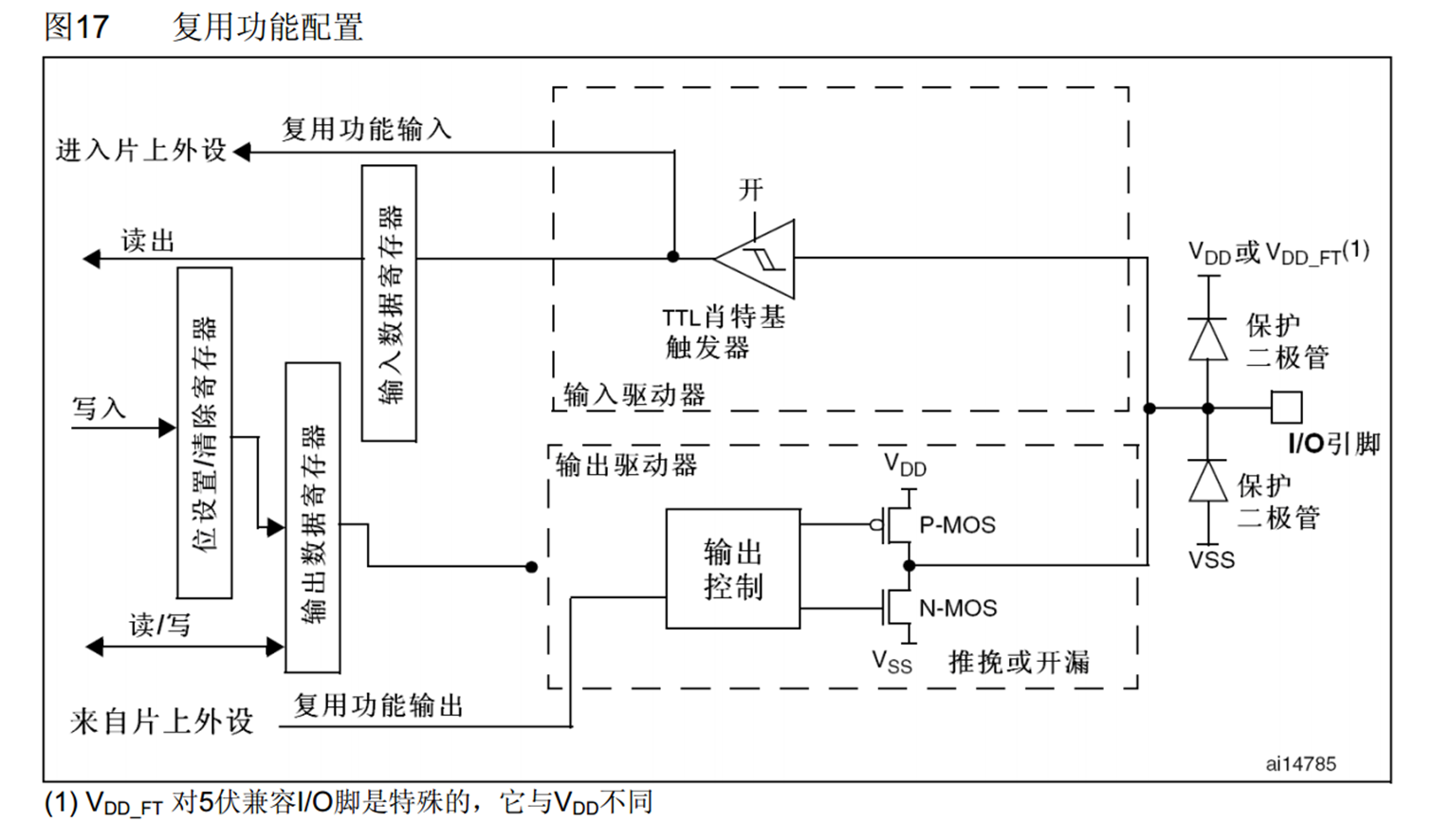

4.复用开漏/推挽输出

只不过复用的输出,引脚的电平是由片上外设所决定的。