【软考】计算机系统构成及硬件基础知识

文章目录

- 进制

- 码制

- 逻辑运算

- CPU的构成、CPU性能指标

- 多级存储、存储器分类、高速缓存Cache

- 总线

- 指令、寻址方式、RISC/CISC

- 流水线的概念、周期、计算公式

- 输入输出系统

- 校验码 (奇偶校验、CRC、海明码)

进制

二进制:0、1

八进制:0、1、2、3、4、5、6、7

十进制:0、1、2、3、4、5、6、7、8、9

十六进制:0、1、2、3、4、5、6、7、8、9、A(10)、B(11)、C(12)、D(13)、E(14)、F(15)

- 进制转换

- 十进制→ 其他进制

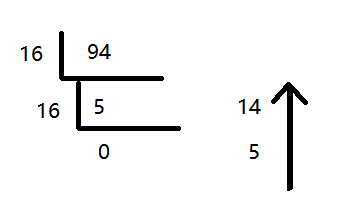

整数部分:除基取余法(短除法)(逆序)示例1:十进制25 → 二进制 25 ÷ 2 = 12 余 1 12 ÷ 2 = 6 余 0 6 ÷ 2 = 3 余 0 3 ÷ 2 = 1 余 1 1 ÷ 2 = 0 余 1 → 11001(二进制)示例2:十进制94 → 十六进制 94 ÷ 16 = 5 余 14(E) 5 ÷ 16 = 0 余 5 → 5E(十六进制)

小数部分:乘基取整法(顺序)示例:十进制25 → 二进制 0.625 × 2 = 1.25 → 取整1 0.25 × 2 = 0.5 → 取整0 0.5 × 2 = 1.0 → 取整1 → 0.101(二进制) - 其他进制→ 十进制(按权展开发)

1111(二进制)=1*2³+1*2²+1*2¹+1*2º=8+4+2+1=15 604.01(八进制)= 6*8²+0*8¹+4*8º+0*8的负一次方+1*8的负二次方=384+0+4+0+1/64=388+1/64 - 二进制 ↔ 八/十六进制

二进制 → 八进制:每3位分组(不足补0)

二进制 → 十六进制:每4位分组(不足补0)101 110 011 → 1*2²+0*2¹+1*2º 1*2²+1*2¹+0*2º 0*2²+1*2¹+1*2º → 563(八进制)1011 1001 → 1*2³+1*2¹+1*2º 1*2³+1*2º → 11 9 →B9(十六进制)

- 十进制→ 其他进制

码制

| 类型 | 表示规则 | 特点 | 数值1 | 数值-1 | 1+(-1) |

|---|---|---|---|---|---|

| 原码 | 符号位(0正1负)+绝对值 | 直观,但加减复杂 | 0000 0001 | 1000 0001 | 1000 0010(计算错误) |

| 反码 | 在原码的基础上,正数不变,负数符号位不变,数值位取反 | 过渡方案,已淘汰 | 0000 0001 | 1111 1110 | 1111 1111(计算错误) |

| 补码 | 在反码的基础上,正数不变,负数+1 | 统一加减法,现代计算机标准 | 0000 0001 | 1111 1111 | 0000 0000(正确!) |

| 移码 | 在补码的基础上,符号位取反 | 用于浮点数阶码 | 1000 0001 | 0111 1111 | 0000 0000 |

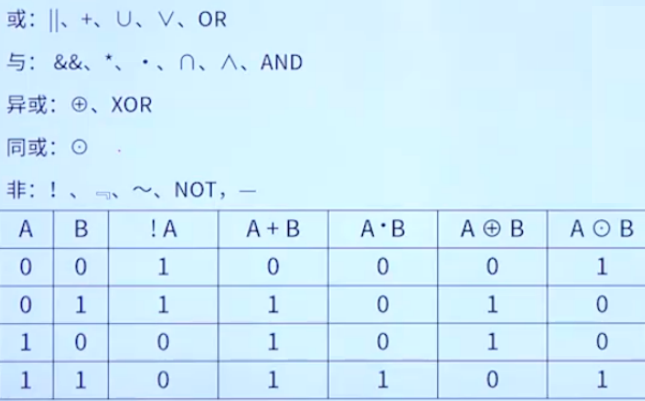

逻辑运算

备注:

1)0假1真

2)或:一真就真

3)与:全真才真

4)异或:相同为假,相异为真

5)同或:相同为真,相异为假

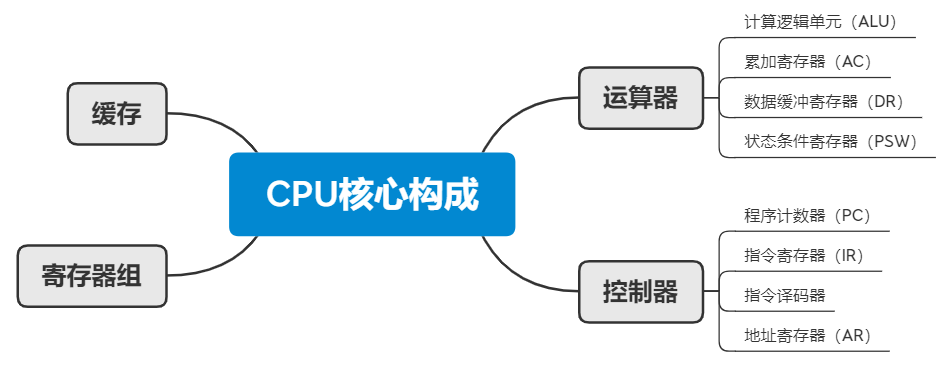

CPU的构成、CPU性能指标

- CPU核心构成模块

- CPU关键性能指标

-

基础指标

指标 定义与影响 典型值示例 主频 时钟频率(GHz,即10⁹ Hz),决定单核指令执行速度(需结合IPC) 3.6GHz(Intel i7) 核心数 物理核心数量,影响多线程并行能力 8核(AMD Ryzen) 字长 CPU一次处理的二进制位数(64位支持更大内存寻址) 64位 -

指令与缓存性能

- IPC(每周期指令数Instructions per Clock Cycle):表示 每个时钟周期内处理器可执行的指令数量,是衡量CPU性能的核心指标之一。数值越高,代表CPU的指令吞吐效率越高

- CPI(Cycles Per Instruction):为IPC的倒数,表示执行一条指令所需的平均时钟周期数,常用于分析指令执行效率。

- 缓存命中率:L1命中率需≥95%以避免主存访问延迟。

- 执行时间公式:

执行时间= (指令数)*CPI/主频

-

题目: 某CPU主频4.0GHz,执行一段程序包含2×10⁹条指令,平均CPI=1.5,求总执行时间?

解析: 执行时间=(2×10⁹×1.5)/(4×10⁹)=0.75s

备注: 1 kHz = 10^3 Hz,1 MHz = 10^6 Hz,1 GHz = 10^9 Hz

多级存储、存储器分类、高速缓存Cache

-

多级存储体系

现代计算机采用金字塔型多级存储结构,按速度、容量和成本分层设计:层级 类型 容量范围 访问速度 成本 典型实现技术 1 寄存器 <1KB 0.1ns 最高 SRAM(CPU内部) 2 高速缓存Cache L1:32KB

L2:256KB

L3:16MB1-12ns 高 SRAM(片内/片外) 3 主存储器 8GB-128GB 50-100ns 中等 DRAM(DDR4/DDR5) 4 外存储器 512GB-10TB 5-20ms 低 磁盘/SSD/NVMe 核心作用:通过层级互补平衡速度、容量与成本,如Cache减少CPU等待主存的延迟(时空局部性原理)

-

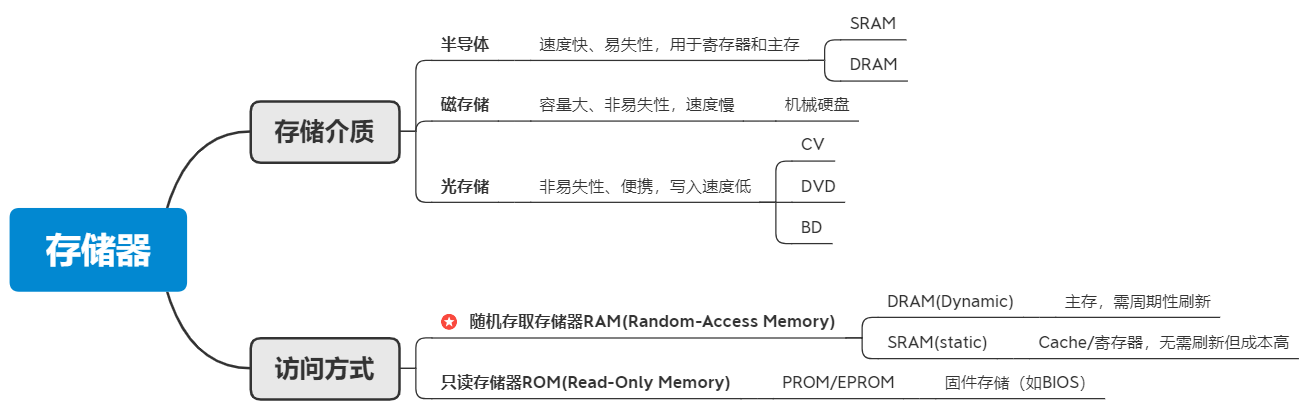

存储器分类与特性

-

Cache核心知识

映射方式 特点 适用场景 直接映射 主存块与Cache行——对应,冲突率高但硬件简单 低功耗嵌入式系统 全相联映射 主存块可存入任意Cache行,冲突率低但硬件成本高 小容量Cache 组相联映射 主存块映射到特定组内,平衡速度与成本 通用CPU (Intel/AMD) Cache命中率计算:

平均访问时间 = 命中率×Cache时间 + 失效率×(Cache时间+主存时间)

题目1: 某系统Cache命中率95%,主存访问时间100ns,Cache访问时间5ns,求平均访问时间。

解析: 平均时间=0.95×5ns+(1−0.95)×(5ns+100ns)=4.75+5.25=10ns题目2: 某计算机主存按字节编址,地址范围从A5000H到DCFFFH,求存储容量(单位KB)。

解析:

- 计算地址差值:DCFFFH - A5000H + 1 = 38000H(H 表示十六进制)

- 转换为十进制:38000H = 3×16⁴ + 8×16³ = 229,376B

- 转换为KB:229,376B ÷ 1024 = 224KB

总线

-

总线定义与功能

总线是计算机系统中各部件间传输数据的公共通道,包括数据、地址和控制信号的传递。核心功能包括:- 数据总线(Data Bus): 传输操作数、指令和结果(宽度决定单次传输数据量)

- 地址总线(Address Bus): 指定内存或外设的访问位置(宽度决定寻址空间)

- 控制总线(Control Bus): 传递时序、中断请求等控制信号(如读写控制、总线仲裁)

-

总线分类与特性

指标 定义与计算公式 示例值 总线带宽 单位时间传输数据量:带宽=总线频率×总线位宽÷8(单位:MB/s) PCle 4.0×16: 32GB/s 总线位宽 数据总线宽度(如32位总线单次传输4B数据) 64位 总线时钟 同步总线的时钟频率 (如DDR5总线频率可达6400MHz) 100MHz

题目1: 若内存容量为4GB,字长为32位,则地址总线宽度为( )

解析: 4GB = 2^32B →地址总线需32位,但字长为32位(32bit÷8=4B),实际寻址单元数=4GB/4B=1G=2^30 → 地址线30位

备注: 1GB=2^10(即1024)MB = 2^20KB = 2^30B(字节);1B(字节)=8bit(位)

题目2: 某总线频率为100MHz,位宽64位,求总线带宽(单位GB/s)。

解析: 带宽=(100×106×64)÷8÷109 =0.8GB/s

备注: 1MHz=10^6Hz

题目3: 某系统地址总线宽度为32位,数据总线宽度为64位,求最大可寻址空间(单位GB)

解析: 地址总线宽度决定寻址能力:地址总线宽度为32位,可生成的唯一地址数量为2^32个,每个地址对应1字节(按字节寻址),总容量为2^32B=4GB(1GB=2^30B)

备注: 数据总线宽度不影响寻址空间。数据总线宽度为 64位(即每次传输 8 字节),仅决定单次数据传输量,与寻址空间无关。

指令、寻址方式、RISC/CISC

-

RISC与CISC对比

RISC(Reduced Instruction Set Computer) 一种微处理器设计理念,其核心在于采用精简且高频使用的指令集,通过减少指令类型和复杂度提升执行效率。

CISC(Complex Instruction Set Computer) 采用复杂多样的指令集,支持直接内存操作,但指令执行时间和格式差异较大。维度 RISC CISC 指令数量 少 (数十至百余条) 多(200-300条) 指令格式 固定长度,种类少 可变长度,种类多 执行周期 单周期指令为主 多周期指令占比高 典型应用 ARM架构、移动设备 x86架构、传统PC -

寻址方式详解

寻址方式 定义 特点 公式 比喻 立即寻址 操作数直接包含在指令中 执行速度快,但操作数不可修改。 EA=指令中的立即数 直接给你铅笔盒! 直接寻址 指令中直接给出操作数的内存地址 形式地址=有效地址,需访问内存 EA=地址码字段 告诉你铅笔盒在书包的第三层! 变址寻址 变址寄存器内容+形式地址=有效地址 EA= (Rx) + A 从大树(变址寄存器)出发,向前走5步,左转再走3步 基址寻址 基址寄存器内容+位移量=有效地址 EA = (Rb) + D 从教室门(基址)向右数第4个座位! 相对寻址 程序计数器(PC)当前值+位移量=有效地址(用于跳转指令)。 EA = (PC) + D 从你现在站的位置,向前跳3格!

题目: 变址寻址与基址寻址的主要区别是?

答案: 变址寻址以变址寄存器为基准,用于数组遍历;基址寻址以基址寄存器为基准,用于动态地址分配。

流水线的概念、周期、计算公式

-

流水线基本概念

定义:流水线是一种通过将指令处理划分为多个阶段,使不同指令的各阶段重叠执行的技术,以提高处理器效率。

核心特点:

1、各阶段并行处理不同指令的对应部分

2、硬件资源利用率高,指令平均执行速度提升 -

流水线周期

概念:流水线周期(Pipeline Cycle Time)是流水线中执行时间最长的阶段的耗时。

示例:若某流水线分为取指(2ns)、译码(3ns)、执行(5ns)、写回(2ns)四个阶段,则流水线周期为5ns(最长阶段为"执行")。 -

流水线执行时间计算

理论公式:T理论=一条指令完整执行时间+(指令数量-1)×流水线周期 -

流水线性能指标

指标 公式 说明 吞吐率 TP=n÷T(指令数÷执行时间) 单位时间完成的指令数 最大吞吐率 TPmax =1/流水线周期 流水线周期倒数 加速比 S=T年流水线÷T流水线 非流水线时间与流水线时间比值

题目: 某流水线分为3个阶段,耗时分别为2ns、4ns、3ns。执行50条指令时,理论执行时间和吞吐率分别是多少?

解析:

流水线周期=4ns(最长阶段)

理论执行时间=(2+4+3)+(50-1)×4=9+196=205ns

吞吐率=50/205≈0.244条/ns

输入输出系统

- 基本概念与组成

定义:输入输出系统(I/O系统)负责计算机与外部设备(如键盘、显示器、磁盘等)之间的数据传输与控制。

核心组件:

(1)I/O接口: 连接CPU与外部设备的桥梁,实现信号转换与协议匹配(如USB、SATA接口)。

(2)**I/O控制器:**管理设备与主机的通信(如中断控制器、DMA控制器)。

(3)数据缓冲寄存器(DR): 暂存待传输的数据,解决CPU与设备速度不匹配问题4。 - I/O控制方式

方式 原理 适用场景 程序查询 CPU主动轮询设备状态,效率低 低速设备 (如键盘) 中断驱动 设备完成操作后触发中断, CPU暂停当前任务处理中断 中速设备 (如打印机) DMA (直接存储器访问)

Direct Memory AccessDMA控制器接管数据传输,无需CPU参与, 直接访问内存 高速设备(如磁盘、网络卡)

题目1: DMA传输过程中,CPU是否需要全程参与?为什么?

答案: 不需要。DMA控制器直接接管总线,独立完成设备与内存的数据传输,仅在传输开始和结束时通知CPU。

题目2: 某磁盘采用DMA方式传输数据,单次传输块大小为4KB,传输速率为200MB/S。若CPU处理一次中断耗时2μs,求传输10块数据的总时间(忽略寻道时间)。

解析:

单块传输时间 = 4KB÷200MB/s = (4×1024)÷(200×10^6)≈0.00002048s = 20.48μs

总时间=10×20.48μs + 2μs×10 = 204.8μs + 20μs = 224.8μs

答案: 224.8μs

校验码 (奇偶校验、CRC、海明码)

-

奇偶校验码

定义: 通过增加1位校验位,使数据中"1"的个数为奇数(奇校验)或偶数(偶校验)。

特点:

(1)码距为2,只能检测奇数位错误,无法检测偶数位错误13。

(2) 无纠错能力,适用于低速数据传输(如串口通信)58。

示例: 数据1011采用奇校验,校验位为0,完整编码为10110。 -

CRC循环冗余校验码 (Cyclic Redundancy Check)

原理: 利用生成多项式生成校验码,通过模2除法(异或运算)检测错误。

特点:

(1)可检测连续多位错误,广泛应用于网络通信和存储系统(如以太网、磁盘)。

(2)校验位长度由生成多项式决定(如CRC-32使用32位校验码)。

计算步骤:

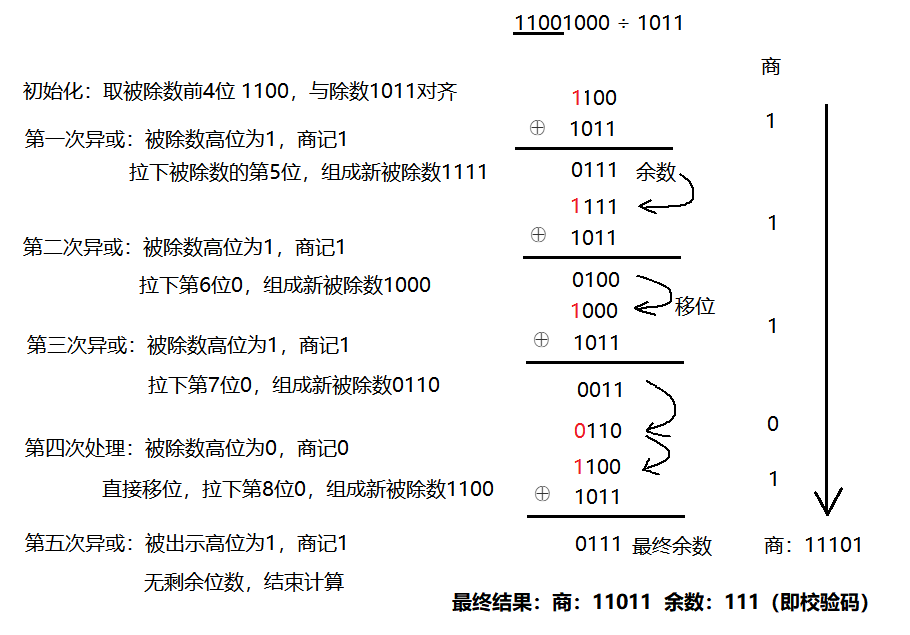

①数据末尾补0(0的数量=生成多项式位数-1)→②模2除法计算余数→③余数作为校验码附加到数据末尾 。模2除法步骤流程

1. 对齐高位:将被除数高位与除数最高位对齐,若被除数当前高位为1,则商记为1,并执行异或运算;若为0,商记为0,直接移位。

2. 异或运算:用除数与当前被除数的高位部分进行异或(相同为0,不同为1),得到中间余数。

3. 移位并拼接:将余数左移一位,并拉取下一位被除数,组成新的被除数片段。

4.重复直到处理完所有位:重复上述步骤,直到所有被除数位都被处理完毕,最终余数即为结果。 -

海明码

原理: 通过增加多个校验位,扩大码距以实现单比特纠错、双比特检错, 校验位放置在2的幂次位置 (1,2,4,8…) 。

公式: 校验位数k 满足2^k≥n+k+1(n 为数据位数)。

示例: 数据01101001需4位校验位(k=4),海明码最终覆盖二进制位置1,2,4,8的奇偶性。

题目1: 设计一个4位数据的奇偶校验码生成流程(偶校验)。

答案: ①统计数据中"1"的个数→②若为偶数,校验位为0;若为奇数,校验位为1→③附加校验位到数据末尾。

题目2: 使用生成多项式G(X)=X3+X+1(对应二进制1011),计算数据11001的CRC校验码。

解析:

①数据补4-1=3个0 → 11001000

②模2除法:11001000 ÷ 1011 → 余数111

答案: CRC校验码为11001111 (数据+余数111)。

题目3: 海明码的码距是多少?为什么能纠正单比特错误?

答案: 码距为3。单比特错误会改变多个校验位的奇偶性,通过校验位组合定位错误位置。