AXI 协议补充(二)

axi协议存在slave 和master 之间的数据交互,在ahb ,axi-stream 高速接口 ,叠加大位宽代码逻辑中,往往有时序问题,valid 和ready 的组合电路中的问题引发的时序问题较多。

本文根据axi 协议和现有解决反压造成的时序问题的方法做一个详细的科普。

1. 解决时序问题的方法:

1.增加 register slice / pipe / 打拍

在将打拍时,需要注意哪些场景下,简单的打拍不能完全解决,需要熟悉模块间的信号交互关系,决定是否需要额外逻辑。

举几个例子:

1. 在asic 设计时,要求每个module 输出信号必须打拍,这就是最常见的打拍优化时序的方法

2. 对于axi 协议类型 某一个通道内信号不是简单的单向的,必须 打拍+额外逻辑 保证原时序对齐

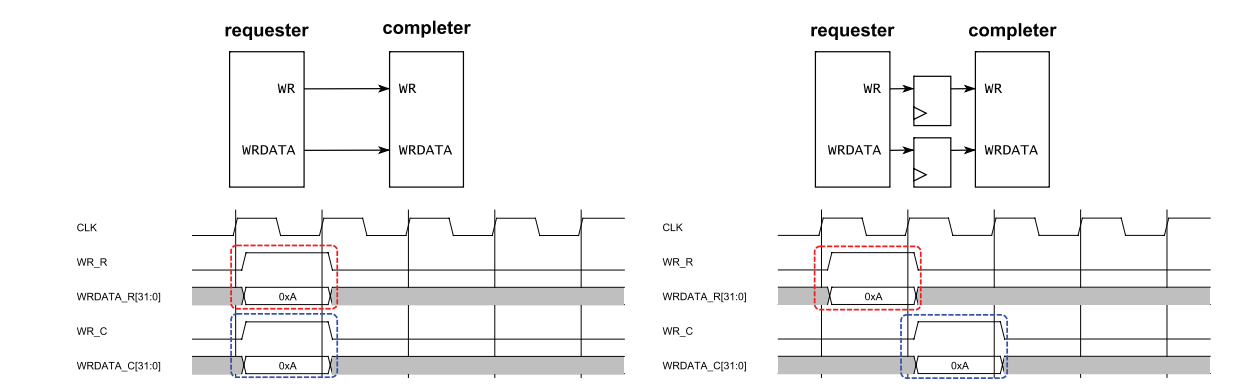

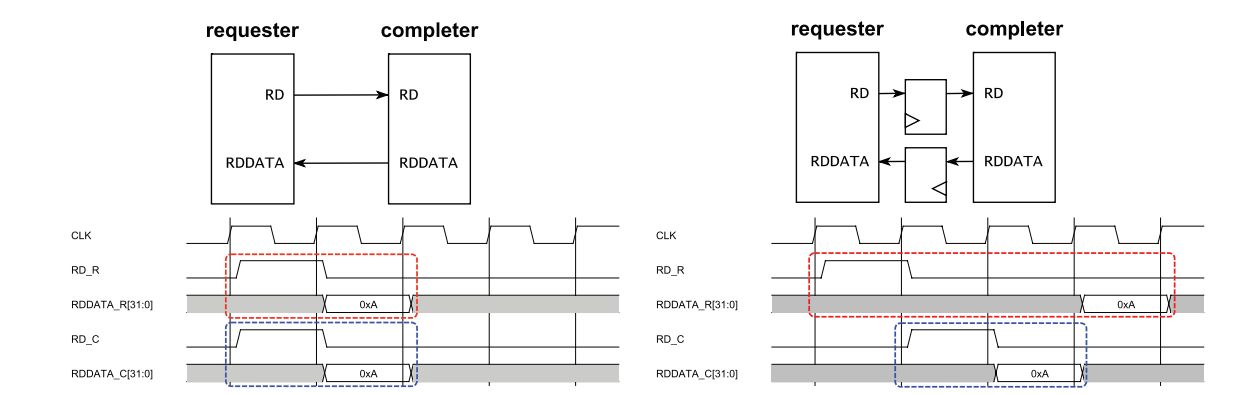

如下图 ,对于写发向,wr 和wrdate 方向相同,打拍后到下级模块的时序与打拍前一致。

但是对于读方向,rd 和rdata 的方向不相同,打拍后的读时序出现了偏差,rdata 没有在rd的下一拍返回。

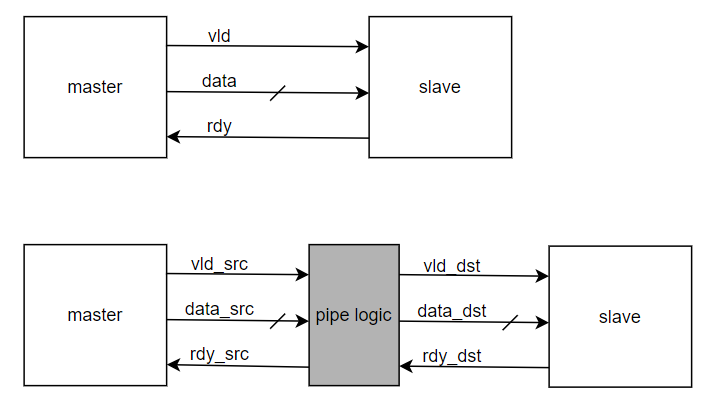

对于aix 存在valid 和ready 握手机制的协议,如何实现打拍呢?

按照时序可能存在的点,将打拍分为 forward registed ,backward registed 和 forward-backward registed 三类。

forward registed(对vld 和data 打拍) :

module forward_logic(input wire clk,input wire rst_n, input wire [7:0] data_src,input wire vld_src,output wire rdy_src,output reg [7:0] data_dst,output reg vld_dst,