高速连接器设计的真相

在高速连接器设计领域,有两种相反的想法。对于某些人来说,如果你简单地将塑料和金属碎片放在一起,最终你会得到信号传输。这个过程非常简单。另一方面,有一种观点认为,可靠的连接器设计需要对电磁理论有深入的理解,而这种智慧只有巫师和巫师才具备。就像生活中的几乎所有事情一样,真相介于两者之间。在本文中,我将尝试揭开高速连接器设计的一些概念的神秘面纱。

对立的观点和考虑

让我先说,“不,事情没那么简单。如果是这样,公司就不会有专门的团队专门负责连接器设计。仅在工程方面,这些团队就由信号完整性 (SI) 工程师、机械工程师和制造工程师组成。如果 SI 工程师谈论阻抗、串扰和插入损耗(有趣的东西),机械工程师谈论法向力或配接周期(无聊的东西),制造工程师谈论工具或成型(更无聊)。我什至没有考虑业务方面,因为工程师通常不太关心成本:“谁在乎它是否太贵?这是一个美丽的设计!如您所见,高速连接器设计是一项多学科的工作,并不像将金属和塑料放在一起那么简单。

相关资源

另一方面,一些 SI 工程师使连接器设计的电气部分听起来像魔法。当一些波浪线出现问题时,我们 SI 向导可以让它们上升、下降、出现和消失!这可能需要一些经验和知识,但肯定不是魔法。在本文中,我将探讨我们在连接器设计的 SI 方面所做的工作。

高速连接器设计的电气侧

在处理高速设计时,必须解决几个不同的参数。这些因素包括串扰、损耗、阻抗、共模、模式转换、耦合等,对于首先考虑什么,以及什么或多或少相关,永远不会达成一致。归根结底,它归结为客户的需求。在这里,我将重点介绍在设计高速连接器时我花费大部分时间的两个方面:差分阻抗(回波损耗)和谐振(插入损耗)。

因为高速连接器设计并非易事,我们可以理解为什么大多数公司都非常保护他们的设计。很难说服任何参与该市场的组织分享他们的知识产权,但我们可以收集一些关于相关内容的见解,并通过一个简单的委员会来解决问题。例如,在顶部接地层和底部接地层之间具有共面接地和一些接地拼接通孔的差分微带是说明这些设计原理的良好测试工具。

阻抗

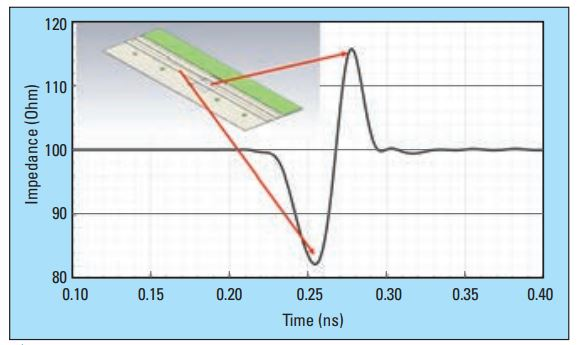

如果截面轮廓沿传播方向不变,则差分阻抗也不会改变。然而,有时接地层会在信号走线下方被切开,从而使阻抗升高。或者拼接过孔离信号走线太近,或者两条信号走线靠得太近,从而降低了阻抗。图 1 说明了这些现象。

图 1 差分微带走线的差分阻抗曲线。阻抗在接地层切割的地方上升,在走线较宽(更近)的地方下降。

这就是我们在设计连接器时调整阻抗的方法:如果我们想降低阻抗,我们添加金属或使走线(或接地)靠得更近。如果我们想让它上升,我们去除金属或拉动痕迹或进一步接地。在这里显示的示例中,事情会很简单,因为我们只需尝试使横截面恒定即可。在实际的连接器设计中,事情会涉及更多。我们将调整差分阻抗,直到达到尽可能平坦的曲线。最近对阻抗的计算方式以及单端模式和差分模式之间的差异进行了详细分析。1

共振

一旦阻抗达到最佳状态,我们就可以将注意力转向谐振。它们将出现在插入损耗曲线中,并且通常会延续到回波损耗和串扰中。有两种类型的谐振需要解决:一种是由信号路径中的短截线引起的,另一种是由返回路径或接地结构引起的。

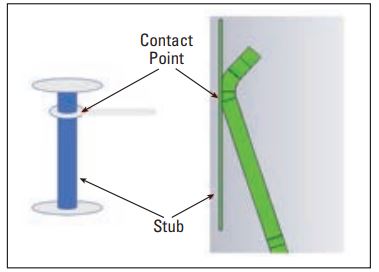

第一个已经由业内的几位专家解释过2, 3电路板中有过孔存根。在连接器设计中,这种现象也会发生,并且与两个配接引脚之间的擦拭有关。尽管几何形状在机械上不同,但从电气角度来看它是相同的:如果允许信号在触点和擦除或过孔末端的短路之间传播,它将产生与该短截线长度成正比的谐振。图 2 说明了过孔短截线和连接器配接短截线之间的并行。在理想的电气设计中,连接器中不允许有擦拭,因此不存在短截线。但从机械角度来看,这是不可能的,必须在电气性能和机械可靠性之间实现折衷。擦除时间越长,连接器的谐振频率就越低。这是 1 GHz 连接器和 40 GHz 连接器之间的一个区别:40 GHz 连接器不能承受长时间的擦除,就像 40 GHz 性能的电路板必须包括背钻以移除过孔短线一样。

图 2 过孔和连接器配接点的短截线效应。

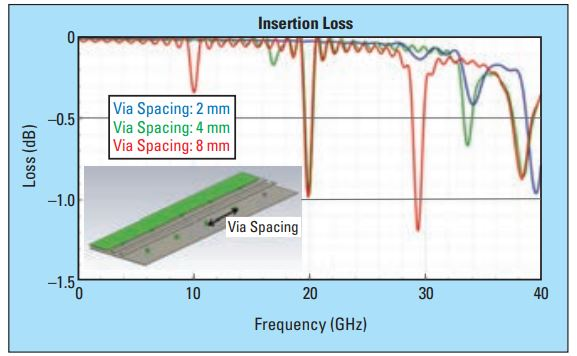

即使信号路径完美,仍可能存在共振。返回路径是这里的游戏名称。拼接通孔之间的距离将决定平面到平面结构中发生谐振的频率。这是设计在 1 GHz 下工作的连接器与在 40 GHz 下工作的连接器时的另一个区别:连接器应该工作的频率越高,相关的返回路径结构必须越短。

例如,如果连接器有接地引脚,则必须将它们缝合成,以使谐振超过所需的最小频率。我们再次使用 microstrip 示例来说明这个概念。图 3 显示了这种现象。拼接过孔越近,顶部和底部接地平面腔的谐振频率就越高。

图 3 插入损耗与通孔空间的关系。

现在人们可能很容易相信一切都很清楚。没那么快......请注意,在图 3 中,8 mm 过孔间距示例的谐振频率是 10 GHz 的倍数,但当您查看 4 mm 过孔间距示例时,不同频率下也有不同的组合。

例如,在 17 GHz 和 34 GHz 处存在一些问题。原因是拼接过孔之间的距离可以沿着顶部接地条的方向测量(就像我们正在做的那样),也可以沿着顶部接地条测量。在某些情况下,后者可能是主导效应。甚至两者的组合也可能是导致接地平面腔谐振的原因。

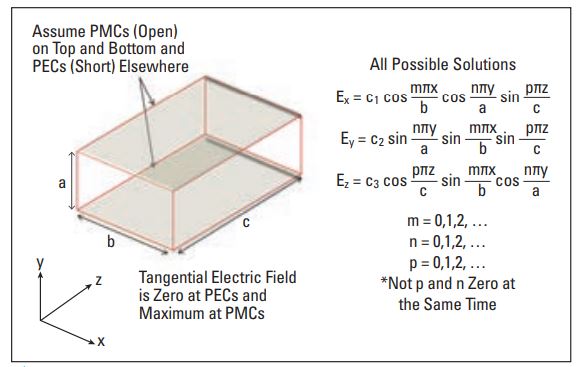

请记住,这是一个非常简单的 microstrip 迹线。在实际的连接器设计中,事情并不那么简单。确定问题所在位置的一种方法是查看谐振频率下的场。我和我的同事过去曾对这个问题进行了更深入的研究。4图 4 突出显示了这种方法背后的概念。

图 4 用于谐振腔问题的基本电磁理论。

从本质上讲,我们将注意力转向共振原理,并提出了一个问题,“它们起源于哪里?从基本电磁理论来看,当有一个空腔并且电磁场被困在该空腔内时,就会发生共振。请注意,模式(可能的解决方案)可以是 x、y 或 z 的函数,主导模式将取决于型腔尺寸。同样,在我们的微带走线示例中,顶平面到底平面腔的谐振频率可以是 x 方向、y 方向的通孔间距的函数,也可以是两者的组合,而且并不总是很明显,尤其是在设计连接器时,问题可能就在那里。

为了扩展基本理论,我们用类似连接器的几何结构代替理想化的空腔。这是通过使用特征模求解器来识别可能发生谐振的频率来实现的。本征模态解不仅比全频扫描快得多,而且一旦有解可用,场图也可用。这使用户能够看到共振最强的区域,帮助工程师从理论和基本角度解决问题,而不是试错。

通过移除信号引脚,仅用接地结构获得本征模解,从而允许将接地结构视为谐振腔,如图 4 中描述的基本腔。除了提供可能的谐振频率列表外,特征求解器还提供与每种谐振模式相关的 Q 因子。Q 因子表示如果兴奋,模式会产生多强的共鸣。Q 值越高,该模式的谐振就越强。

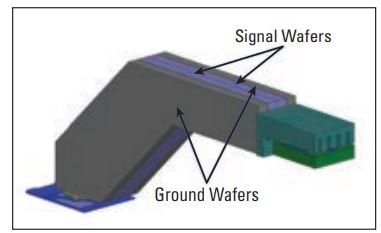

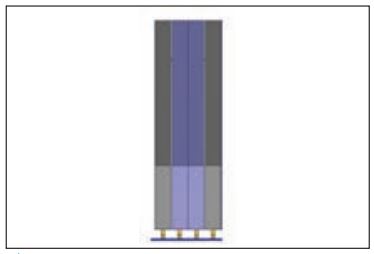

我们模拟了高速连接器中的常见几何形状。这种几何形状由四个晶片(嵌入塑料中的金属引脚)组成。构成差分对的内部信号晶片夹在两个接地晶片之间,如图 5 所示。

图 5 高速连接器示例。

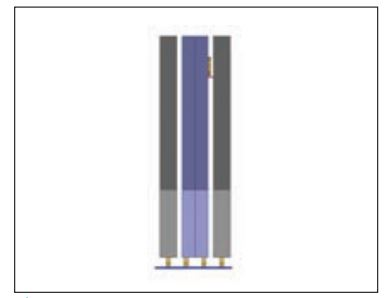

在第一种结构中,信号晶片和接地晶片之间有一个气隙,如图 6 所示。这称为间隙结构 (GS)。

图 6 横截面,带接地信号 (GS) 间隙。

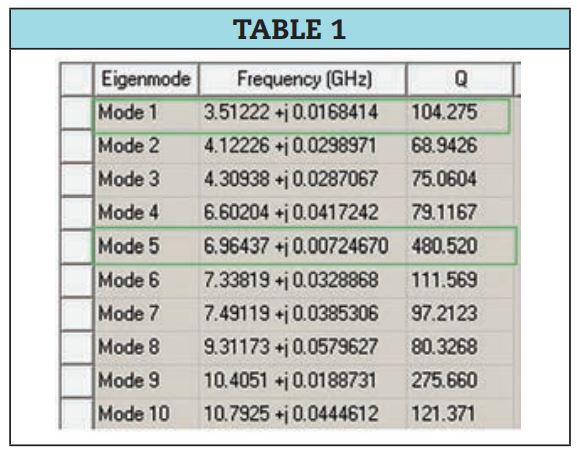

使用特征模态求解器分析了该结构。表 1 总结了谐振频率及其相关的 Q 值。

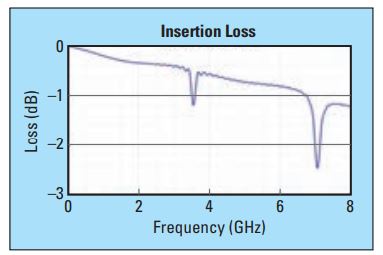

同样的几何结构也在频域中通过全频扫描进行了分析。一般来说,在整个感兴趣的频率范围内进行完全扫描至少比特征模态解慢一个数量级。该结构的相应插入损耗曲线如图 7 所示。

图 7 GS Gap 结构的插入损耗图,如图 6 所示。

请注意,图 7 中的谐振与表 1 中的模式 1 和 5 一致。特征模解决定了给定结构可能谐振的所有频率,但并非所有模式都会被差分信号激励。对于差分特征模态不明显的情况,用户可以查看特征模态解的完整三维场分布。

与其花费计算时间进行频率扫描,不如查看特征模态场图来研究哪些特征模态相关。这种方法至少比传统的全扫描快一个数量级。通过检查场,用户可以辨别哪些场是由差分信号生成的。

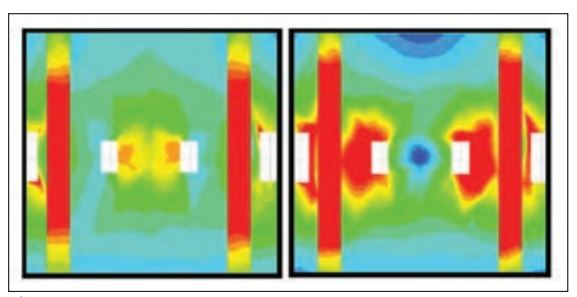

图 8 显示了特征模态场图,这些图确定了差分能量(左)和不太可能被差分能量激发的特征模场(右)可能发生的共振。通常,第一个特征模态(本例中为 3.5 GHz)是与差模相关的特征模态,这是主要关注点。此外,高次谐波(例如 6.9 GHz 的模式 5)通常也相关。

图 8 电场分布显示了由差分能量激发的模式(左)和不由差分能量激发的模式(右)。

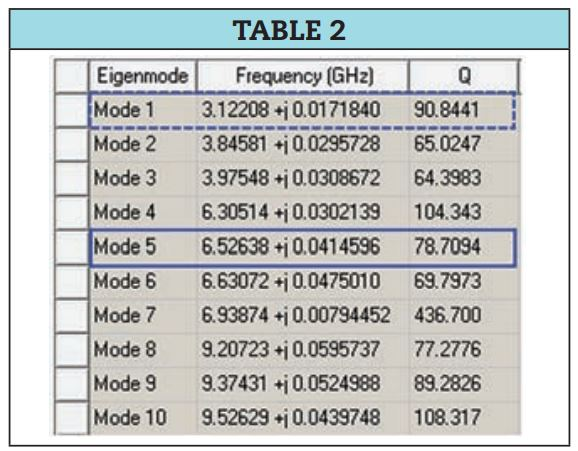

回到 GS Gap 结构,可以通过降低谐振的强度来提高性能。换句话说,可以调整几何结构,使谐振模式产生较低的 Q 因子。使用此几何形状实现此目的的一种方法是减小 GS 气隙,如图 9 所示。特征求解器的结果总结在表 2 中。

图 9 GS 间隙减小的横截面。

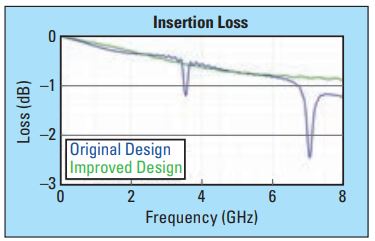

与表 1 和表 2 中的结果相比,Q 因子的降低是显而易见的,特别是对于模式 1 和 5。因此,减小的 GS Gap 几何图形有望获得更好的性能。事实上,当仿真全频率扫描时,插入损耗曲线显示出显著改善,如图 10 所示。

图 10 Q 因子的降低转化为更好的插入损耗曲线。

最后,正如我们之前看到的,在连接器中添加或移除金属会对阻抗产生影响。更改晶圆的位置也会影响阻抗。在大多数情况下,设计人员在达到最佳电气性能之前必须重新审视阻抗调谐。

结论

在理想的 SI 世界中,我们只需调整阻抗,在我们认为合适的地方添加更多接地连接,然后就收工了。但是,我们不能简单地忽视连接器周围的一切。通常,我们会在 SI、机械和制造之间来回切换。在每一步中,我们确保至少阻抗和插入损耗按预期运行。而且我完全清楚,我什至没有谈论所有其他可能发挥作用的 SI 指标,例如共模、串扰、模式转换/偏移等。

总而言之:不,高速连接器设计不仅仅是将塑料和金属缝合在一起。它也不是魔法。这确实需要一些经验和知识,但有些事情可以用简单的术语来解释。还有一些人更先进一些。