总线-AXI

是什么?

- AXI(Advanced eXtensible Interface)是片内总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分

为什么?

-

SoC集成电路设计中集成的组件数量迅速增长,例如处理器、存储器、外设以及各种类型的IP核。

-

要一个高效、灵活的总线协议 管理SoC集成电路组件间的通信

-

AXI协议提供了诸如突发传输、未排序传输、支持多并发传输等先进特性

-

AXI协议使用分离的地址/控制和数据阶段,允许在不牺牲性能的前提下实现更好的数据流控制

怎么做?

核心本质

- 就是一个片内总线协议

接口应用

- AXI4中的限制是最多256个数据传输的突发事务。AXI4-Lite只允许每个事务进行1个数据传输

![![[Pasted image 20250216153109.png]]](https://i-blog.csdnimg.cn/direct/3f06fc372cd449a0b548c5df88471e06.png)

三种总线

AXI4:(For high-performance memory-mapped requirements. AXI4-full)

- 主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

![![[Pasted image 20250216152009.png]]](https://i-blog.csdnimg.cn/direct/e277c9b8f2d8476faacfd582a0107cc7.png)

![![[Pasted image 20250216165855.png]]](https://i-blog.csdnimg.cn/direct/f45150aed4b94dd499504af4aa8d3fbe.png)

![![[Pasted image 20250216170002.png]]](https://i-blog.csdnimg.cn/direct/771dfe5c25d5413284098b13a08b1283.png)

![![[Pasted image 20250216170221.png]]](https://i-blog.csdnimg.cn/direct/e46e82a34aac4b968cddd2127c69f625.png)

AXI4-Lite:(For simple, low-throughput memory-mapped communication )

- 是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data)

- 面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

![![[Pasted image 20250216151936.png]]](https://i-blog.csdnimg.cn/direct/9a8fdc38655a4b04a3cd455cce2477a8.png)

三种接口

![![[Pasted image 20250216165403.png]]](https://i-blog.csdnimg.cn/direct/62ef65b6dd1b48f29c820314ea998dc6.png)

- AXI-GP接口(4个) :是通用的AXI接口,包括两个32位主设备接口和两个32位从设备接口,用过改接口可以访问PS中的片内外设。

- AXI-HP接口(4个):是高性能/带宽的标准的接口, PL模块作为主设备连接(从下图中箭头可以看出)。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

- AXI-ACP接口(1个):是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设, PS端是Slave接口。

ZYNQ中AXI-Stream

-

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种

-

AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接

-

AXI-DMA:AXI-HP<---->AXI-Stream

-

AXI-FIFO-MM2S:AXI-GP<----->AXI-Stream

-

AXI-DataMover:AXI-HP<---->AXI-Stream,完全由PL控制的,PS是完全被动的

-

AXI-VDMA:AXI-HP<---->AXI-Stream,专门针对视频、图像等二维数据的

-

AXI-CDMA ,由PL完成的将数据从内存的一个位置搬移到另一个位置,无需CPU来插手

![![[Pasted image 20250216165803.png]]](https://i-blog.csdnimg.cn/direct/b37bf459028247dfaefd5ce5dd2f04a3.png)

![![[Pasted image 20250216170443.png]]](https://i-blog.csdnimg.cn/direct/fe4d5a50e7f4472f9f6f3875d3f7d48e.png)

![![[Pasted image 20250216170415.png]]](https://i-blog.csdnimg.cn/direct/bdf2ab935f594e6db4dd4919fe5971c0.png)

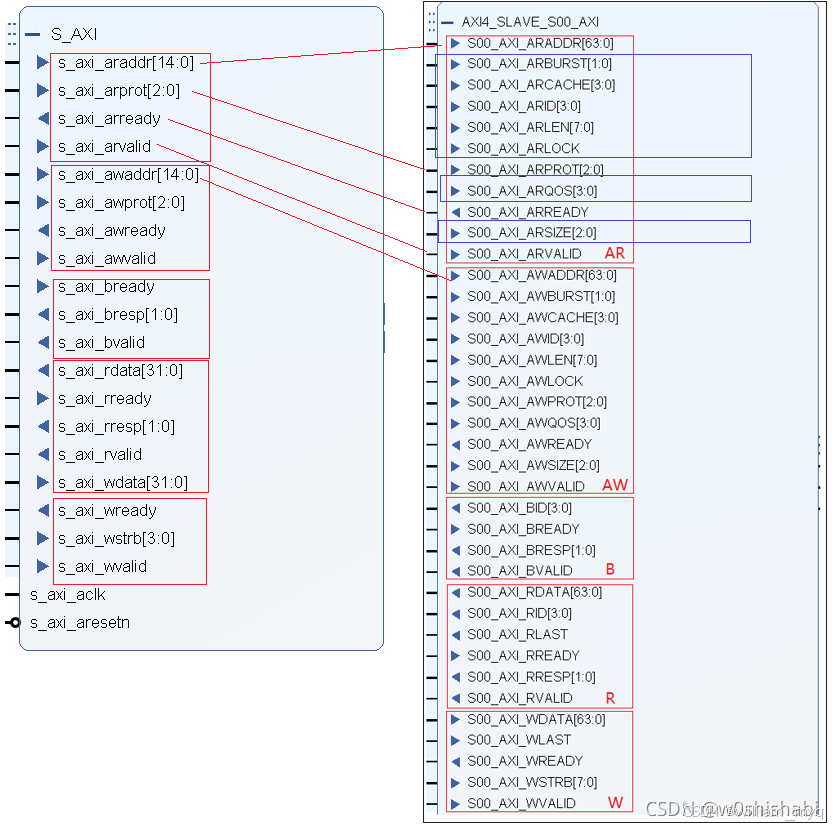

五种通道与信号

- 读地址通道(Read Address Channel)

- 写地址通道(Write Address Channel)

- 读数据通道(Read Data Channel)

- 写数据通道(Write Data Channel)

- 写响应通道(Write Response Channel)

![![[Pasted image 20250216153439.png]]](https://i-blog.csdnimg.cn/direct/02bd4ab2181d4cd384838cd4361d8ef2.png)

- ARADDR, AWADDR: 读地址 写地址

- ARPROT, AWPROT: 读保护类型 写保护类型

- WDATA, RDATA: 写数据 读数据

- ARVALID, AWVALID, WVALID: 读地址有效 写地址有效 写数据有效

- ARREADY, AWREADY, WREADY: 读地址就绪 写地址就绪 写数据就绪

- BRESP, RRESP: 写响应 读响应

- WSTRB 写选通(strobe)。这个信号指示内存中要更新的字节位置。写数据总线的每8位都有一个写选通。因此,WSTRB[n]对应于WDATA[(8 × n) + 7:(8 × n)],即每一位选通自己对应的Byte

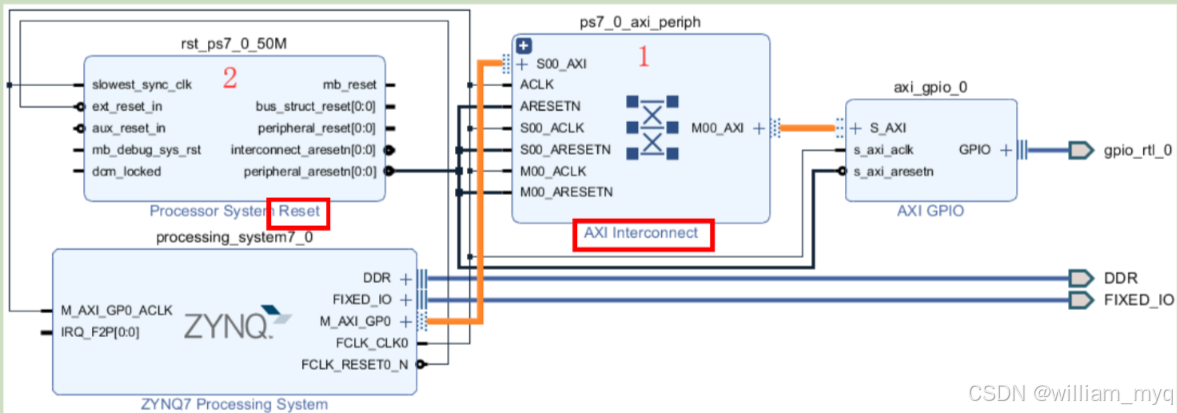

连接

- 单个AXI主(master)从(slave)之间的接口

- 多个Master和Slave之间的内存映射可以通过Xilinx AXI Interconnect IP 和 AXI SmartConnect IP 连接

![![[Pasted image 20250216161917.png]]](https://i-blog.csdnimg.cn/direct/421f6aa7f78246aaa0515b8b4fa2900c.png)

基本事务

突发读

![![[Pasted image 20250216154326.png]]](https://i-blog.csdnimg.cn/direct/aa6fd2857b6b4770a046b8b4f13fc0b2.png)

重叠突发读

![![[Pasted image 20250216154333.png]]](https://i-blog.csdnimg.cn/direct/0ae5f7bccdf54b8c941437889e9cf03d.png)

突发写

![![[Pasted image 20250216154341.png]]](https://i-blog.csdnimg.cn/direct/36d0252200c24fe1a0dc6164884a2160.png)

文档链接说明

-

参考文档

深入AXI总线设计:FPGA高效通信的5大秘技 - CSDN文库 -

参考文档

AXI 总线详解-CSDN博客 -

参考文档

AXI总线基础教程:7步带你从零理解AXI协议 - CSDN文库 -

参考文档

AXI4协议学习:架构、信号定义、工作时序和握手机制-CSDN博客 -

参考文档

zynq_AXI接口_笔记-CSDN博客