PCB设计实践(二十三)什么是阻抗匹配,需要做啥

PCB设计中的阻抗匹配是高速数字电路、射频通信、信号完整性等领域的核心技术,其重要性贯穿从基础理论到复杂系统设计的全流程。本文将从工程实践角度深入探讨阻抗匹配的本质原理、应用场景、设计方法、常见误区及解决方案,全面解析这一影响现代电子设备性能的核心要素。

一、阻抗匹配的物理本质与工程价值

在电磁波传输理论中,阻抗匹配的本质是能量传输效率最大化问题。当信号源的输出阻抗(Zs)、传输线特征阻抗(Z0)与负载阻抗(Zl)三者满足Zs=Z0=Zl时,电磁波能量可实现零反射传输。这一定律的工程价值体现在:

信号完整性保障

高速信号上升时间进入纳秒级时,PCB走线已呈现传输线特性。阻抗失配引发的信号反射会导致眼图闭合、时序偏移等问题。例如USB 3.0的5Gbps传输速率下,仅5%的阻抗偏差即可使信号抖动增加30%以上。电磁兼容性优化

失配点产生的驻波会形成电磁辐射热点。实验数据显示,50Ω传输线在70Ω负载下,辐射强度较匹配状态提升6dB,直接导致设备EMI测试超标。功率传输效率提升

在射频功率放大器设计中,阻抗失配造成的回波损耗(Return Loss)直接影响输出功率。2.4GHz WiFi模块的PA输出端若存在10%的阻抗偏差,有效辐射功率将下降15%。

二、典型应用场景与设计规范

1. 高速数字接口

- USB/PCIe/SATA协议

要求差分阻抗90Ω±10%,单端阻抗50Ω。设计要点包括:

- 采用对称蛇形线补偿长度偏差(ΔL<5mil)

- 参考层间距控制(H1<4mil时需采用超低损耗材料)

- 过孔反焊盘直径优化(反焊盘直径=2倍孔径时阻抗变化<3%)

- DDR4/5内存总线

Fly-by拓扑结构下需保持地址/控制线阻抗40Ω±5%,数据线采用动态ODT技术。关键设计参数:

- 线宽/间距比(W/S≥3:1降低串扰)

- 玻纤效应补偿(采用Spread Glass材料)

- 封装互连阻抗匹配(C4凸点阻抗控制)

2. 射频微波电路

天线馈线设计

50Ω同轴电缆转PCB微带线时,采用四分之一波长阻抗变换器:

实际工程中需考虑介质损耗角正切(tanδ<0.002@10GHz)功率放大器匹配网络

使用Smith圆图工具设计L型/T型匹配网络,典型步骤:

- 测量晶体管S参数建立阻抗轨迹

- 添加串联电感/并联电容实现共轭匹配

- 版图实现时采用空气桥降低寄生电容

3. 特殊场景应用

汽车电子CAN总线

120Ω终端电阻需考虑温度漂移(±5%/-40~125℃),采用厚膜电阻阵列实现<1%偏差医疗设备生物电信号采集

高阻抗输入级(>1GΩ)需采用Guard Ring防护环结构,降低漏电流干扰

三、阻抗控制的核心参数与设计方法

1. 传输线参数模型

微带线特征阻抗计算公式:

带状线特征阻抗计算公式:

其中:

- εr:介质相对介电常数

- H:介质厚度(微带线)

- B:上下介质层总厚度(带状线)

- W:走线宽度

- T:铜厚

2. 现代设计工具链

前仿真阶段

使用HFSS/Q3D提取三维场分布参数,精度可达±1%版图实现阶段

Polar SI9000计算工具内置20种传输线模型,支持:

- 差分对间耦合系数设置(0.1<k<0.3)

- 阻焊层厚度补偿(绿油使阻抗降低2-5Ω)

后验证阶段

TDR时域反射仪测量实际阻抗,采样率需>40GHz(上升时间<25ps)

四、典型设计误区与纠正方案

误区1:差分信号无需参考平面

-

错误认知

认为差分对通过相互耦合完成电流回路,忽略地平面作用 -

实验数据

在6层板测试中,移除参考地平面导致:- 共模噪声增加12dB

- 远端串扰(FEXT)上升8dB

-

解决方案

采用共面波导(CPW)结构:- 两侧地铜间距D=3W

- 地铜带过孔间距λ/10

误区2:阻抗线宽优先于层叠结构

- 错误案例

某HDMI接口设计强行采用4mil线宽实现90Ω差分阻抗,导致:- 介质层厚度不足引发层间短路

- 蚀刻公差±0.5mil造成阻抗波动±8Ω

- 科学设计流程

- 确定板材类型(FR4/Rogers)

- 选择合理层厚(H≥3W避免边缘效应)

- 反推线宽/间距参数

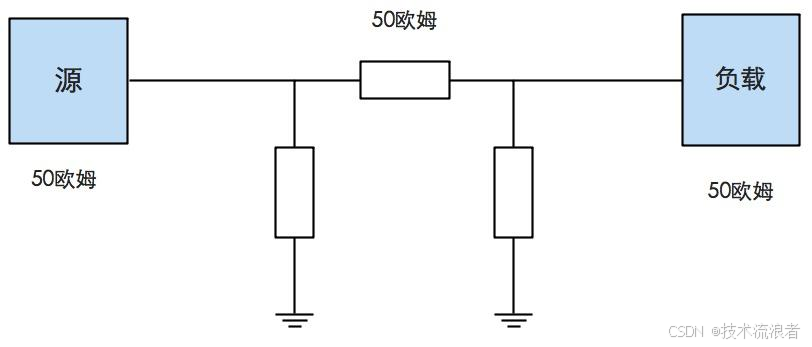

误区3:终端匹配电阻万能论

- 问题场景

在DDR3地址线末端并联39Ω电阻导致:- 驱动电流超负荷20%

- 信号上升时间延长0.5ns

- 匹配策略优化

- 源端串联匹配(Rs=Z0-Zout)

- 戴维南并联匹配(R1=R2=2Z0)

- 交流终端匹配(RC时间常数<0.1UI)

五、先进工艺对阻抗控制的影响

1. 材料创新

超低粗糙度铜箔(RTF铜箔)

表面轮廓Rz<2μm,减少趋肤效应损耗(@10GHz损耗降低30%)混压介质材料

采用M6/M7混压结构实现εr梯度变化,带宽提升2倍

2. 制造工艺

激光直接成像(LDI)

线宽精度±2μm,阻抗控制精度提升至±3%等离子体表面处理

改善孔壁粗糙度(Ra<8μm),降低过孔阻抗偏差

3. 三维集成技术

- 硅通孔(TSV)阻抗建模

采用双指数模型描述高频特性:

其中C≈5fF,R≈50mΩ,τ≈0.1ps

六、未来技术挑战与发展趋势

太赫兹频段阻抗控制

300GHz以上频段需采用空气腔波导结构,传统微带线损耗超过3dB/mm柔性电子阻抗匹配

可拉伸基材(PDMS)的εr变化率需控制在±5%以内光子-电子混合集成

光电共封装中的阻抗过渡结构设计(光电转换界面VSWR<1.2)机器学习辅助设计

CNN神经网络预测阻抗偏差(训练集包含10万组HFSS仿真数据)

通过系统化的理论分析、严谨的工程实践和持续的技术创新,阻抗匹配技术正在突破传统设计边界。从5G基站的大功率阻抗调谐到脑机接口的微伏级信号采集,这一基础理论持续推动着电子技术的演进,成为连接物理原理与工程奇迹的核心纽带。