AXI-LITE slave读写时序

从机接口(被控模块接口)

.s_axi_aclk(s_axi_aclk), // input wire s_axi_aclk

.s_axi_aresetn(s_axi_aresetn), // input wire s_axi_aresetn

.s_axi_awaddr(s_axi_awaddr), // input wire [11 : 0] s_axi_awaddr

.s_axi_awvalid(s_axi_awvalid), // input wire s_axi_awvalid

.s_axi_awready(s_axi_awready), // output wire s_axi_awready

.s_axi_wdata(s_axi_wdata), // input wire [31 : 0] s_axi_wdata

.s_axi_wstrb(s_axi_wstrb), // input wire [3 : 0] s_axi_wstrb

.s_axi_wvalid(s_axi_wvalid), // input wire s_axi_wvalid

.s_axi_wready(s_axi_wready), // output wire s_axi_wready

.s_axi_bresp(s_axi_bresp), // output wire [1 : 0] s_axi_bresp

.s_axi_bvalid(s_axi_bvalid), // output wire s_axi_bvalid

.s_axi_bready(s_axi_bready), // input wire s_axi_bready

.s_axi_araddr(s_axi_araddr), // input wire [11 : 0] s_axi_araddr

.s_axi_arvalid(s_axi_arvalid), // input wire s_axi_arvalid

.s_axi_arready(s_axi_arready), // output wire s_axi_arready

.s_axi_rdata(s_axi_rdata), // output wire [31 : 0] s_axi_rdata

.s_axi_rresp(s_axi_rresp), // output wire [1 : 0] s_axi_rresp

.s_axi_rvalid(s_axi_rvalid), // output wire s_axi_rvalid

.s_axi_rready(s_axi_rready), // input wire s_axi_rready

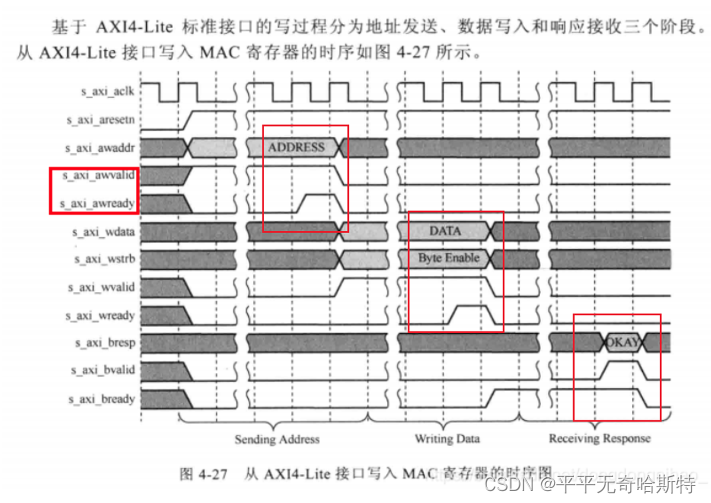

写数据时序

AXI-Lite写操作有两个通道:写地址通道(AW)和写数据通道(W)。

你可以先发送地址,再发送数据,也可以先发送数据,再发送地址,或者同时发送,协议都支持。

只有当地址和数据都有效时,AXI-Lite从接口才会执行一次写操作。

一:地址发送阶段

在写数据过程中,主机的地址连接在s_axi_awaddr总线上,同时将s_axi_awvalid信号拉高,表示主机的有效地址信息已经在信道上等待从机完成接收。同时等待从机发出的接受响应,当从机发送的s_axi_awready有效(拉高)时表示从机允许接收地址信息。

从接口只在s_axi_awvaild和s_axi_awready同时有效时才能完成地址信息的接收,即完成主接口的写地址发送。

awvalid写地址有效是主机发出的,主机来定义写入的数据是否是有效

awready地址接收有效是从机发出的,从机来定义是否可以为有效接收

二:数据写入阶段

主接口发送完地址信息后,准备写入数据,将待写入的数据置于s_axi_wdata总线上(s_axi_wstrb表示写入选通吸信号,默认为11,表示写入数据均可用),并将s_axi_wvalid置为有效(拉高),表示数据已经在信道上等待从机发出的写入响应信号,进而写入从接口。

从接口将s_axi_wready信号拉高,表示从接口可以被写入数据了。

当s_axi_wavaild和s_axi_wready信号同时为1后,表示完成了数据写入

三:响应接收阶段【响应信号表示接收数据是否为有效数据,但完成响应被主机知晓,也需要有响应的有效信号】

主接口完成数据写入后,主机把 s_axi_bready信号拉高(给从机一个我可以接收响应了 的信号),等待从机接口的响应信号。从接口的响应信号s_axi_bresp[1:0]用2‘b00表示数据信道的数据写入成功,即OKEY,从机接口发出的s_axi_bresp响应信号 的有效信号s_axi_bvaild为1时才表示响应有效。

主机的s_axi_bready=1,从机的s_axi_bresp[1:0]=2‘b00,s_axi_bvaild=1,同时满足表示主机接口确认从接口完成了数据的写入。

总结AXI-LITE写数据流程:

- 主机发出写地址(AWADDR+AWVALID),等待AWREADY。(s_axi_awvaild和s_axi_awready同时有效时才能完成地址信息写入)

- 主机发出写数据(WDATA+WVALID),等待WREADY。(s_axi_wavaild和s_axi_wready信号同时为1后,表示完成了数据写入)

- 从机收到地址和数据后,发出写响应(BRESP+BVALID),主机用BREADY响应。

- 一次写操作完成。

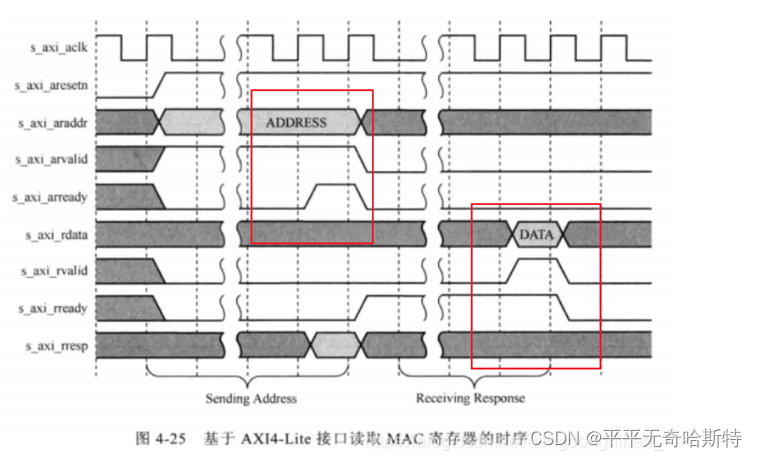

读数据时序

一:地址发送:

主机将要读入的地址输入到s_axi_araddr总线上,同时将s_axi_arvalid信号拉高。表示主机的地址已经在信道上等待从接口完成接收,同时等待从接口发出s_axi_arready信号,当从接口发出的s_axi_arready信号有效时,表示从接口允许接收地址信息。

从接口只在s_axi_arvaild信号和s_axi_arready同时有效时才能完成信息接收,即完成主接口的读地址发送。

二:数据接收:

主机发送完地址请求后,发送接收数据请求信号,将s_axi_rready信号拉高,表示主机可以接收数据了。从接口接收到主接口的准备ready信号后给出响应,在s_axi_rdata总线上发送主机请求的数据,同时把s_axi_rvaild信号拉高,表示s_axi_rdata数据有效,主机根据s_axi_rvaild信号 有效 接收数据,完成数据的读过程。

总结AXI-LITE读数据流程:

- 主机发出读地址(ARADDR+ARVALID),等待从机 ARREADY。

- 从机返回数据(RDATA+RVALID),主机用 RREADY 响应。

- 一次读操作完成。