PCIeSwitch 学习

系列文章目录

文章目录

- 系列文章目录

- 一、核心设备清单

- 二、搭建步骤

- 1. 硬件连接与配置

- 2. 信号完整性验证

- 3. 协议层测试

- 4. 热插拔与可靠性测试

- 5. 兼容性测试

- 三、关键注意事项

- 四、典型应用场景

- 一文读懂什么是PCIe Switch

- 什么是 PCIe Switch

- Virtual Switch/Switch Partitioning

- Multi-root

- Single-Root

- Dynamic Allocation

- 什么是Peer to Peer

- 什么是PCIe Bridge

- 什么是NTB (Non-Transparent Bridge)

- 什么是SR-IOV

- 什么是MR-IOV

- 应用场景

- 1.3 PCle 4.0交换芯片在数据中心的应用

- 第二章 全球 PCle 4.0 交换芯片市场分析

- 2.1 全球 PCle 4.0交换芯片市场规模与增长趋势

- 2.2 主要市场区域分析

- 2.3 市场驱动因素与挑战

- 云计算

- 各种开发板

- NVMe

- DPU

- 1. DPU 的核心功能

- 2. DPU 在 JBOF 中的架构优势

- PCIe Switch 与 GPU

- HPC(High Performance Computing)

- 核心特征

- 知识点

- CTS(Completion Time-out Synthesis)

- 1. CTS的功能与原理

- 2. CTS与PCIe协议的关系

- 3. CTS的应用场景

- 4. 实现案例(Microchip Switchtec™ PCIe Switch)

- DPC(Downstream Port Containment)

- 1. DPC的功能与触发条件

- 2. DPC的工作流程

- 3. DPC的应用场景

- 4. DPC的配置与调试

- 资料

- 1

- 2

- 链接

PCIe Switch测试环境的搭建需结合硬件选型、信号完整性保障及协议验证等多方面因素,以下是基于最新行业实践的详细步骤及设备清单:

一、核心设备清单

-

PCIe Switch测试卡

- 需支持目标PCIe版本(如Gen5/Gen6),提供多端口扩展能力(如Gen5 Switch卡支持4个MCIO接口),推荐SerialCables的Gen5 Switch卡用于链路训练与设备验证。

- 需兼容热插拔功能,支持带电更换设备时的信号隔离与稳定性。

-

信号完整性测试设备

- 高带宽示波器:如泰克DPO/MSO70000系列(≥60GHz带宽),用于捕获PCIe 5.0/6.0高速信号,分析眼图、抖动等参数。

- 误码仪:支持PCIe 5.0/6.0速率,检测数据传输误码率,评估链路可靠性。

- 参考时钟源:提供高精度时钟信号(频率精度≤±5ppm),确保多设备同步。

-

协议与功能验证工具

- 协议分析仪:如Keysight BSA286C,监控链路训练、错误恢复等协议行为,验证PCIe规范符合性。

- 自动化测试软件:如泰克TekExpress(含PCE5选项),支持脚本化测试流程,自动配置设备参数并生成报告。

- PCIe CV软件:验证配置空间寄存器设置,检测基本配置、能力寄存器等合规性。

-

测试夹具与线缆

- PCI-SIG标准夹具:如CBB(主板+插接板)用于附加卡测试,CLB用于系统级测试,确保电气连接可靠性。

- 接口转换夹具:如U.2转E3.S、M.2转EDSFF等,适配不同形态的SSD或加速卡。

- 低损耗线缆:如Saniffer升级版Raw Wires,减少高速信号衰减,优化信号完整性。

-

环境控制设备

- 温箱:支持-40°C至125°C温度范围,用于高低温环境下的稳定性测试。

- 功耗分析模块:如Quarch PAM夹层,实时监测设备功耗与sideband信号。

二、搭建步骤

1. 硬件连接与配置

- Switch卡部署

将PCIe Switch卡插入主板的PCIe x16插槽(需支持Gen5/Gen6速率),通过MCIO接口连接延长线至测试背板。 - 被测设备(DUT)接入

使用转接卡将DUT(如NVMe SSD、GPU)连接至Switch卡下游端口,确保物理链路对齐并固定。 - 供电与信号控制

通过背板sideband信号线控制DUT的复位、供电拉高/拉低,并连接温箱实现温度循环测试。

2. 信号完整性验证

- 眼图与抖动测试

使用示波器捕获PCIe链路信号,分析眼图张开度(≥80%)、抖动(RJ/TJ≤500fs)等参数,对比PCIe规范阈值。 - 通道裕量测试

通过Gold System调整信号参数,模拟不同信道损耗条件,评估DUT在劣化环境下的误码率表现。

3. 协议层测试

- 链路训练验证

监控Link Training & Status State Machine(LTSSM),确保从L0到L0s/L1状态切换正常,无链路协商失败。 - 错误注入与恢复

使用协议分析仪模拟错误场景(如LCRC错误),验证Switch卡及DUT的错误恢复机制是否符合PCIe规范。

4. 热插拔与可靠性测试

- 自动化热插拔脚本

编写脚本循环执行DUT插拔操作,记录链路重连时间及状态稳定性,测试最大插拔次数阈值。 - 高低温循环测试

在温箱中设置梯度温度(如-40°C→125°C),持续运行DUT 72小时,监测信号完整性及功耗变化。

5. 兼容性测试

- 多厂商设备互操作性

连接不同品牌DUT(如三星、西数SSD),验证Switch卡对多源设备的兼容性。 - 混合速率测试

在Gen5 Switch卡上混合连接Gen5/Gen4设备,测试链路速率协商与流量调度能力。

三、关键注意事项

-

信号完整性优化

- 优先使用背板布线方案,减少走线长度(≤3英寸),避免直角弯折。

- 高频测试需选用低损耗延长线(如Saniffer Raw Wires),并定期校准夹具阻抗。

-

环境干扰控制

- 温箱测试时需配置氮气吹扫,避免冷凝水对电路板造成腐蚀。

- 实验室需配备电磁屏蔽室,减少外部噪声对高速信号的干扰。

-

数据安全与备份

- 自动化测试需实时记录日志,并设置异常中断自动保存功能,防止数据丢失。

- 测试报告需包含原始数据、图表及合规性结论,便于后续问题追溯。

四、典型应用场景

- 企业级SSD验证:批量测试Gen5 SSD在温箱中的耐久性,验证4K随机读写性能稳定性。

- Switch芯片开发:验证多端口负载均衡算法及故障切换机制。

- 数据中心互连:模拟GPU集群通过Switch卡扩展的端到端链路性能。

通过上述步骤及设备配置,可构建覆盖功能、性能及可靠性的PCIe Switch测试环境。如需Gen6环境搭建细节,可参考《PCIe5&6.0测试白皮书》第5章。

一文读懂什么是PCIe Switch

一文读懂什么是PCIe Switch

什么是 PCIe Switch

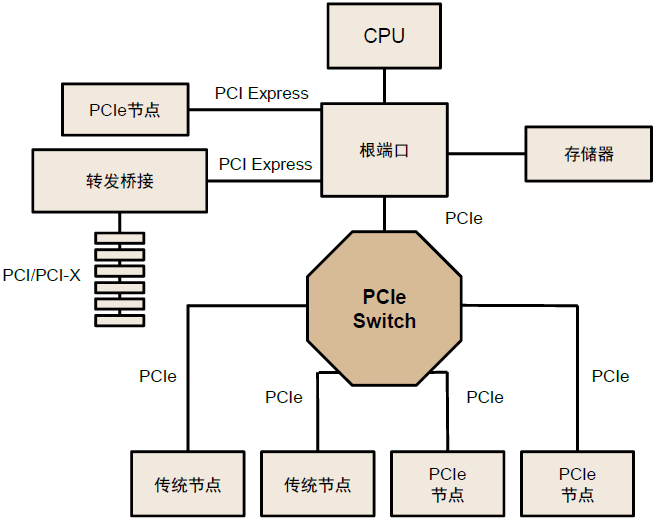

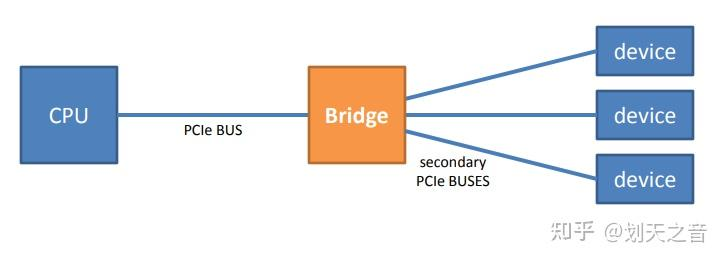

PCIe Switch是一种硬件设备,提供扩展或聚合能力,并允许更多的设备连接到一个PCle端口。它具有以下功能:

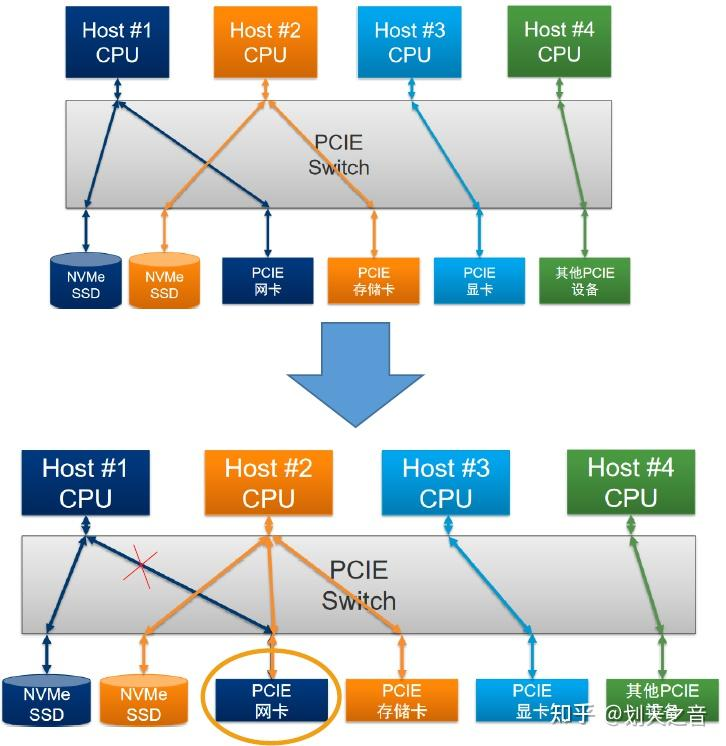

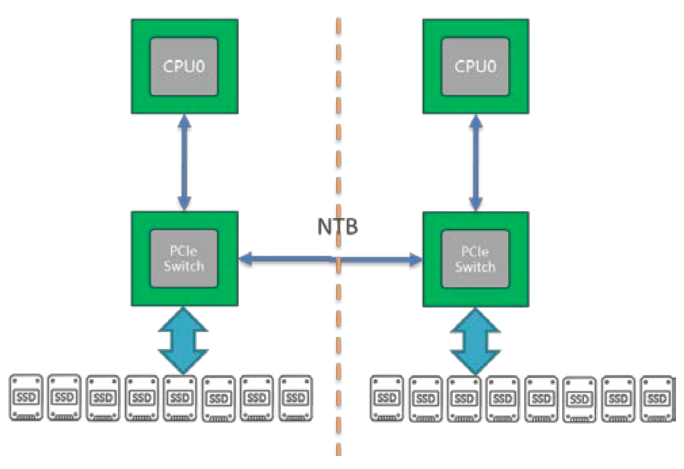

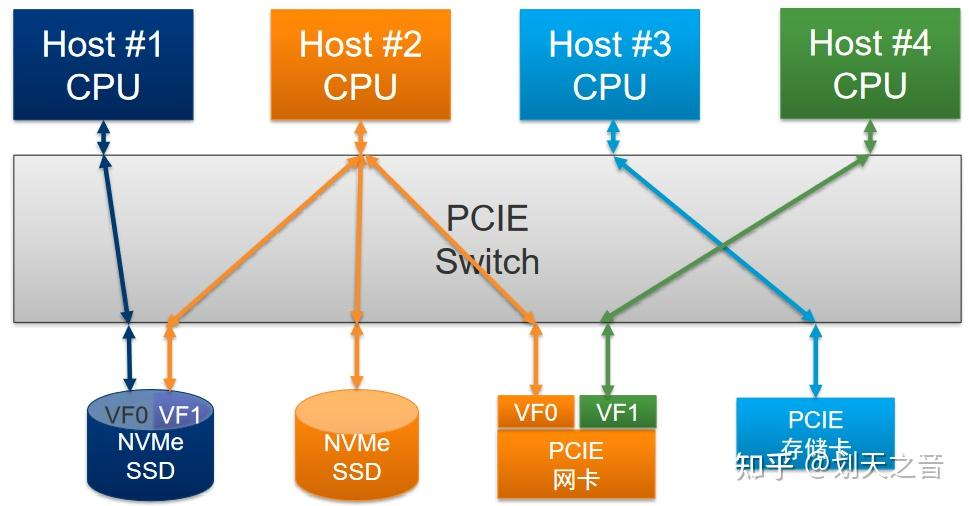

连接多个设备:PCIe switch允许多个设备通过单个PCIe总线连接到主机系统,从而扩展系统的连接性。数据交换:PCIe switch可以在多个设备之间传输数据,允许设备之间直接通信而无需通过主机处理器。动态分配:支持动态分配带宽和资源,根据需要调整设备之间的通信速率和优先级。NTB(Non-Transparent Bridge):支持NTB技术,允许两个或多个系统之间直接通信,提高数据传输效率。Peer to Peer:支持点对点通信,设备之间可以直接进行数据交换而无需通过主机。MRIOV(Multi-Root I/O Virtualization):支持多根IO虚拟化,允许多个根端系统共享单个PCIe设备。SRIOV(Single Root I/O Virtualization):支持单根IO虚拟化,允许单个PCIe设备被划分为多个虚拟功能。

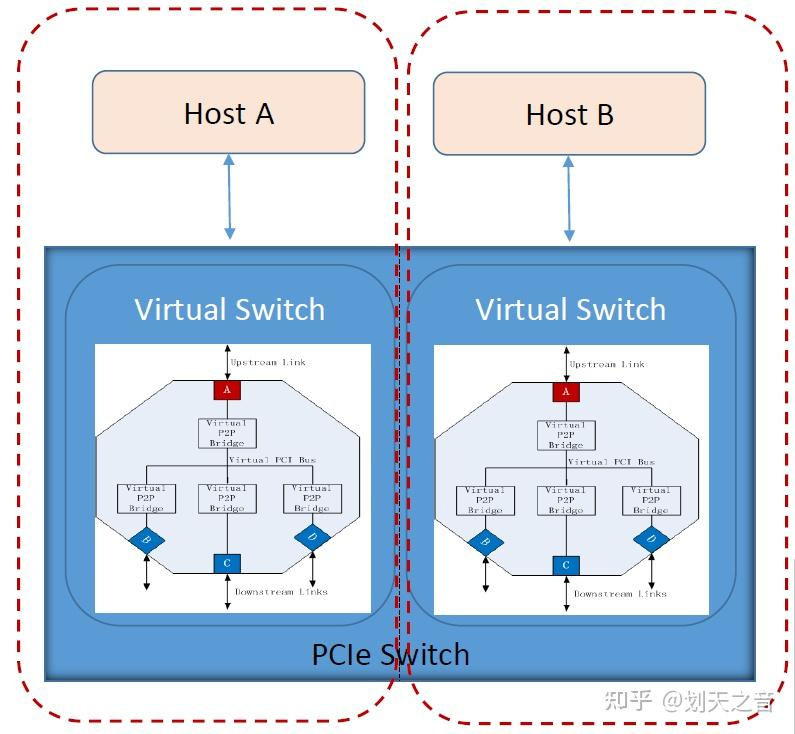

Virtual Switch/Switch Partitioning

Multi-root

Single-Root

Dynamic Allocation

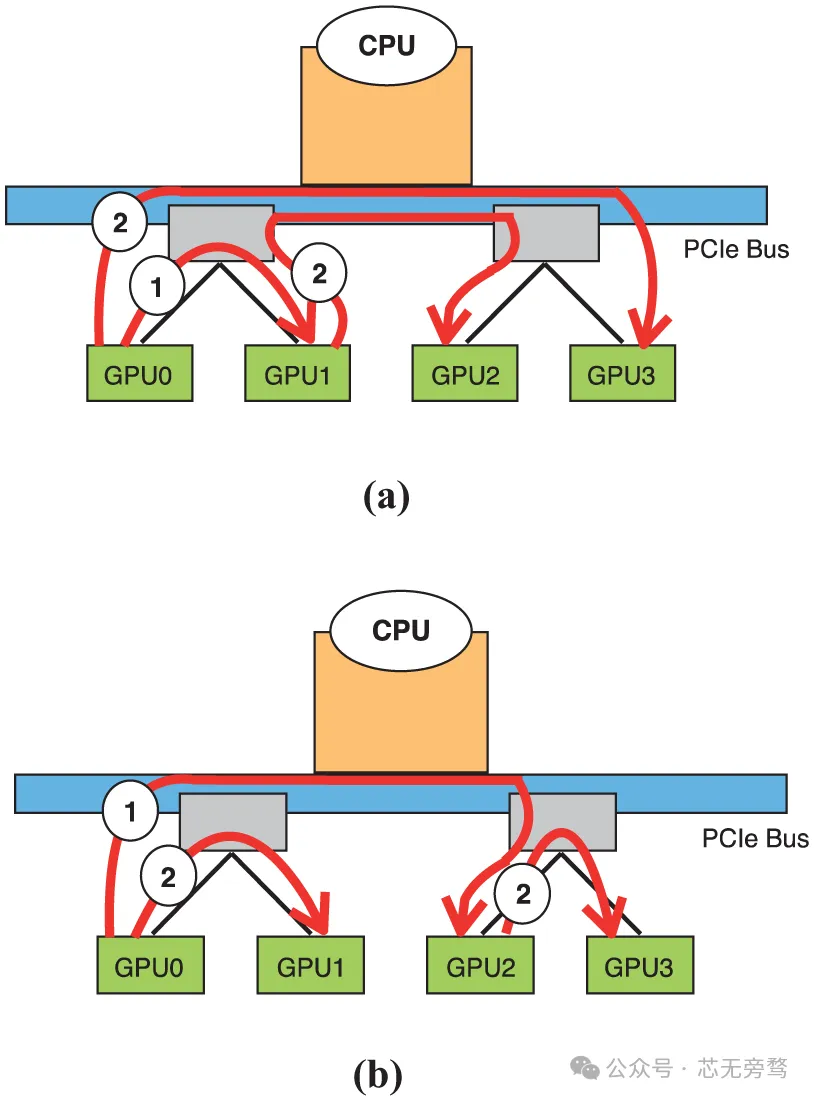

什么是Peer to Peer

什么是PCIe Bridge

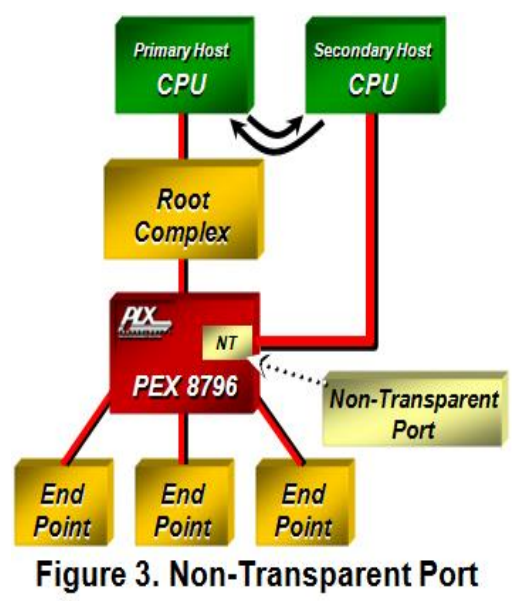

什么是NTB (Non-Transparent Bridge)

什么是SR-IOV

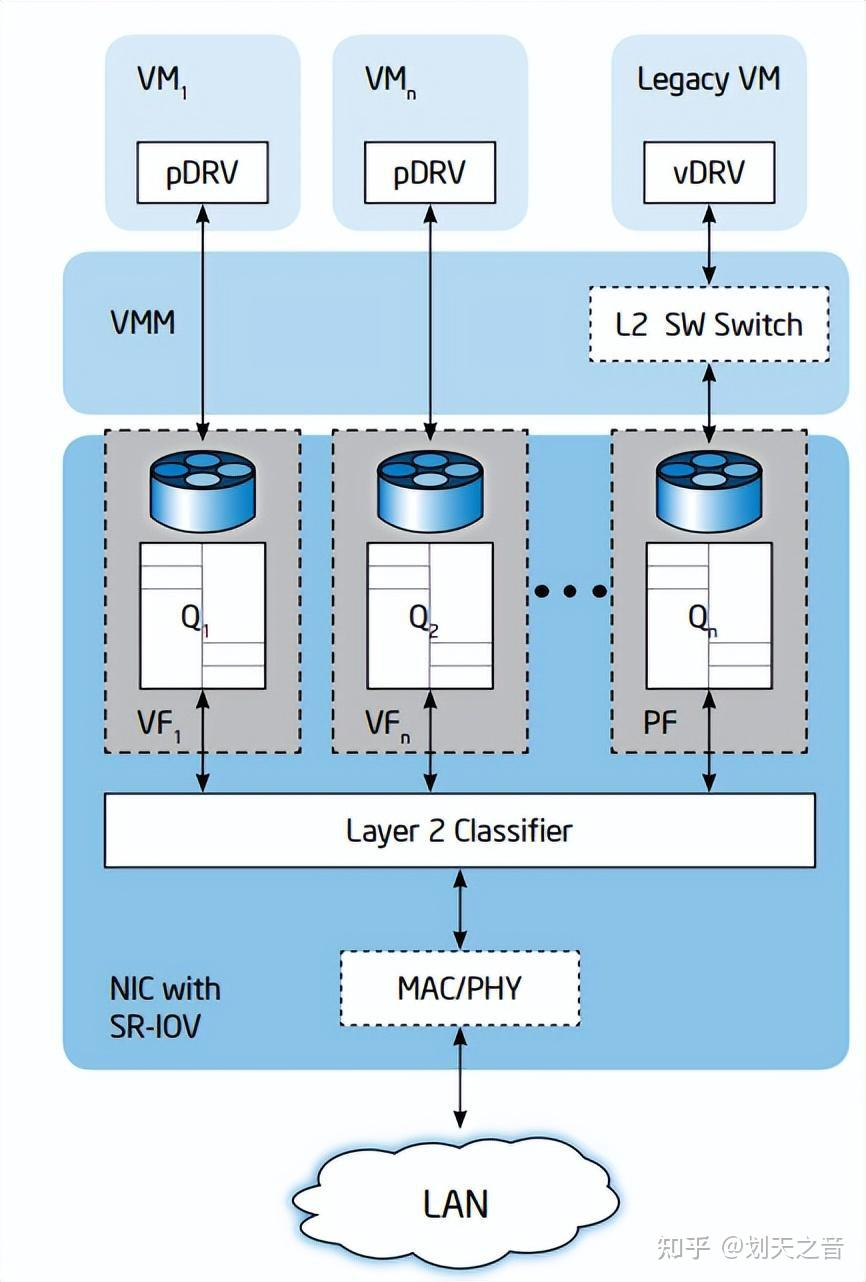

SR-IOV(Single Root I/O Virtualization)是一种PCI Express(PCIe)技术,用于在虚拟化环境中提高网络和存储设备的性能和效率。SR-IOV允许单个物理设备(如网卡或存储控制器)在多个虚拟机之间共享,同时保持高性能和低延迟。

什么是MR-IOV

MRIOV(Multi-Root I/O Virtualization)是一种PCI Express(PCIe)技术,用于在Multi-Root系统之间共享单个PCIe设备的虚拟化功能。通常情况下,PCIe设备只能由Single-Root端系统独占使用,而MRIOV技术允许Multi-Root系统同时访问和共享同一个PCIe设备。

应用场景

- 服务器

- AI 服务器,GPU 间连接

- 通用服务器

- 存储服务器, JBOF

- 信创服务器

2024-2030全球PCle4.0交换芯片行业调研及趋势分析报告

PCIe Switch 4.0 能够在服务器、存储系统和网络设备之间提供高速的数据传输能力,是实现高性能计算和大数据处理的关键组件。

1.3 PCle 4.0交换芯片在数据中心的应用

- PCle 4.0交换芯片在数据中心的应用日益广泛,特别是在高性能计算(HPC)和大数据处理领域。随着数据中心对数据传输速度和带宽需求的不断增长,PCIe4.0交换芯片提供了更高的数据传输速率和更低的延迟,成为提升数据中心性能的关键。例如,在HPC领域,高性能计算集群需要快速的数据交换能力来处理大规模计算任务。采用PCIe4.0交换芯片的数据中心可以支持高达256GB/s的数据传输速率,这对于加速科学研究和工程设计计算至关重要。

- 在存储系统中,PCle 4.0交换芯片的应用同样显著。随着数据量的爆炸性增长,企业对存储性能的要求越来越高。PCIe 4.0交换芯片能够提供高速的数据读写速度,支持 NVMe(Non-Volatile Memory Express)存储解决方案,从而实现更快的存储性能。例如,在数据中心中,使用PCIe4.0交换芯片的NVMeSSD存储系统可以实现高达7.68GB/S的连续读写速度,显著提升了数据中心的 I/0性能。

- 此外,PCIe4.0交换芯片在数据中心网络架构中的应用也日益增多。随着网络虚拟化和软件定义网络(SDN)技术的发展,PCIe 4.0交换芯片能够提供灵活的网络配置和更高的网络性能。例如,在数据中心网络中,PCIe4.0交换芯片可以支持高达 100个端口,每个端口的带宽达到 32GT/s,这使得交换芯片能够满足大规模网络部署的需求。以谷歌数据中心为例,其采用了PCIe 4.0交换芯片来实现高速的网络连接,提高了数据中心的整体网络性能和可靠性。

第二章 全球 PCle 4.0 交换芯片市场分析

2.1 全球 PCle 4.0交换芯片市场规模与增长趋势

- 根据市场研究数据显示,全球PCle4.0交换芯片市场规模在2024年预计将达到数十亿美元,预计在未来五年内将以复合年增长率(CAGR)超过20%的速度增长。这一增长主要得益于数据中心和云计算行业的快速发展,以及对高性能计算和大数据处理需求的不断上升。

- 在全球范围内,数据中心是PCIe 4.0交换芯片最大的应用市场。随着企业对数据中心性能要求的提高,以及新兴技术的广泛应用,如人工智能、机器学习和边缘计算,PCIe 4.0交换芯片的需求量持续增加。据预测,到2030年数据中心市场对PCIe 4.0交换芯片的需求将占全球总需求的 60%以上。

- 除了数据中心市场,PCle 4.0交换芯片在服务器存储和网络设备中的应用也在不断扩大。随着5G通信技术的推广和物联网(IOT)设备的普及,对高速数据传输的需求不断增长,PCIe 4.0交换芯片在这些领域的应用潜力巨大预计随着技术的成熟和市场需求的增加,PCIe4.0交换芯片的市场规模将继续保持稳定增长态势。

2.2 主要市场区域分析

- 在全球 PCIe4.0交换芯片市场区域分析中,北美地区占据着重要的市场份额。北美地区的数据中心建设和云计算基础设施发展迅速,对高性能交换芯片的需求量大。根据市场研究报告,2024年北美地区PCIe4.0交换芯片的市场份额预计将达到30%,这一比例预计将在未来几年内保持稳定。以亚马逊 AWS 和微软 Azure 等云计算巨头为例,它们在数据中心部署了大量的PCIe 4.0交换芯片,以支持其高速数据传输需求。

- 欧洲地区也是PCIe 4.0交换芯片市场的重要区域随着欧洲数据中心市场的增长,以及对高性能计算和大数据处理的重视,PCIe 4.0交换芯片的需求持续上升。特别是德国、英国和法国等国家,它们在人工智能、自动驾驶和生物信息学等领域的研发投入,推动了PCIe4.0交换芯片的应用。据统计,2024年欧洲地区POle4.0交换芯片的市场份额预计将达到25%,预计未来几年将保持稳定增长。

- 亚太地区,尤其是中国和日本,是全球PCe 4.0交换芯片市场增长最快的区域。随着中国云计算市场的快速发展,以及日本在半导体和电子制造领域的强大实力,亚太地区 PCIe 4.0交换芯片的市场份额预计将从2024 年的 20%增长到 2030 年的 35%。以阿里巴巴、腾讯和百度等中国互联网巨头为例,它们在数据中心和云计算领域的投资,为PCIe4.0交换芯片市场提供了巨大的增长动力。此外,韩国和新加坡等国家的数据中心建设也推动了PCIe4.0交换芯片的需求增长。

2.3 市场驱动因素与挑战

- 市场驱动因素方面,全球PCIe 4.0交换芯片行业的主要驱动力包括数据中心和云计算的快速增长,以及新兴技术的广泛应用。据市场研究机构预测,全球数据中心市场预计将在 2024 年至 2030 年间以每年超过 10%的速度增长:这直接推动了PCIe 4.0交换芯片的需求。例如,谷歌和亚马逊等大型云服务提供商在数据中心部署了大量的PCIe 40交换芯片,以支持其高速数据传输和存储需求。

- 另一个重要驱动因素是高性能计算(HPC)领域的快速发展。随着科学研究和工程设计对计算能力要求的提高HPC 市场对 PCIe 4.0交换芯片的需求也在不断增长。例如,美国国家超级计算应用中心(NCSA)在升级其超级计算机时选择了支持PCIe 4.0的交换芯片,以实现更高的数据传输速度和更低的延迟。

- 尽管市场前景广阔,PCIe 4.0交换芯片行业也面临着一些挑战。首先,高昂的研发成本和制造成本限制了新进入者的进入。此外,随着技术的不断进步,保持产品竞争力需要持续的研发投入。例如,随着5G和物联网(IOT)技术的兴起,PCIe4.0交换芯片需要适应更广泛的应用场景:这要求制造商在产品设计和功能上不断创新。同时,全球供应链的不稳定性和原材料价格的波动也给行业带来了不确定性。

云计算

云计算(Cloud Computing)是指通过互联网提供按需计算服务,包括服务器、存储、数据库、网络、软件和分析

云计算允许客户端设备通过互联网访问租用的计算资源,如数据、分析和云应用。它依赖于云服务提供商(CSP)所拥有和运营的远程数据中心、服务器和存储系统网络。云计算的工作流程通常包括以下步骤:

- 客户通过互联网向云提供商发起服务请求。

- 请求到达云提供商管理的大型数据中心。

- 云提供商的软件动态分配必要的资源来满足客户请求。

- 分配的资源处理请求,并将结果通过互联网返回给客户。

| 模型 | 定义 | 示例 |

|---|---|---|

| IaaS | 提供基础计算资源(虚拟机、存储、网络) | AWS EC2、阿里云ECS |

| PaaS | 提供应用开发与部署平台(数据库、中间件、运行时环境) | Google App Engine、Heroku |

| SaaS | 提供可直接使用的软件服务(通过浏览器或API访问) | Microsoft 365、Salesforce |

各种开发板

边缘计算、物联网、人工智能

NVMe

JBOF、EBOF 与 NVMe-of

NVMe(Non-Volatile Memory Express)详解

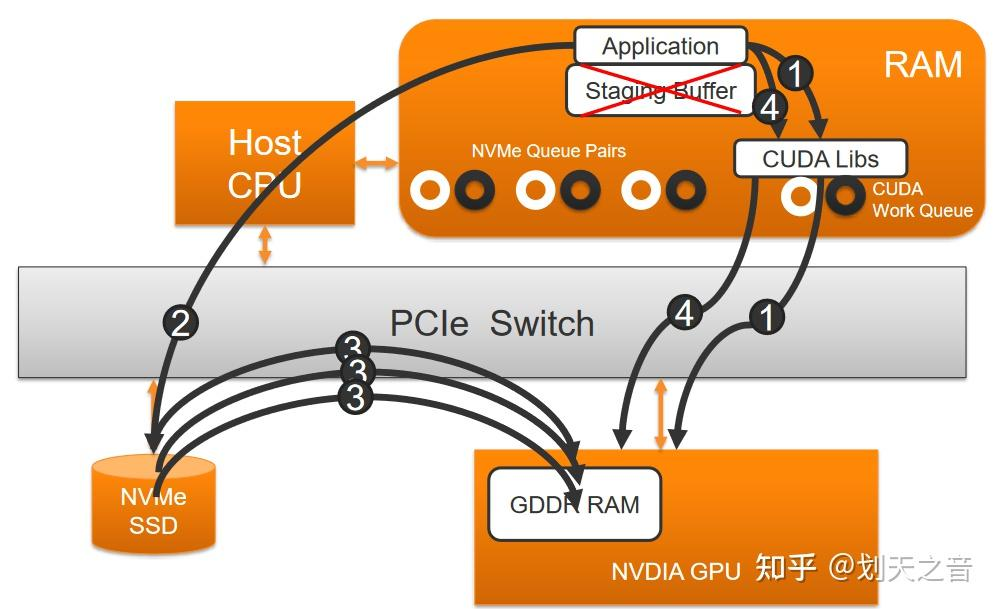

- NVMe(非易失性内存主机控制器接口规范)是一种 基于PCIe总线的高性能存储协议,专为固态硬盘(SSD)设计,旨在替代传统的AHCI协议(如SATA)。

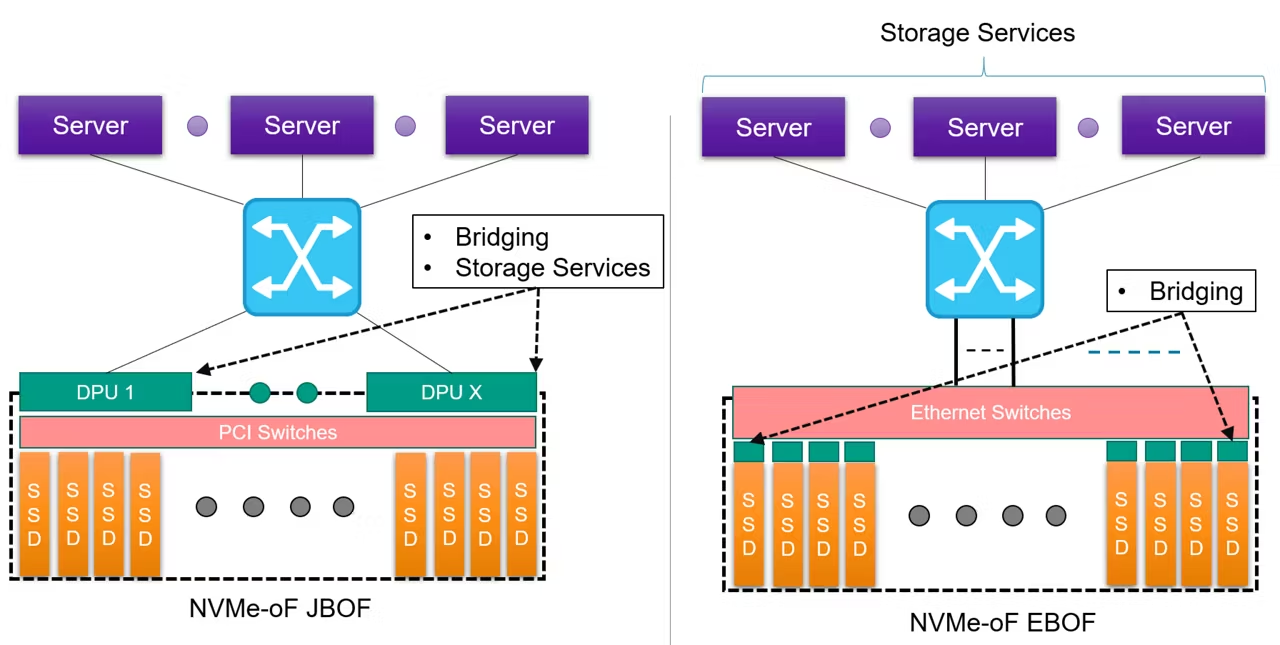

- NVMe-oF(NVMe over Fabrics)是一种将NVMe协议扩展到网络存储环境的技术,通过RDMA、光纤通道(FC)或TCP等传输层实现高性能存储访问。

- EBOF(Ethernet Bunch of Flash,一堆以太网闪存)

- JBOF (Just a Bunch of Flash,一堆闪存)是一种专注于闪存存储的高密度设备,其核心理念是将多个NVMe固态硬盘(SSD)集成到单一机箱中,通过PCIe交换机实现扩展和连接。

- JBOD(Just a Bunch of Disks)

| 技术 | 特点 | 适用场景 |

|---|---|---|

| JBOF | 基于PCIe扩展,无CPU设计,专注本地闪存性能 | 高性能计算、本地存储池 |

| EBOF | 通过以太网交换机连接SSD,NVMe-oF转换在SSD端完成(1:1桥接) | 分布式存储、跨节点资源共享 |

| JBOD | 传统机械硬盘扩展方案,无协议优化 | 大容量冷存储 |

DPU

在JBOF(Just a Bunch of Flash)中,DPU(Data Processing Unit,数据处理单元) 是一种专为数据中心设计的处理器,通过硬件加速和任务卸载技术优化存储性能与管理效率。其核心作用是将传统存储架构中由CPU处理的网络、存储协议和安全任务转移到专用芯片上执行,从而释放CPU资源并提升整体效率。以下是具体解析:

1. DPU 的核心功能

-

协议卸载与加速

DPU直接处理NVMe-oF(NVMe over Fabrics)、RDMA等存储协议转换任务,例如将主机端的NVMe命令封装为网络数据包,或解析远程存储请求并映射到本地SSD。这种硬件加速避免了CPU参与协议栈处理,显著降低延迟(如Supermicro基于BlueField DPU的JBOF在4KB随机读取测试中延迟低至86μs,比x86方案提升13%)。 -

网络与存储资源管理

DPU集成PCIe交换机、网络接口(如400Gb/s以太网/InfiniBand)和存储控制器功能,可动态分配带宽、管理多主机并发访问,并通过RDMA实现数据直连SSD,绕过CPU中转。 -

安全与隔离

提供硬件级加密(如AES-256)、数据完整性校验和访问控制策略执行,确保存储数据在传输和存储过程中的安全性。例如,BlueField DPU支持独立的安全引擎,可对存储流量进行端到端加密。

2. DPU 在 JBOF 中的架构优势

-

性能提升

- 低延迟:通过卸载CPU密集型任务(如NVMe-oF协议转换),DPU使存储访问延迟降低至微秒级,满足AI训练、高频交易等场景需求。

- 高吞吐:支持400Gb/s网络带宽和并行处理多路I/O请求,例如Supermicro JBOF的吞吐量可达50GB/s。

-

能效优化

DPU替代传统x86 CPU、NIC和DRAM模块,功耗降低高达50%。例如,BlueField DPU的硬件加速引擎仅需处理特定指令,而通用CPU的利用率从50%降至接近空闲状态。 -

扩展性与灵活性

- 多主机共享:通过PCIe Switch连接多个计算节点,实现存储资源池化,支持动态扩展至PB级容量(如Supermicro JBOF支持36个E3.S SSD或24个U.2 SSD)。

- 异构协同:DPU可与GPU协同工作,例如在AI推理中直接处理数据预处理任务,减少GPU等待数据加载的时间。

Supermicro 推出由 NVIDIA BlueField 提供支持的 JBOF 以优化 AI 存储

存储网络SAN、NVMe oF等

NVMe-oF E-JBOF设计解析:WD RapidFlex网卡、OpenFlex Data24

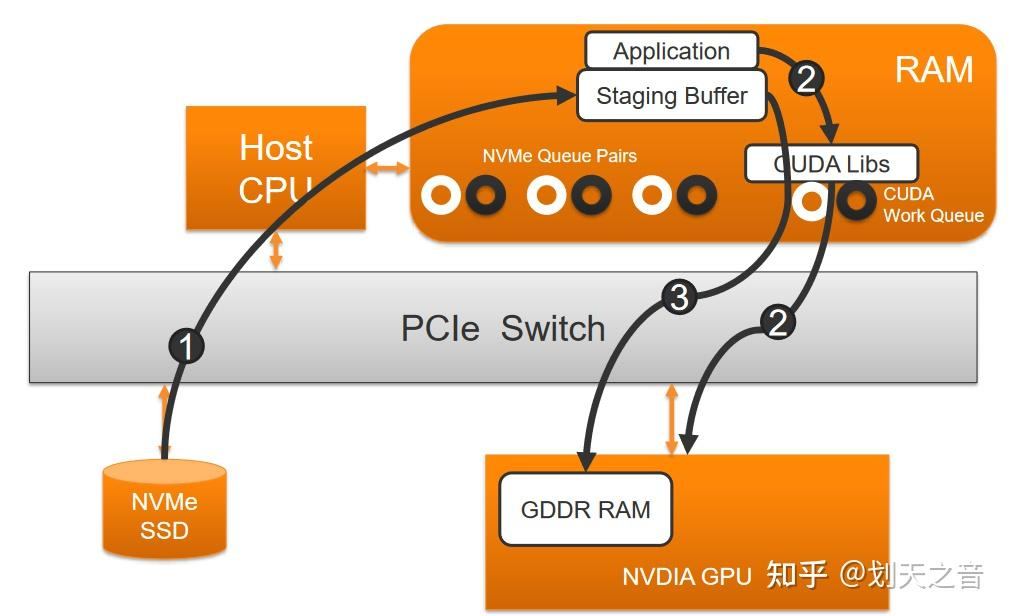

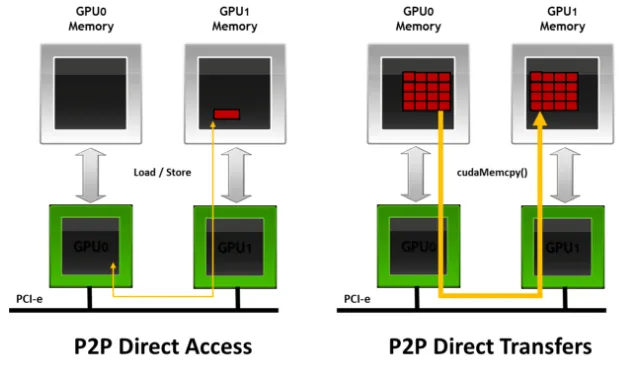

PCIe Switch 与 GPU

浅析GPU通信技术(上)-GPUDirect P2P

浅析GPU通信技术(中)-NVLink

浅析GPU通信技术(下)-GPUDirect RDMA

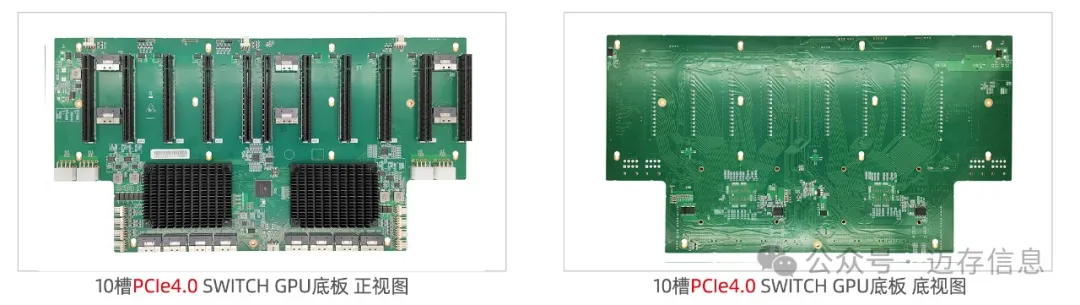

GPU底板

HPC(High Performance Computing)

HPC(高性能计算,High Performance Computing)领域是指利用超级计算机、计算集群等高性能计算资源,解决大规模复杂计算问题的技术体系。其核心目标是通过聚合计算能力,实现传统计算机难以完成的高吞吐量、高精度计算任务。

核心特征

- 计算能力

单精度浮点运算速度可达每秒万亿次(TFLOPS)以上,部分超算系统甚至达到E级(百亿亿次/秒)水平,如我国的神威太湖之光。 - 系统架构

由多台计算节点通过高速网络(如InfiniBand、RoCE)互联,结合分布式存储系统(如Lustre文件系统),形成松散耦合的集群架构。 - 应用场景

主要服务于科学计算(如气候模拟、基因测序)、工程仿真(航空航天流体力学)、金融分析(高频交易)、AI训练(深度学习模型优化)等领域。

知识点

CTS(Completion Time-out Synthesis)

PCIe Switch中的 完成超时合成(Completion Time-out Synthesis, CTS) 是一种可靠性增强机制,主要用于处理请求方(Requester)未收到完成包(Completion)时的超时场景。以下是其核心要点:

1. CTS的功能与原理

- 功能:当Switch作为中间设备转发请求时,若下游设备(Completer)未在规定时间内返回完成包,CTS会合成一个虚拟的完成包(数据全为

0xFF)并返回给请求方,避免系统因等待响应而陷入阻塞。 - 触发条件:超时时间由上游设备(如CPU)配置,通常通过PCIe寄存器的

Completion Timeout Value字段设定,范围从50微秒到50毫秒不等。 - 合成逻辑:CTS会记录所有非发布型(Non-Post)请求,并启动定时器。超时后自动生成全

0xFF的完成包,同时通知固件(FW)进行错误处理(如重置设备或记录日志)。

2. CTS与PCIe协议的关系

- 协议定位:PCIe协议规定根复合体(Root Complex)和端点(Endpoint)需支持完成超时机制,但Switch本身无需支持(因其不主动发起请求)。

- 扩展实现:Microchip等厂商在Switch中自定义实现CTS,作为对PCIe协议栈的补充,提升复杂系统(如多级Switch或嵌入式设备)的可靠性。

3. CTS的应用场景

- 复杂拓扑系统:在含多级Switch的系统中,CTS可避免因下游设备故障或链路拥塞导致的上游设备挂起。

- 错误恢复:合成完成包后,系统可快速触发错误处理流程(如重试或重置),减少宕机时间。

- 兼容性:返回全

0xFF的完成包符合多数驱动对“异常状态”的判定逻辑,便于上层软件识别错误。

4. 实现案例(Microchip Switchtec™ PCIe Switch)

- 硬件支持:Microchip的PCI100x系列Switch集成CTS功能,支持PCIe 4.0规范,速率达16GT/s。

- 配置方式:通过寄存器配置超时阈值,并配合固件实现错误上报与恢复逻辑。

DPC(Downstream Port Containment)

PCIe Switch中的下游端口遏制(Downstream Port Containment, DPC)是一种关键的错误处理机制,旨在防止PCIe链路中不可纠正的错误扩散,从而提升系统可靠性。以下是其核心要点:

1. DPC的功能与触发条件

- 功能:当DPC端口检测到不可屏蔽的不可纠正错误(如硬件故障、热插拔异常等)或收到严重错误消息(如ERR_FATAL/ERR_NONFATAL)时,DPC会立即隔离下游端口,阻断链路通信,避免错误传播。

- 触发条件:

- 硬件错误:如链路层协议错误、数据链路协议错误等(需通过DPC寄存器配置错误掩码)。

- 错误消息:下游设备上报的ERR_FATAL或ERR_NONFATAL消息(取决于DPC触发使能配置)。

2. DPC的工作流程

- 错误检测与触发:

- DPC端口检测到错误后,设置触发状态位并记录错误源ID(如请求者ID)。

- 若未启用DPC,错误可能通过链路向上传播,导致系统级故障。

- 链路隔离:

- 下游端口的LTSSM(链路训练与状态机)进入Disabled状态,链路完全断开。

- 所有待处理的TLP(事务层数据包)被丢弃,Non-Posted请求返回UR(Unsupported Request)或CA(Completion Abort)。

- 错误恢复:

- 软件需清除DPC触发状态位,链路重新进入检测(Detect)状态并尝试重新训练。

- 若错误持续,系统可能执行设备重置或热插拔操作。

3. DPC的应用场景

- 热插拔场景:如NVMe SSD暴力拔插时,DPC可快速隔离故障端口,避免未完成I/O导致的数据损坏。

- 高可靠性系统:在数据中心、工业设备中,DPC防止错误扩散,保障关键任务连续性。

- 与AER协同:DPC通常与高级错误报告(AER)结合,AER记录错误细节,DPC执行隔离操作。

4. DPC的配置与调试

- 寄存器配置:

- DPC Capability Register:定义触发条件(如启用ERR_FATAL触发)。

- DPC Status Register:记录触发原因(如错误类型、请求者ID)。

- 调试注意事项:

- DPC触发后,下游端口寄存器可能返回全F值,需软件特殊处理。

- 需确保链路完全断开后再重新启用,避免状态残留。

资料

1

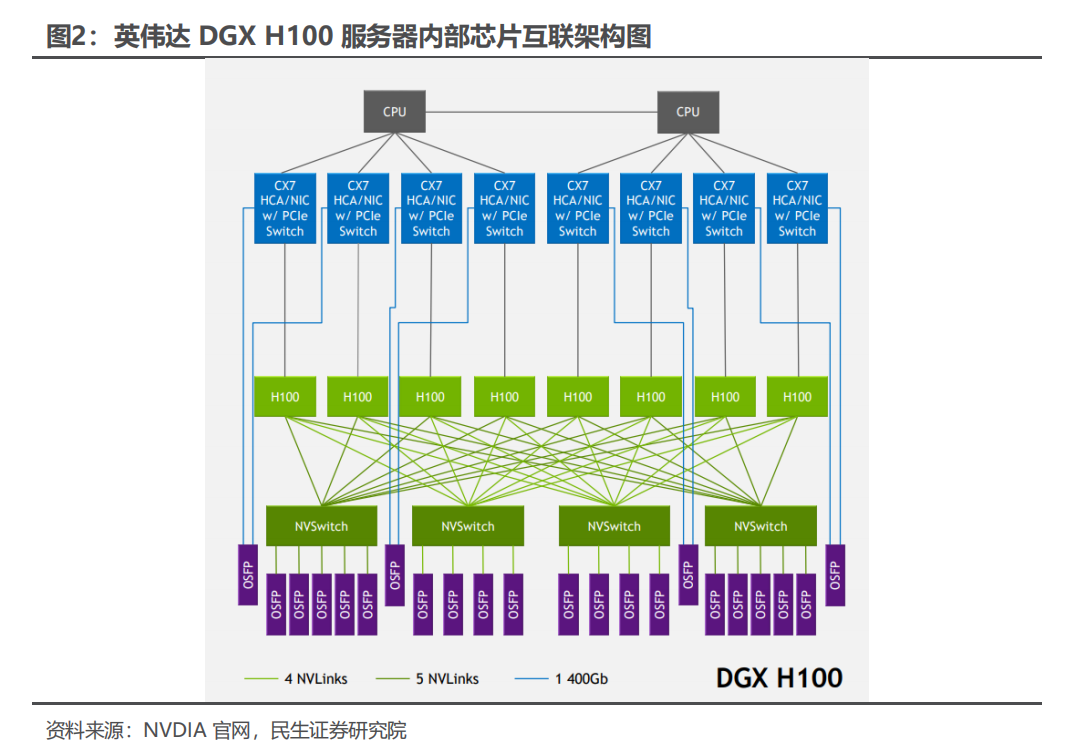

AI 服务器:NVLink,NVSwitch

2

Dual-Host & Failover Support(双主机和故障转移支持)

链接

NVMe-oF E-JBOF设计解析:WD RapidFlex网卡、OpenFlex Data24