LVDS系列12:Xilinx Ultrascale系可编程输入延迟(二)

本节讲解Ultrascale IDELAYE3的参数;

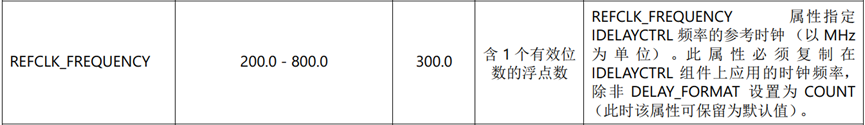

IDELAYE3参数:

REFCLK_FREQUENCY:如果使用COUNT模式,保持300MHz的默认值即可;

如果使用TIME模式,则该值与IDELAYCTRL参考时钟要匹配;

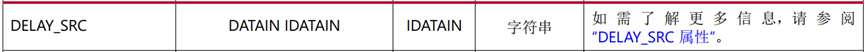

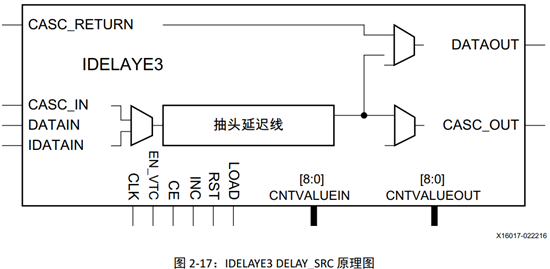

DELAY_SRC:

如果想延时来自IOB的输入信号,那么使用IDATAIN,如果想延时来自FPGA内部逻辑的信号时,使用DATAIN,DELAY_SRC参数设置为DATAIN时,未使用的IDATAIN端口需悬空;

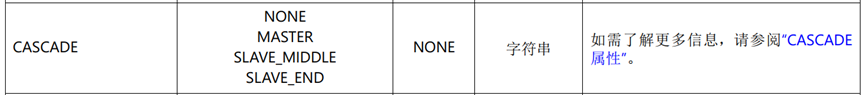

CASCADE:

如果不使用级联,那么CASCADE设置为NONE。

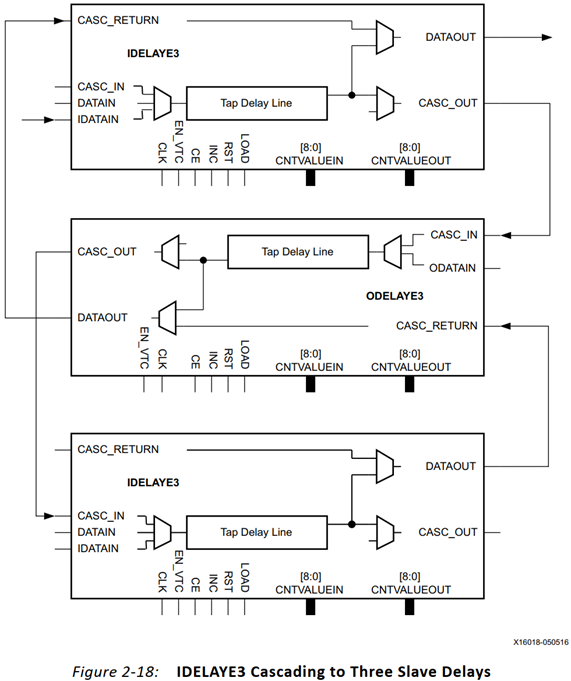

当所需要的延迟大于1.25ns(Ultrascale)或是1.1ns(Ultrascale+)时,可以使用级联,下图为组件之间的连接关系图;

上图中可以看到,IDELAYE3的级联操作需要ODELAYE3一起穿插使用,第一级CASCADE参数设置为MASTER,中间级设置为SLAVE_MIDDLE,最后一级设置为SLAVE_END,级联组件之间的布线是专用高速布线,IDELAYE3 或 ODELAYE3 级联的固定内部插入延迟总量是初始插入延迟与级联插入延迟的总和。此延迟按 IDELAYE3 和 ODELAYE3 级联次数而成倍增加。

在TIME模式下级联时,同一site下两者延迟要相同,如把IDELAYE3延时0.75ns,级联的ODELAYE3延时0.75ns,那么就延时了1.5ns,在FIXED模式下DELAY_VALUE设置两者相同,VAR_LOAD模式下两者CNTVALUEIN输入相同值;

由于级联使用到了ODELAYE3,级联的详细使用等后续ODELAYE3介绍后再考虑讲解;

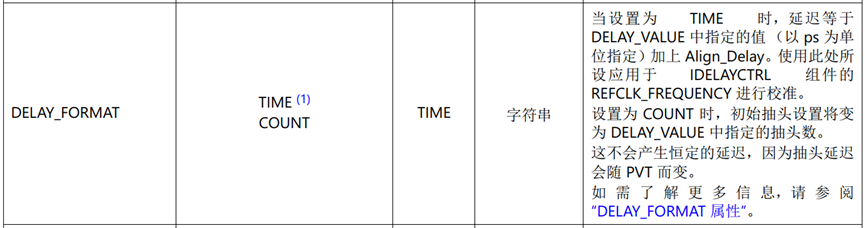

DELAY_FORMAT:该参数选择使用TIME模式还是COUNT模式;

原语抽头分辨率为,Ultrascale系列抽头分辨率为2.5ps15ps,Ultrascale+系列抽头分辨率为2.1ps12ps;

COUNT模式:

不使用IDELAYCTRL;

不对眼延迟线进行校准,且电压温度发生变化时也不会保持不变;

REFCLK_FREQUENCY 属性保留为默认值 (300 MHz)即可;

将 EN_VTC 输入管脚连接到低电平,由于COUNT模式不需要校准,所以不使用VTC校准功能,拉低该管脚可确保禁用 IDELAYE3中的校准和VT维护逻辑;

COUNT模式下延时长短使用抽头数量表示,该模式下DELAY_VALUE参数表示预设延时抽头数量,CNTVALUEIN/OUT[8:0]值分别表示为延迟线设置值或是组件正在使用的抽头数量;

共有512个抽头,抽头数量值0~511;

由于COUNT模式没有校准操作,所以抽头到底延迟多少时间根本无法获知,仿真中看到的只是一个标准值,实际上板工作时随工艺电压温度影响,只能确定每个抽头的延迟范围为Ultrascale系列抽头分辨率为2.5ps15ps,Ultrascale+系列抽头分辨率为2.1ps12ps,至于使用时延迟时间具体为其中哪个值,这个没法获取,所以该模式下不要纠结延时多少,延时多长时间不重要,延迟线的抽头数量才重要,所以COUNT模式下延时的计量靠抽头数量而不是延时时间;

TIME模式:

必须使用IDELAYCTRL;

IDELAYCTRL参考时钟频率必须与REFCLK_FREQUENCY参数匹配;

使用FIXED模式时,EN_VTC管脚置高,一直开启校准;

使用VARIABLE或VAR_LOAD模式时,需主动操作EN_VTC管脚,也就是要修改抽头值时,将EN_VTC管脚置0,停止校准操作,等待写入修改抽头值完毕后,再将EN_VTC管脚置1,也就是组件正常工作时要将EN_VTC管脚置1,保证工作时EN_VTC管脚置1能校准延迟;

这里有一点要注意:

在内置自校准(BISC :built-in self-calibration)过程中,输入延迟线IDELAY用于消除串并转换过程中第一个触发器输入处的时钟到数据偏差。此过程会耗用一定数量的输入延迟线抽头,这称为 Align_Delay,该Align_Delay延迟仿真无法观察,只有实际上板才能看到。

当 DELAY_VALUE 设置为 0 ps 时,报告的 Align_Delay值介于 45 到 65 个抽头之间,通过 CNTVALUEOUT可以读出该值。

如果在输入延迟线中全部写入 0 值,或者如果写入的抽头数量小于报告的 Align_Delay 值,则会影响 BISC 插入的Align_Delay,并可能在捕获数据时引发问题。

Align_Delay这里相关后续细节讲解;

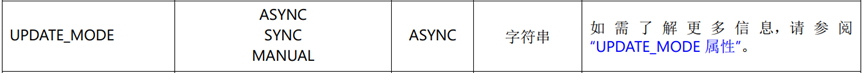

UPDATE_MODE:用于设置更改延迟生效时间的模式;

ASYNC:异步模式,延迟的递增或递减在CLK 时钟端口边沿触发,与数据变化无关。

SYNC:同步模式,延迟的递增或递减在CLK 时钟边沿和 DATAIN (或 IDATAIN)的边沿同步更新。此模式适用于始终定期切换的时钟或数据。

MANUAL:手动模式,则需要 2 次 LOAD 断言有效才能使新值生效。第一次 LOAD 将 CNTVALUEIN 定义的值加载到延迟线选择寄存器中,第二次LOAD必须与CE一起断言有效,以使新值生效。这对于需要使用延迟线更新一定数量的数据通道的设计是有益的,该手动模式与7系的VAR_LOAD_PIPE模式功能相同;

注释:在没有其他特殊要求时,简单使用,首选方法是 ASYNC 模式,因为延迟线仅在延迟线的CLK时钟上更新,而无需考虑其它信号或事件。

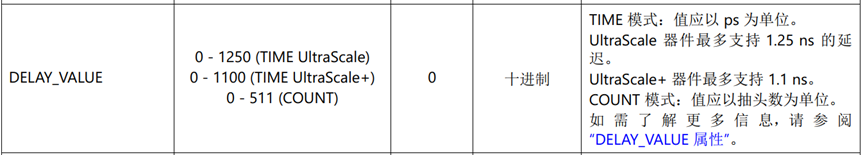

DELAY_VALUE:

当 DELAY_FORMAT属性设置为TIME模式时,DELAY_VALUE属性表示延时时间,以ps为单位。

且实际延时,除DELAY_VALUE参数设置的延时外,IDELAYE3还具有时钟/数据对齐延迟,如前述的Align_Delay,数据经过组件还有一个固定的延时(像是7系就是过组件,就算抽头数为0,也有一个600ps的固定延时,这里U系固定延时在仿真中应该能看到)。通过IDELAYE3的延迟总量为对齐延迟、固定延时、DELAY_VALUE三者之和。

在TIME 模式下DELAY_VALUE表示以ps为单位的时间值,但CNTVALUEIN[8:0]、 CNTVALUEOUT[8:0]在延迟线上读取或写入的值是抽头数的值,不是时间值。因此,更改延迟线的时间需要进行一些计算,后续结合实际详细讲解;

当DELAY_FORMAT参数设置为COUNT模式时, DELAY_VALUE属性表示抽头数量。由于在 COUNT 模式下没有校准或补偿,因此时钟/数据没有 Align_Delay。此时通过 IDELAYE3 的延迟应该就为过组件的固定延迟加上抽头的延迟,后续在仿真中应该能观察到。

在COUNT模式下使用延迟线时,EN_VTC管脚必须设置低电平。在TIME 模式下使用延迟线时,当IDELAYCTRL的RDY为低电平时,EN_VTC管脚必须设置高电平。

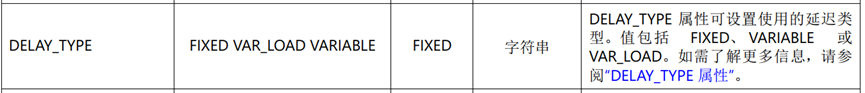

DELAY_TYPE:延时模式设置;

FIXED模式:设置为固定时间延时的延迟模式,配置后无法更改;

VARIABLE模式:可变抽头线,抽头线可递增递减的延迟模式;

VAR_LOAD模式:可变抽头线,可动态加载抽头值同时可以递增递减抽头值的延迟模式;

延时模式比较复杂,后续章节将结合实际一一讲解;

本文章由威三学社出品

对课程感兴趣可以私信联系