ZYNQ笔记(十七):IP核封装与接口定义

版本:Vivado2020.2(Vitis)

任务:将“HDMI彩条显示实验”(正点原子 ZYNQ FPGA 开发视频)中所实现的 RGB2DVI 模块封装成一个 IP 核。

目录

一、介绍

(1)IP核

(2)IP核接口

二、创建与封装 IP

(1)创建

(2)封装

(3)接口定义

一、介绍

(1)IP核

IP核(Intellectual Property Core)是预设计、可复用的硬件功能模块(如FFT、DDR控制器、PCIe等),以封装形式(.xci或.xcix文件)集成到 Vivado设计中,简化开发流程。

-

类型:

-

软核(Soft IP):用HDL描述,可综合到不同器件(如Vivado自带的AXI GPIO)。

-

硬核(Hard IP):物理固化在芯片中(如UltraScale+的PCIe硬核)。

-

(2)IP核接口

接口(Interface) 定义了IP核与外部系统的通信规则,包括信号类型、时序和协议(如AXI、APB、UART、自定义接口等);端口(Port) 则是接口在硬件上的具体实现,即实际的输入/输出引脚(如clk、data、valid等)。

本次例程即封装一个带自定义接口的软IP核。

二、创建与封装 IP

流程和之前的自定义AXI IP核有一定区别,是创建封装一个无 AXI 接口的 IP核,注意区分:ZYNQ笔记(六):自定义IP核-LED呼吸灯

(1)创建

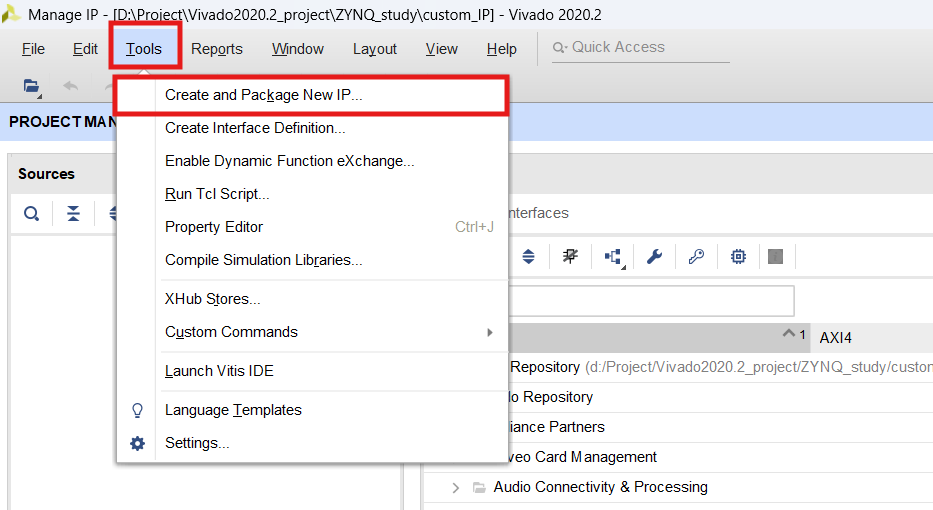

(1.1)新建一个IP管理工程(或任意打开一个vivado工程),点击Tools — Create and Package New lP 创建与封装一个新IP核。

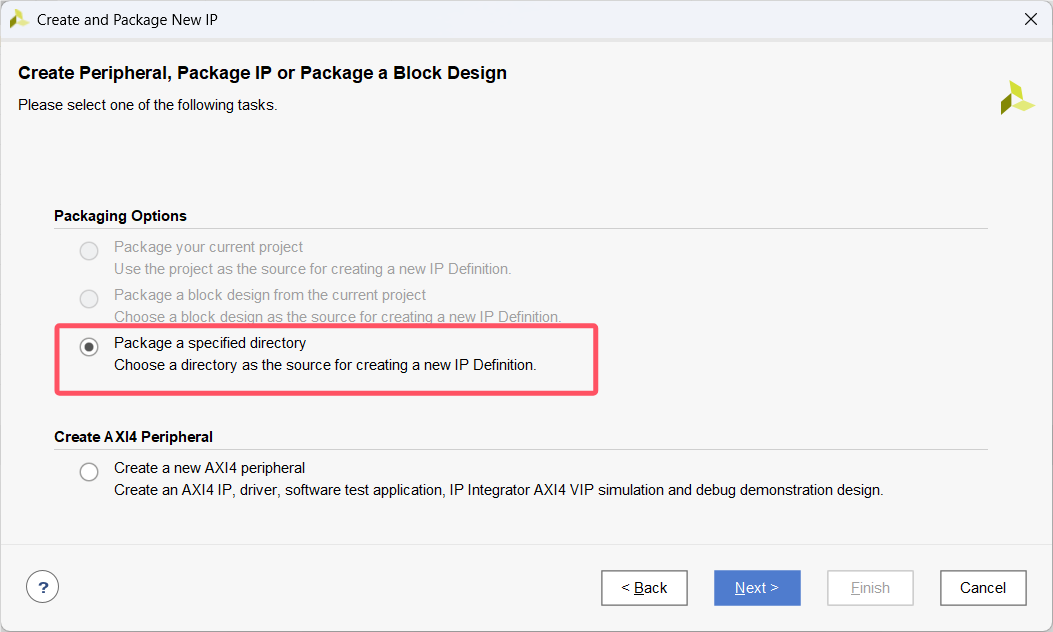

(1.2)选择打包到一个指定目录:(上面两个选项是打包当前工程和BD设计工程,因为我是在IP管理工程开始新建IP的,所以没有可用的设计工程可打包,所以不可选),IP核没用到AXI接口,不勾选创建AXI外设。

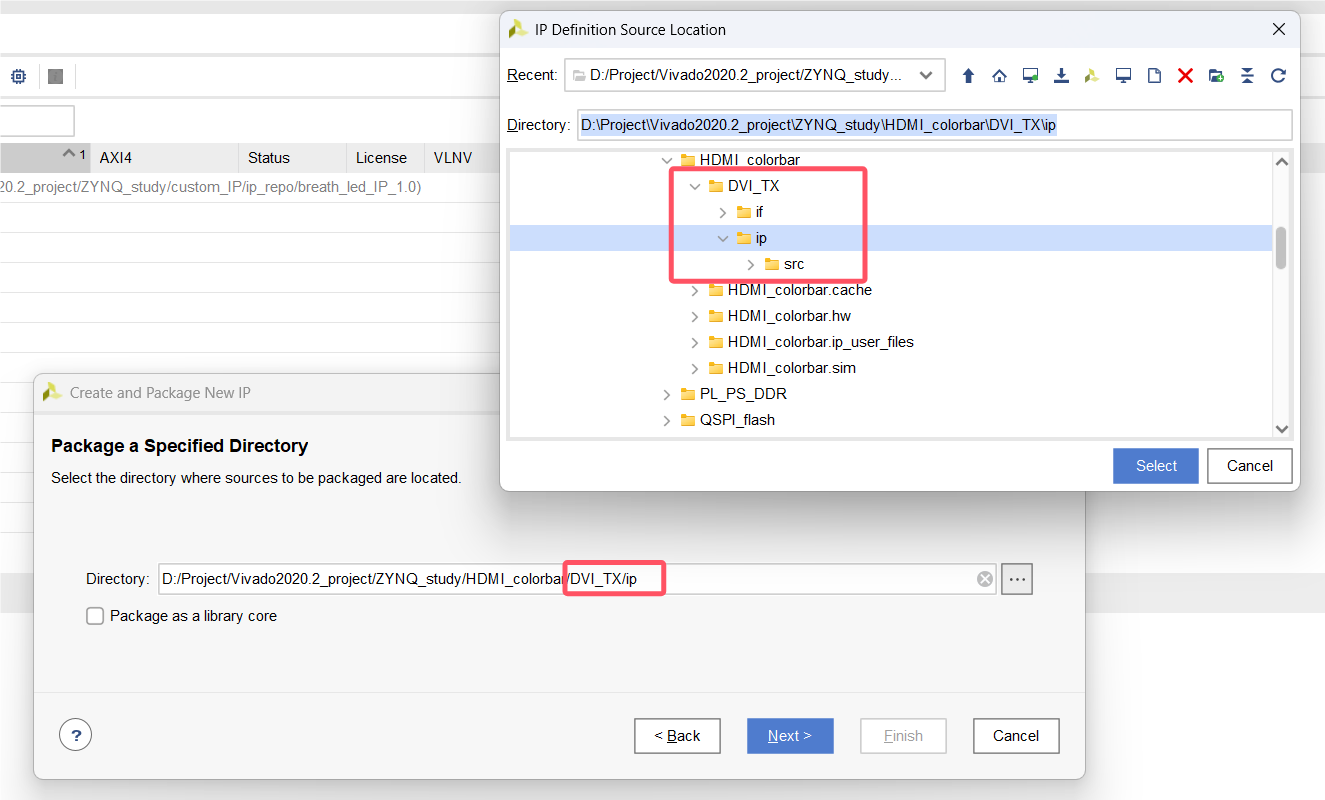

(1.3)源文件路径选择 DVI_TX/ip :

DVI_TX 文件夹是提前建好了的,ip文件夹内的src用于存放设计源文件,我已经拷贝了所需要打包为IP的.v设计文件(之后再添加也是一样的);if 文件夹后面用于存放接口定义相关的文件。

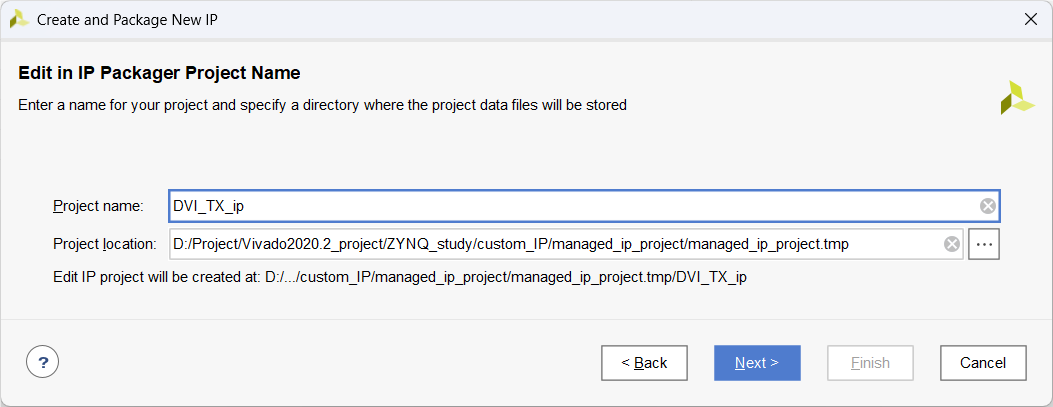

(1.4)接下来是IP核的存放路径,就默认放在我的自定义IP文件夹目录下,命名为DVI_TX_ip:

(2)封装

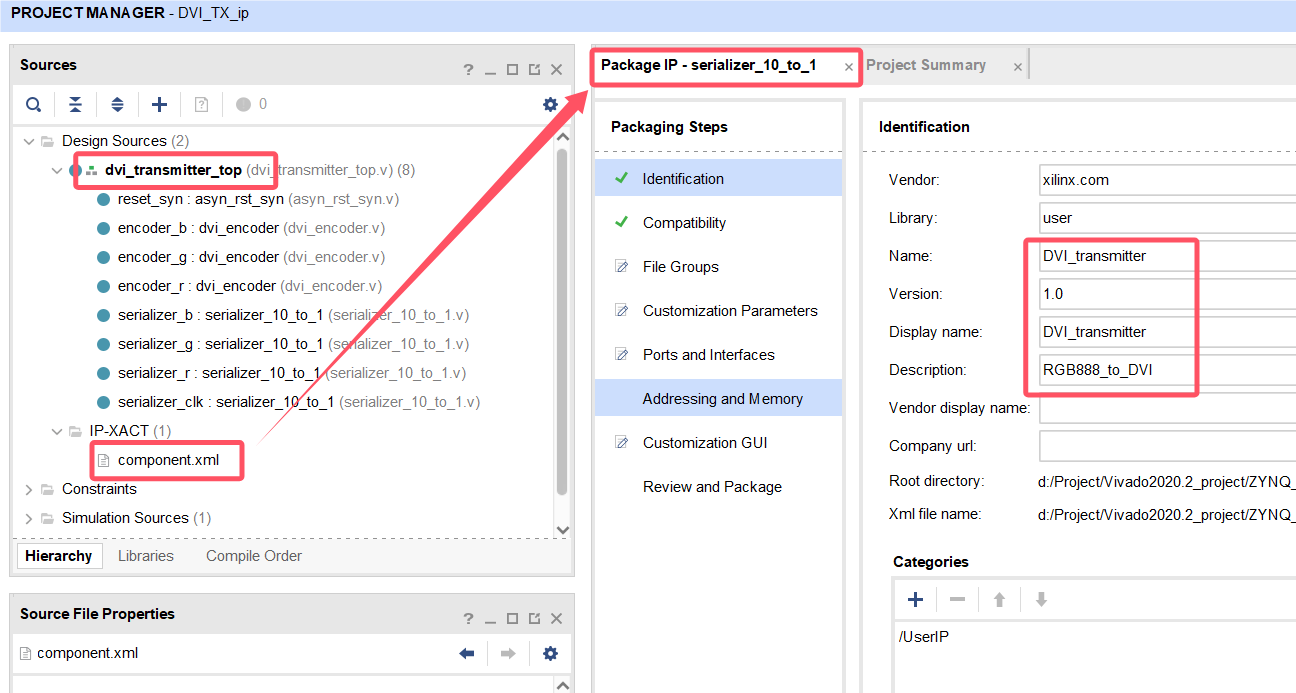

(2.1) 检查设计源文件无误后,开始设置 IP 封装:将界面切换至 Package IP,如果关闭的话,可以通过 IP-XACT 界面下的 component.xml 重新打开。并根据需求修改IP信息:名称、版本、显示名、描述。

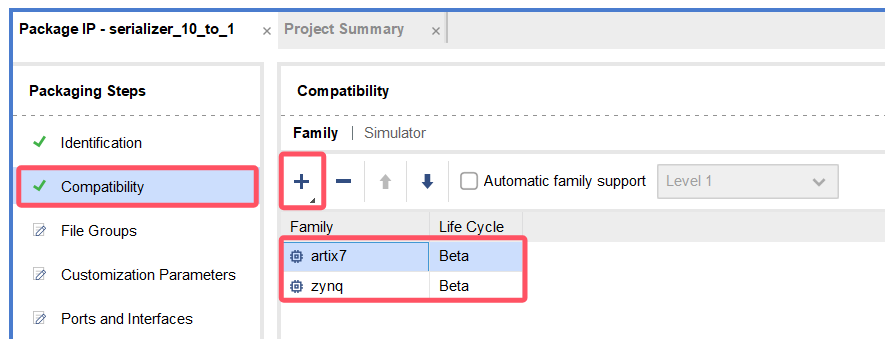

(2.2)第二栏兼容设置,选择IP支持芯片型号,点击 Family 一栏下的“+”图标,选择“Add Family Explicitly”这里勾选 “Artix7” 和 “zynq(zynq-7000)” ,因为源文件设计用到了Artix7的原语。

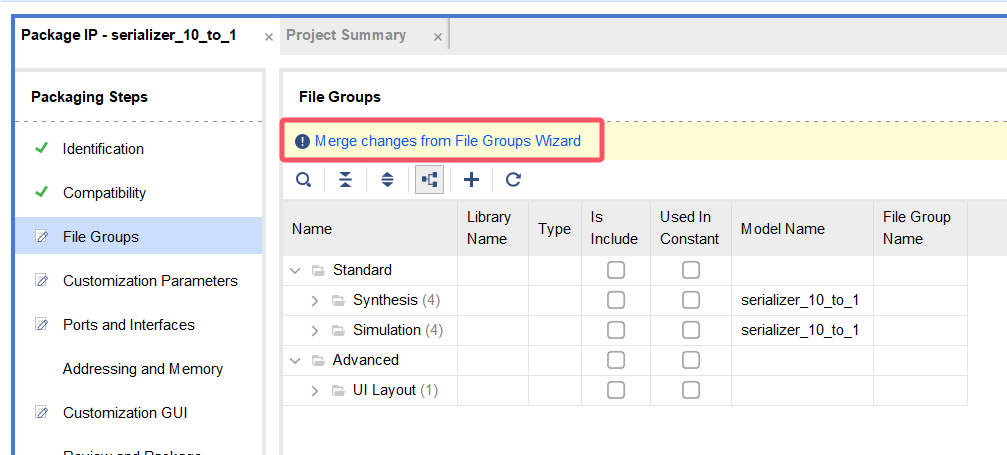

(2.3)在文件组(File Groups)中列出了 IP 核所使用到的源文件,如果修改了文件他不会显示 “绿色打勾” 的状态,点击界面上的“Merge Changes from Gile Groups Wizard”更新一下即可,如下图所示:

(2.4)在 Customization Parameters 栏中做同样操作进行更新,由于在 RGB2DVI 模块中没有定义 parameter 变量,因此在 Customization Parameters 页面工具没有识别 到任何变量,也看不到、并不会显示 “绿色打勾” 的状态。

(3)接口定义

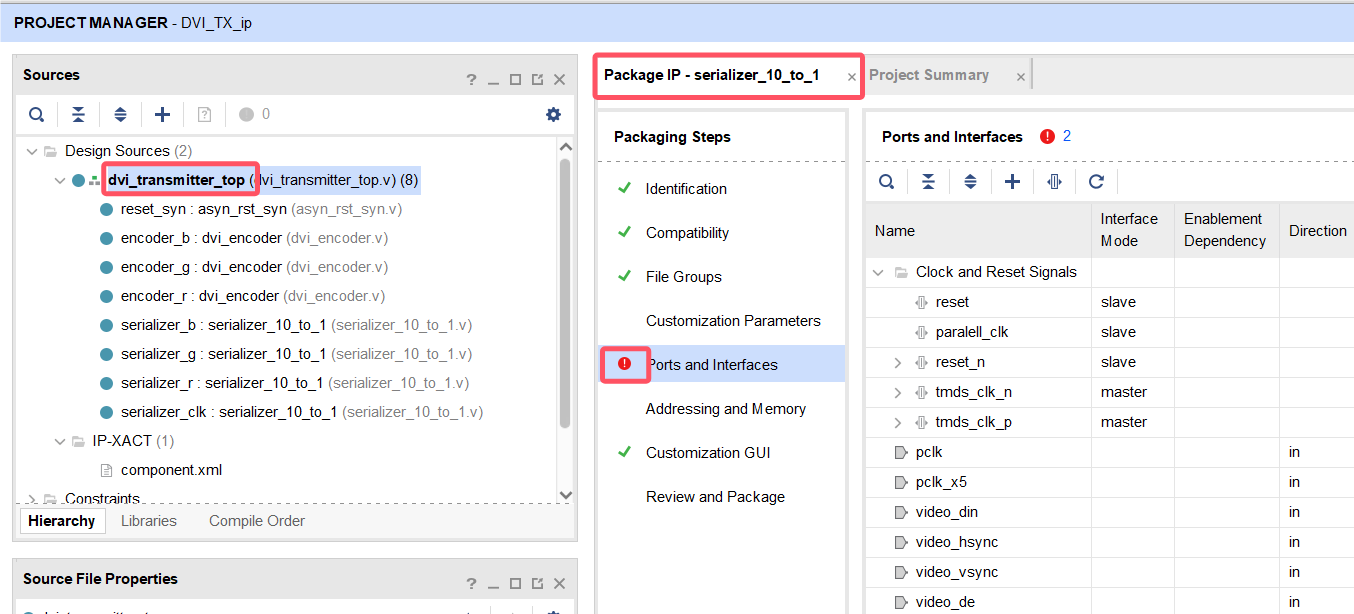

(3.1)设置端口和接口:上面一步更新后可能会报错,是因为顶层模块的端口识别出错(顶层模块一开始是 serializer 10 to 1 是错的,是后来修改为DVI_transmitter_top的,这里没有更新过来),可以看到IP核的名字不是顶层模块 DVI_transmitter_top,识别到他的子模块 serializer 10 to 1去了。

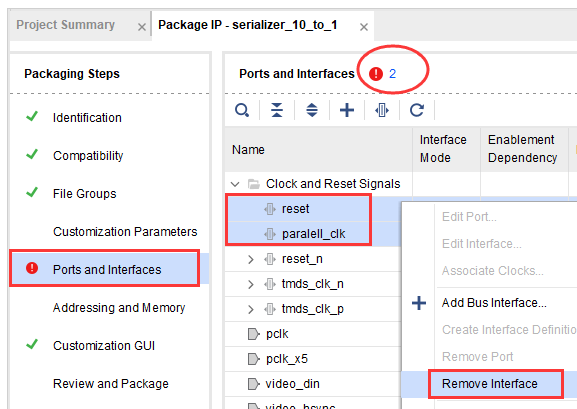

解决办法是将多出来的端口右键移除出接口即可(多出来的 reset、paralell_clk 端口是子模块里面的,不是顶层模块的):

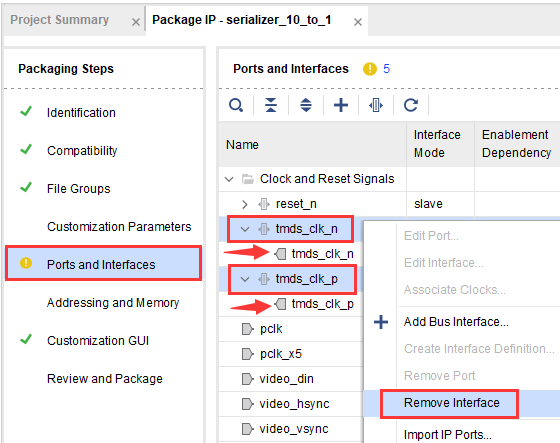

同时 tmds_clk_n 和 tmds_clk_p 这两个端口错误识别成了两个时钟接口,也需要将这两个接口移除,之后再次更新就没有警告报错了。

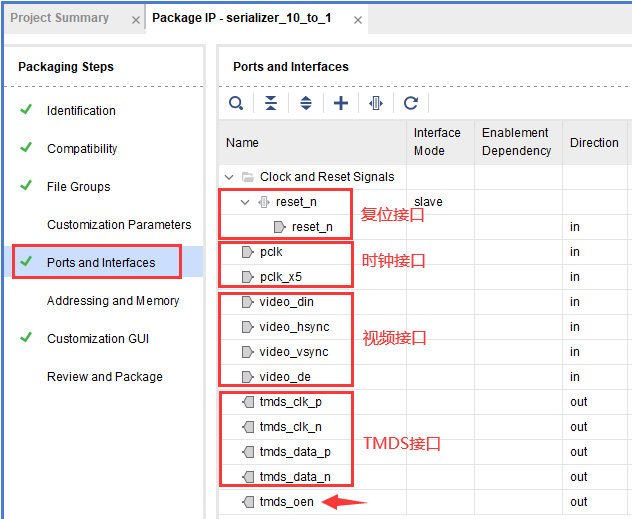

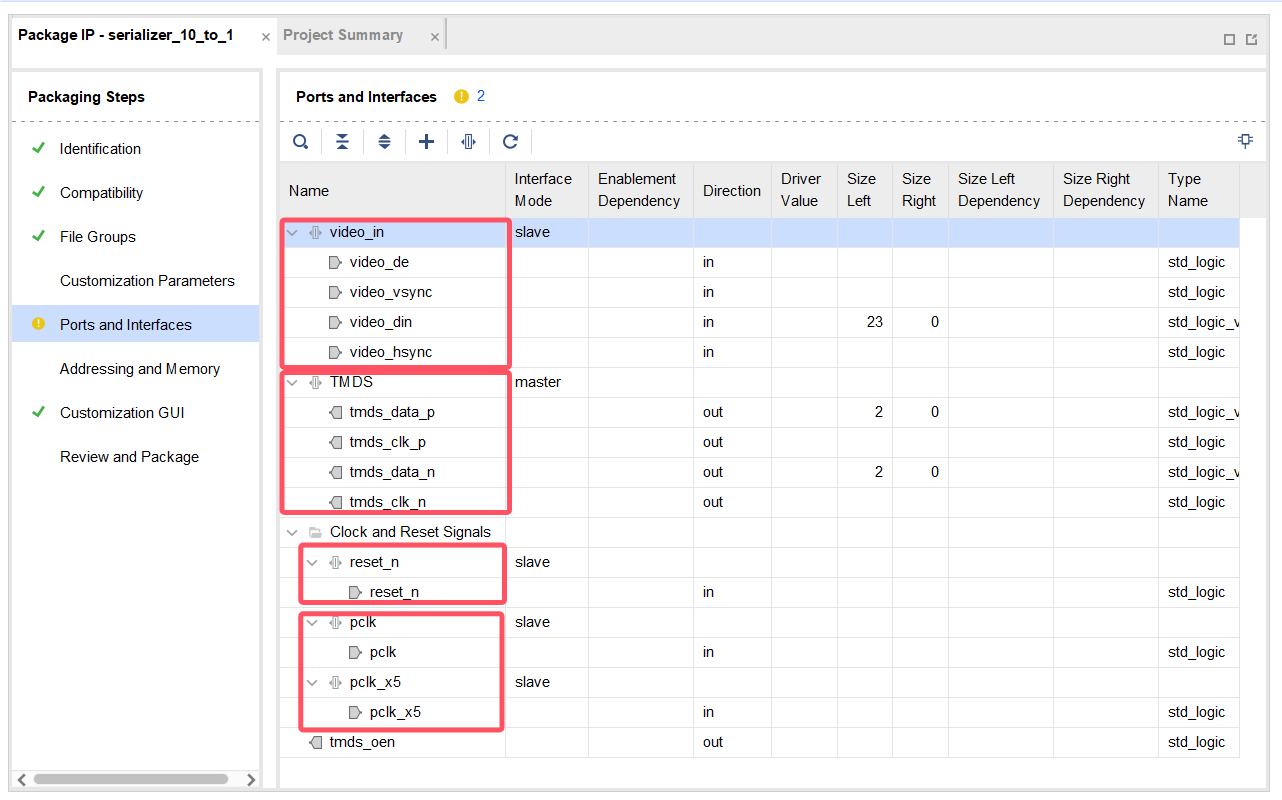

(3.2)将剩余的端口定义成四类端口,IP 核端口与接口界面如下图所示:其中复位接口已经由工具识别到复位信号 reset_n 后自动创建,而其他三个类型的接口需要手动添加。除此之外,tmds_oen 信号没有划分到 TMDS 接口中,而是作为 IP 核独立的端口。

选中对应的端口右键“Add Bus interface”,设置接口定义、名称、模式、端口映射:

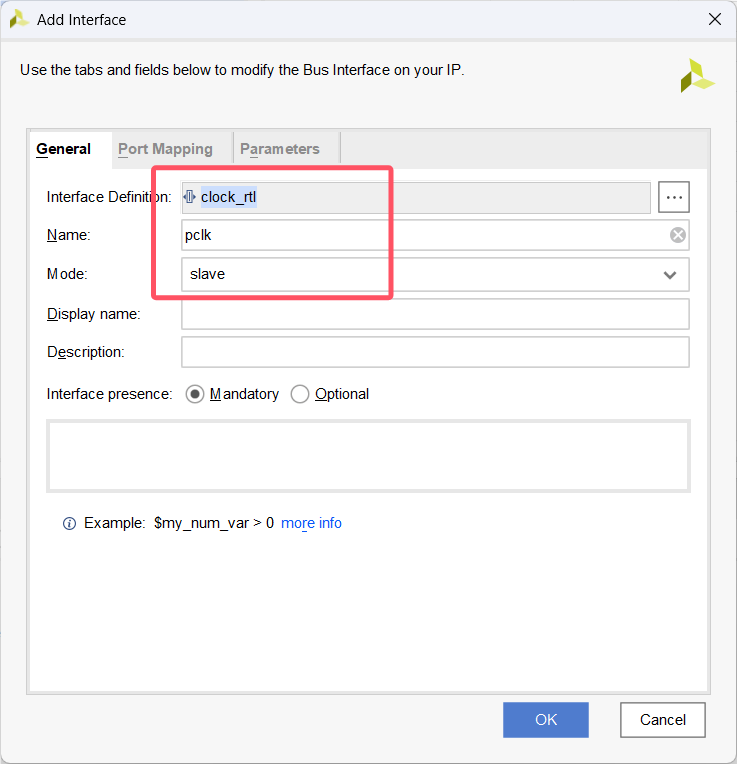

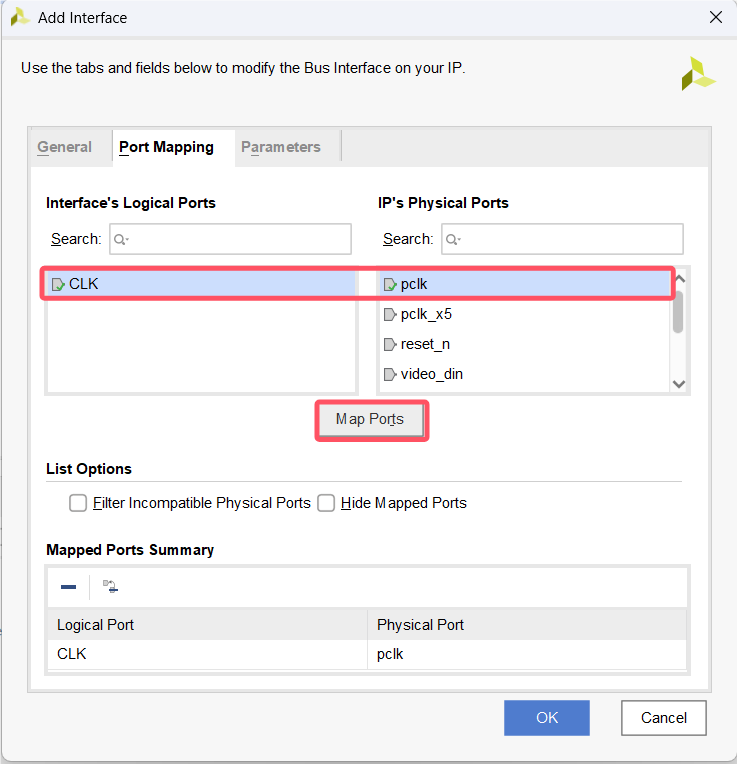

1.pclk接口定义选择已有的 clock_rtl 、同时命名设置模式、完成端口映射(pclk_x5同理)

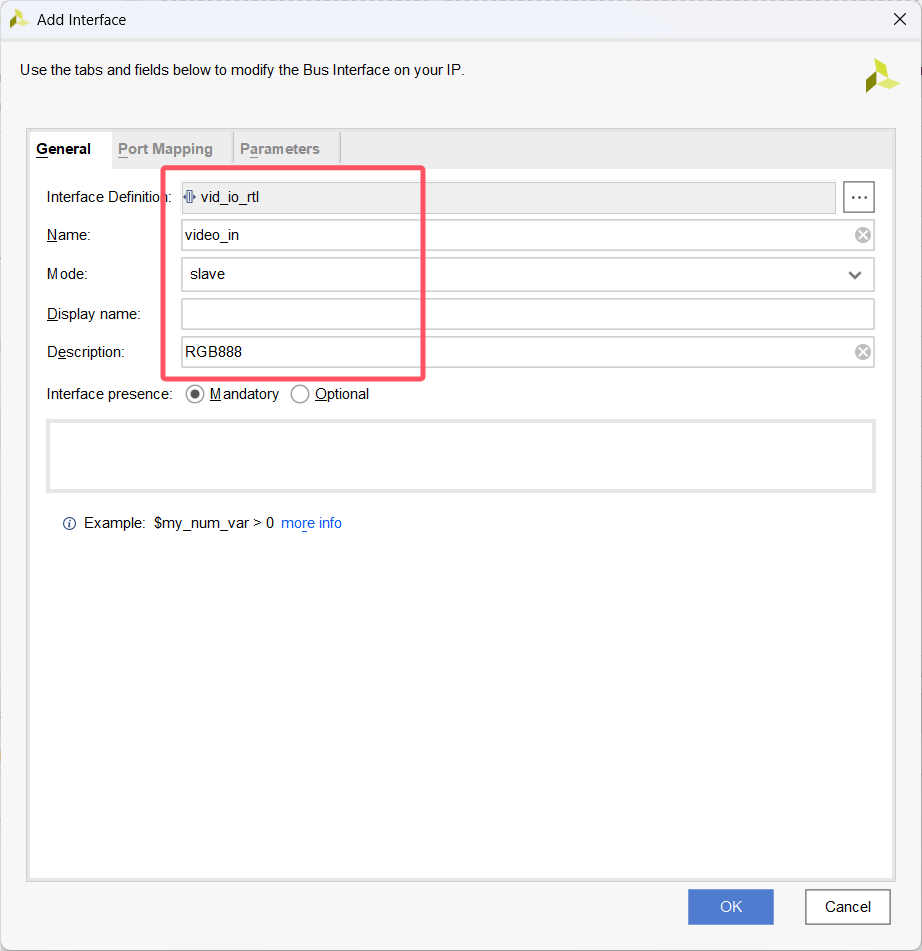

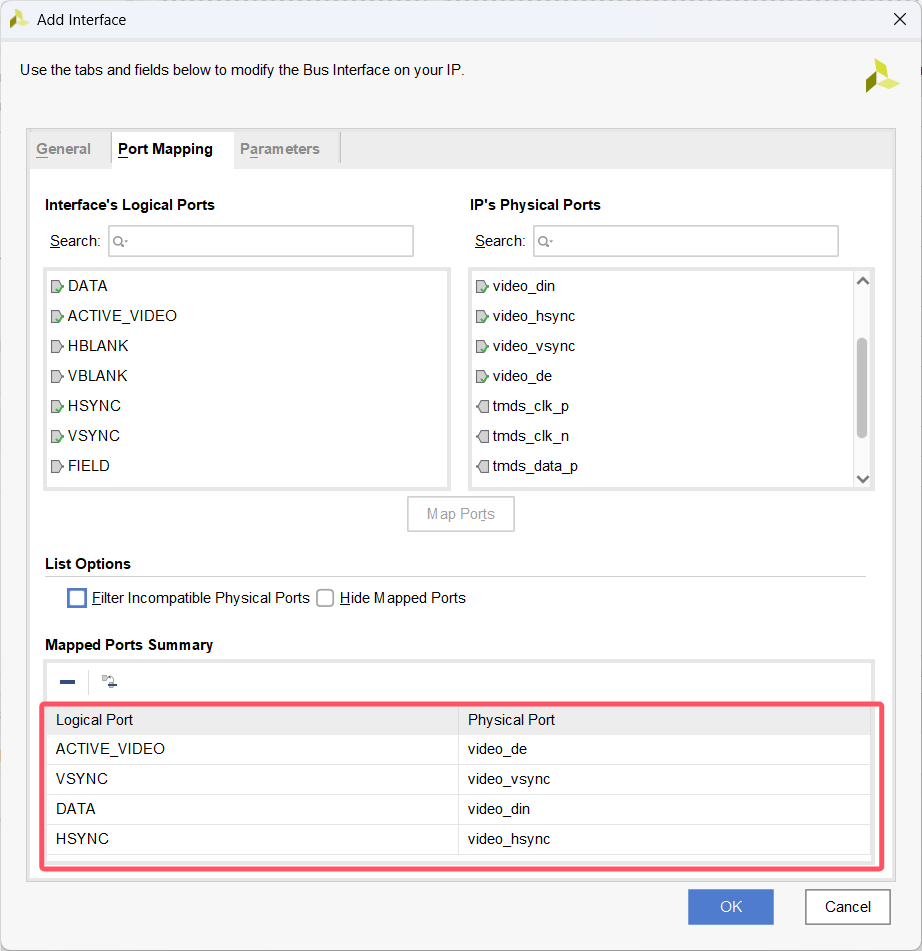

2.video_in接口定义选择已有的 vid_io_rtl 、同时命名设置模式、完成端口映射

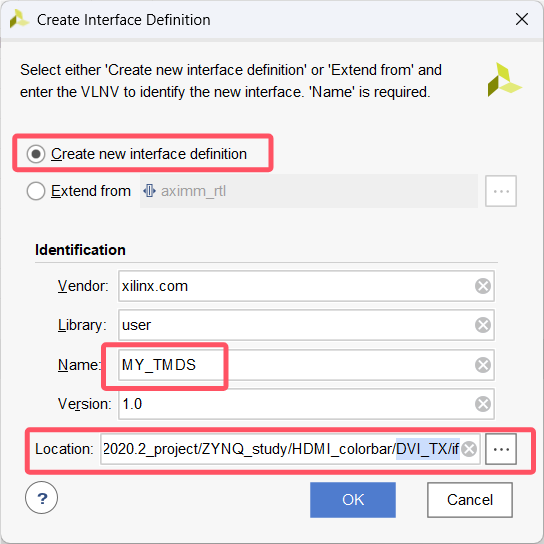

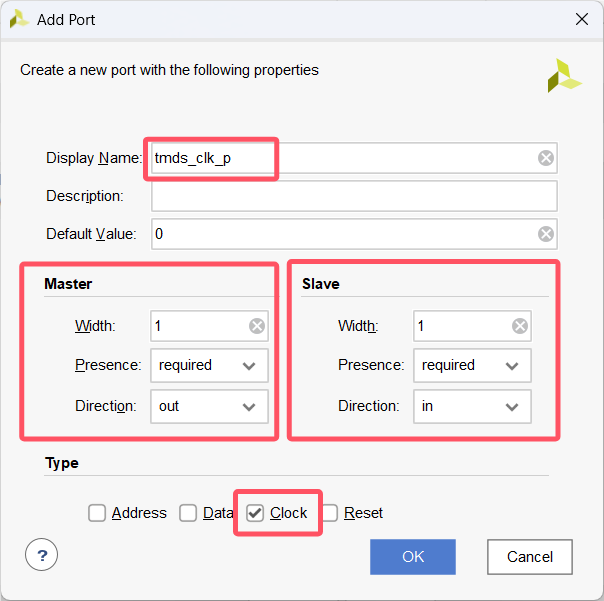

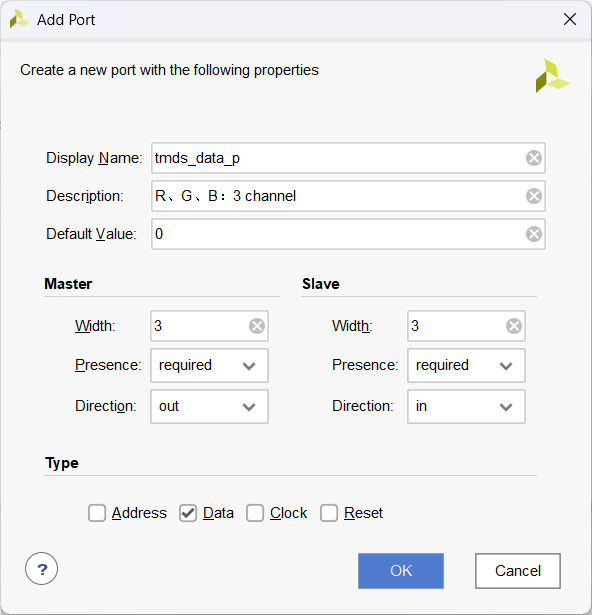

3. tmds 接口需要自定义,因为 Vivado 的 IP 库中并没有这个 TMDS 的接口定义,就自己创建一个,在当前工程中的菜单栏点击“Tools”,然后选择“Create Interface Definition”,选择创建一个新的接口定义、命名为“MY_TMDS”,在弹出来的界面点击加号添加端口定义:

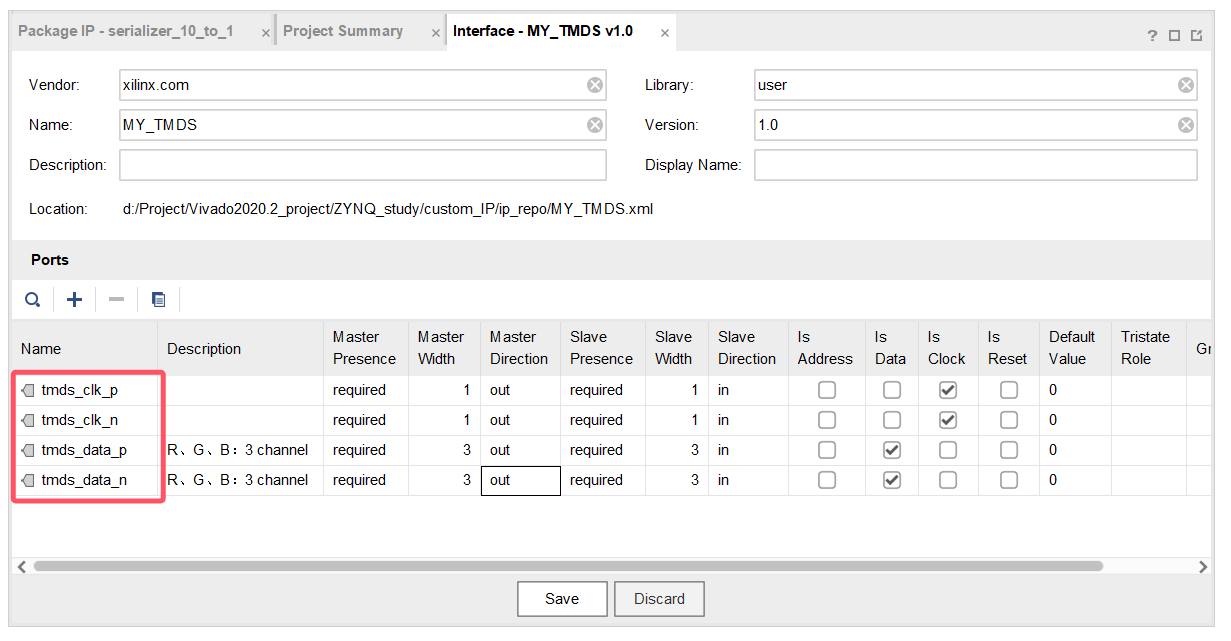

都是差分信号,p和n的参数设置都是一样的,最后的端口定义如图所示,点击Save进行保存。接着再回到封装向导界面对进行tmds的端口进行接口定义即可:

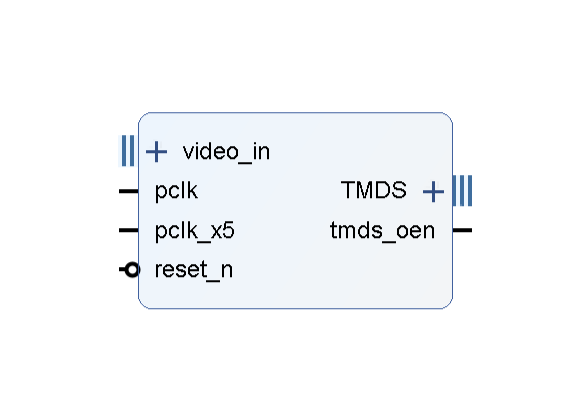

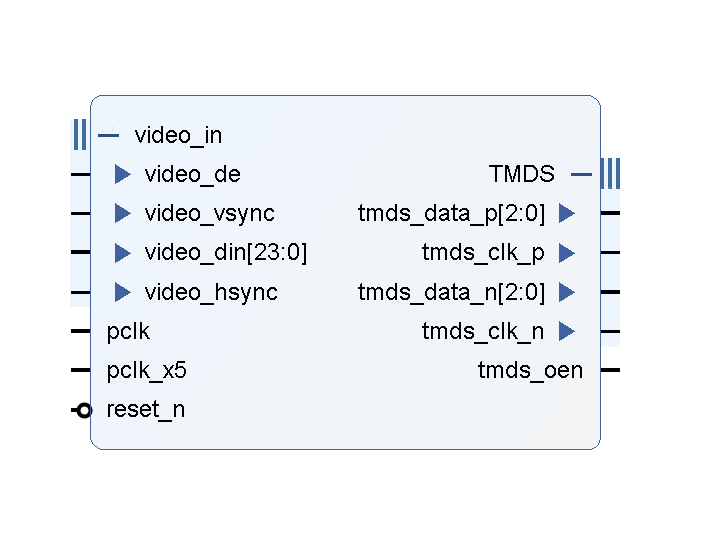

最后端口接口如图所示,到此封装结束,点击最后一栏,点击“打包IP”,完成封装。

GUI视图如图所示:

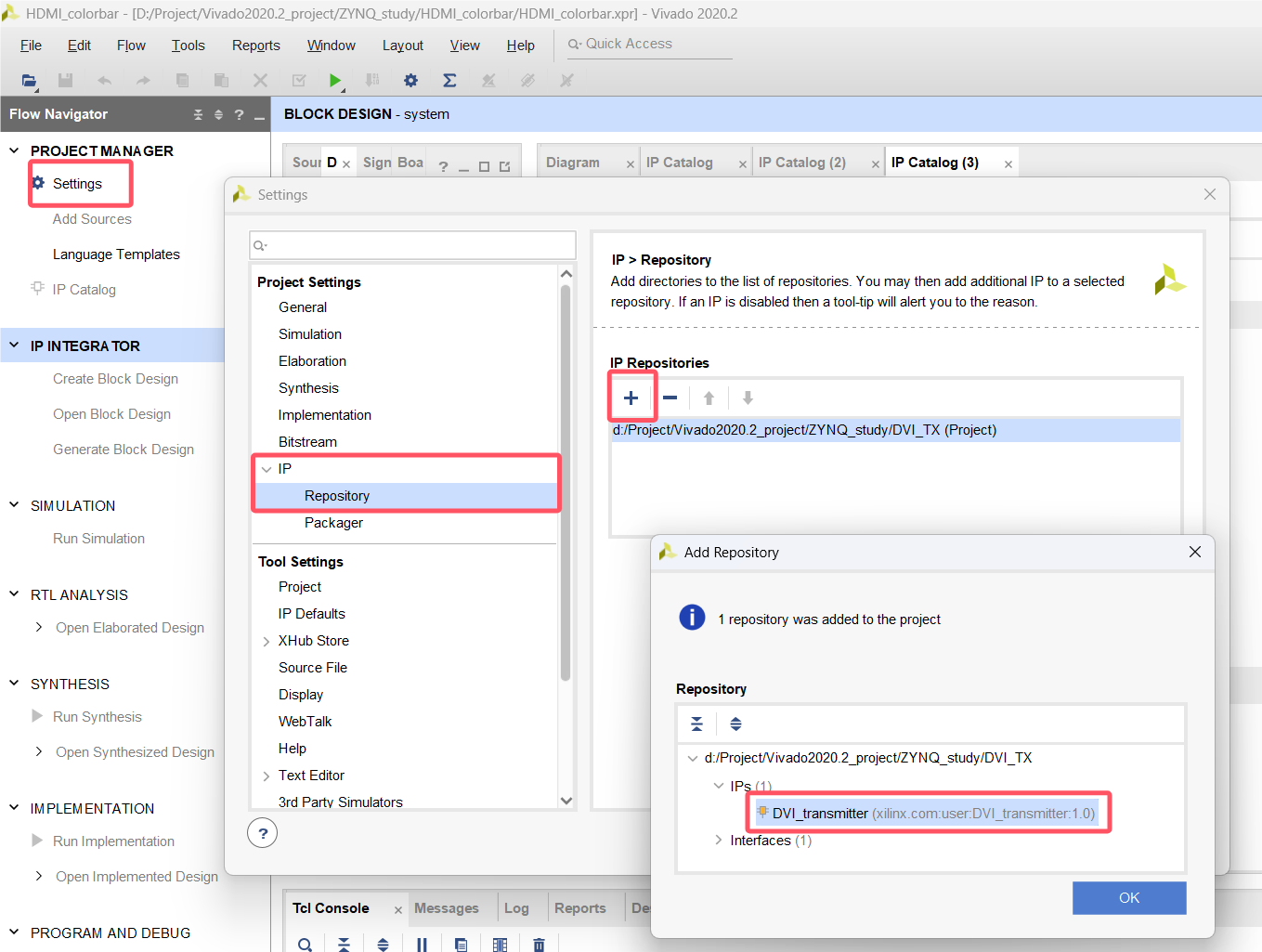

三、使用 IP

设计工程需要使用IP核时,需要添加封装IP的保存路径,这样在IP目录才找到,同时确保芯片型号核IP需要兼容。