芯片软错误概率探究:基于汽车芯片安全设计视角

摘要: 本文深入剖析了芯片软错误概率问题,结合 AEC-Q100 与 IEC61508 标准,以 130 纳米工艺 1Mbit RAM 芯片为例阐述其软错误概率,探讨汽车芯片安全等级划分及软错误对汽车关键系统的影响,分析先进工艺下软错误变化趋势,并提出相应的应对策略,旨在为芯片在汽车等安全关键领域的应用提供理论参考与实践指导,保障电子系统可靠性。

一、引言

随着电子技术在汽车领域的广泛应用,芯片作为核心部件,其可靠性直接关系到车辆的安全性能。其中,软错误这一可靠性问题日益受到关注。软错误是指芯片在运行过程中,因外部环境因素导致其内部存储状态或逻辑状态发生临时性错误,与硬错误不同,软错误并不会造成芯片物理损坏,但可能引发系统功能异常。鉴于汽车应用环境的复杂性与高安全性要求,深入研究芯片软错误概率及其应对措施具有极为重要的现实意义。

二、芯片软错误概率分析

依据 AEC-Q100(汽车电子委员会制定的汽车级集成电路应力测试标准)和 IEC61508(电气 / 电子 / 可编程电子安全系统的功能安全标准)两大权威标准,选取 130 纳米工艺制造的 1Mbit RAM 芯片作为研究对象。研究表明,大气中子单粒子效应引发的软错误概率超过 1000FIT(Failure In Time,定义为在 10^9 小时内出现一次故障即为 1FIT。例如,某器件失效率为 100FIT,则平均预期可安全工作时间为 10^7 小时)。从数值上看,1000FIT 的软错误概率相对较高,尤其对于汽车刹车等安全等级要求极为严苛的应用场景而言,这一概率意味着潜在的巨大安全风险。汽车刹车系统作为车辆安全的关键组成部分,其控制芯片一旦遭受软错误,可能导致刹车指令无法准确执行或延迟执行,从而危及驾乘人员生命安全以及道路行车安全。

三、汽车芯片安全等级划分与软错误关联

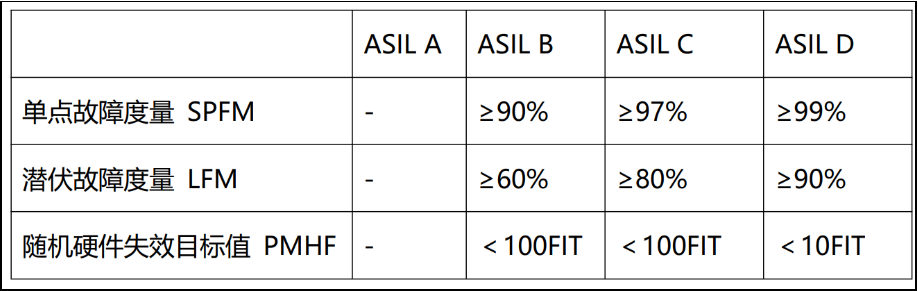

汽车芯片根据其应用场景对应的风险程度,被精细划分为不同安全等级,依次为 QM、ASIL-A、ASIL-B、ASIL-C、ASIL-D,其中 ASIL-D 为最高等级,代表最严格的安全要求。芯片安全等级的划分依据包括三个关键指标的计算,这些指标综合考量了系统故障对人员、环境等可能造成的危害程度。以 130 纳米工艺下的 CMOS 工艺设计为例,当芯片时序存储容量不断增加时,其对安全设计的要求呈指数级增长。1000FIT 的故障率已远超 ASIL-B 的等级要求,这凸显了在先进工艺推进下,芯片软错误问题对汽车芯片安全等级达标构成的严峻挑战,设计者需在芯片架构、电路设计、软件算法等多层面协同优化,以提升芯片的抗软错误能力,确保芯片在全生命周期内符合既定安全等级标准。

四、汽车关键系统对芯片软错误的敏感性

汽车系统的安全等级对所选用的芯片有着明确且严格的要求,尤其是 ASIL-D 等级的动力能源、汽车制动、EBS(电子制动系统)等关键系统,对控制芯片的要求近乎苛刻。以汽车制动系统为例,其对指令的执行精度与时效性要求极高。若芯片出现软错误,导致制动指令 “随机故障”,即制动指令未能按预期执行,后果将不堪设想。驾驶员和乘客将面临着巨大的生命危险,车辆可能因无法及时制动而发生碰撞事故。此外,软错误的来源具有高度不确定性,涵盖大气中子、α粒子、电源电压波动等多种因素,这使得设计者在芯片设计与系统集成过程中,必须全面、系统地考虑每一层级可能出现的软错误,并制定相应的应对方案,构建多层级的容错机制,保障汽车关键系统的可靠性与安全性。

五、先进工艺下芯片软错误趋势

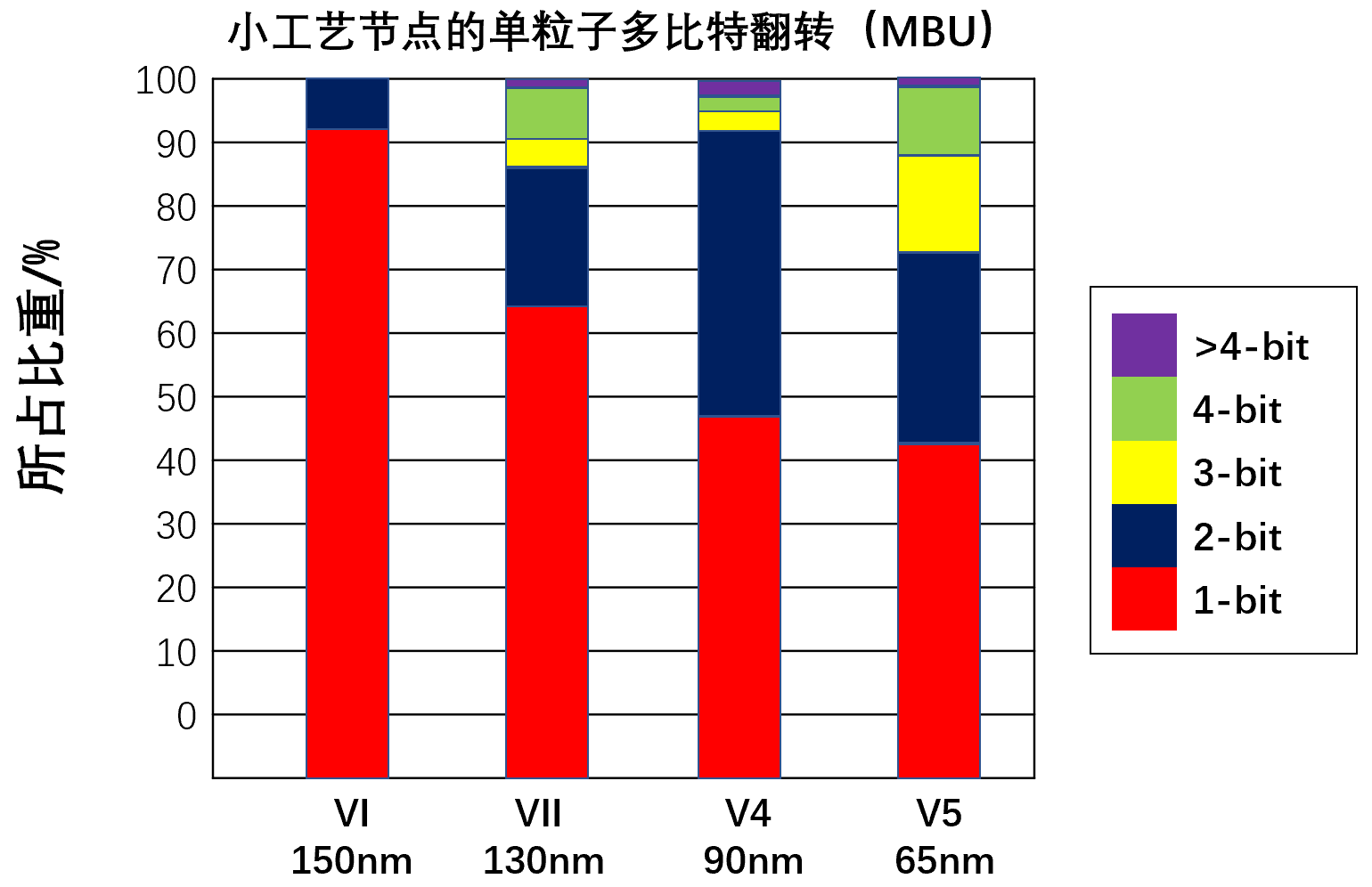

随着半导体制造工艺的不断演进,芯片尺寸持续缩小,当前大多芯片已采用 28 纳米甚至 7 纳米工艺进行生产。然而,工艺的微型化却带来了一个不容忽视的问题 —— 器件的容软错误能力显著下降。在先进工艺下,不仅单比特翻转(SBF)错误概率增加,还出现了更为复杂的多比特翻转(MBU)错误,这进一步加大了故障恢复的难度。研究表明,采用 28 纳米 CMOS 工艺设计的器件相较于 130 纳米工艺器件,在软错误概率上至少高出 3 个数量级。这一趋势对系统的安全性设计提出了前所未有的挑战,迫使芯片设计者与系统工程师必须重新审视传统的可靠性设计方法,探索适应先进工艺的新型软错误防护策略,以平衡芯片性能提升与系统安全性保障之间的矛盾。

六、芯片软错误应对策略

尽管芯片软错误在一定程度上难以完全避免,但这并不意味着芯片无法在众多应用场景中得到有效利用。对于商业级器件和普通工业级器件而言,即使发生软错误,通常可通过简单的重启或复位操作予以消除,且此类故障对人身财产造成的损害风险较低,可接受一定程度的软错误率。然而,对于涉及人民群众生命安全的场景,如汽车安全等级达到 ASIL-D 或工业安全要求达到 SIL-1 的场景,就必须对芯片的软错误特性进行严格评估与控制。

针对器件容软错误的技术方法丰富多样。在太空环境下,器件往往不计成本地在设计与生产环节采取极端冗余、加固等措施以保障任务成功,因太空环境的特殊性与高风险性使得任何微小的故障都可能导致重大任务失败。而对于地面器件,由于其应用场景更为广泛且对成本敏感,在保证安全要求的前提下,追求极致的性价比成为关键目标,这就需要在芯片设计、制造工艺选择、系统架构设计以及软件开发等多个环节进行权衡与优化,综合运用多种软错误防护技术,如错误检测与纠正码(ECC)、冗余设计、时序裕度优化等,以实现芯片在性能、成本与可靠性之间的最佳平衡,满足不同应用场景对芯片软错误特性的差异化要求。例如,国科安芯的AS32A601车规芯片基于自研工艺级软错误防护技术,支持端到端ECC保护。这种设计能够有效检测和纠正存储器中的软错误,从而提高芯片的可靠性。此外,该芯片还集成了硬件加密模块,支持AES、SM2/3/4和TRNG等加密算法,能够有效防止数据在传输过程中被篡改或窃取。

七、结论

芯片软错误概率是影响汽车芯片乃至各类电子产品可靠性的重要因素。通过对 130 纳米工艺 1Mbit RAM 芯片的分析,结合汽车芯片安全等级划分以及先进工艺下软错误趋势的探讨,深刻认识到芯片软错误问题的复杂性与严峻性。在汽车智能化、电动化、网联化快速发展的当下,芯片作为核心支撑,其软错误防护技术研发与应用至关重要。未来,随着芯片制造工艺的持续进步,软错误问题将进一步凸显,需要芯片设计者、系统集成商、标准制定机构以及科研人员等各方协同合作,不断探索创新的软错误应对策略与解决方案,从芯片架构设计、制造工艺改进、系统容错机制构建以及软件算法优化等多维度入手,全面提升芯片的抗软错误能力,确保汽车电子系统以及其他关键应用电子系统的稳定、可靠运行,为人们的出行安全以及社会的数字化发展提供坚实的技术保障。