优化PCB Via Stub系列(1):一次学会利用层叠设计降低Via Stub损耗

开路谐振对SI而言真不是个好东西,这种1/4波长谐振会带来讯号的驻波,进而降低整体通道带宽,导致SI不佳! 在高速PCB设计中,最常发生的1/4波长谐振就属过孔的Via stub,这个小小的金属残段可以酿成大大的SI问题,实务上我们要怎么避免或是说享受与其共存呢?

大致上有几种方法可以解决这个问题!

- 叠构设计

- 背钻(Backdrill)

- U-turn layout design

- B/B Via 的使用

这篇文章我们先讲叠构设计,通过走线层安排以解决Via stub带来的不良影响!

高速通道初期规划 – 通道损耗分析

在规划高速PCB时,如果能在前期就把走线层面安排得井井有条,就能避免很多后续的麻烦,也不用在制造工艺上花大钱做特殊处理,是我们认为最经济实惠的设计选择。

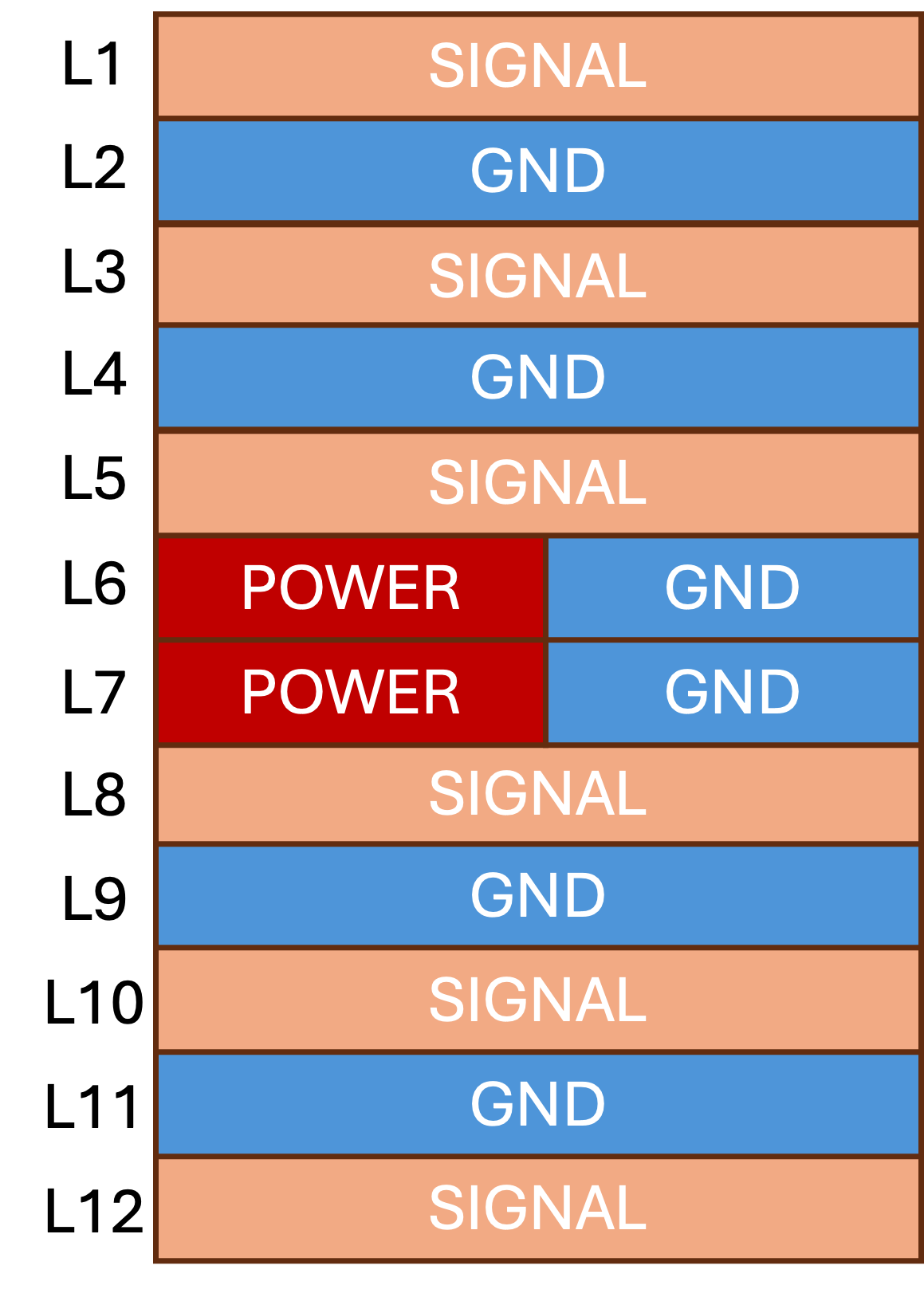

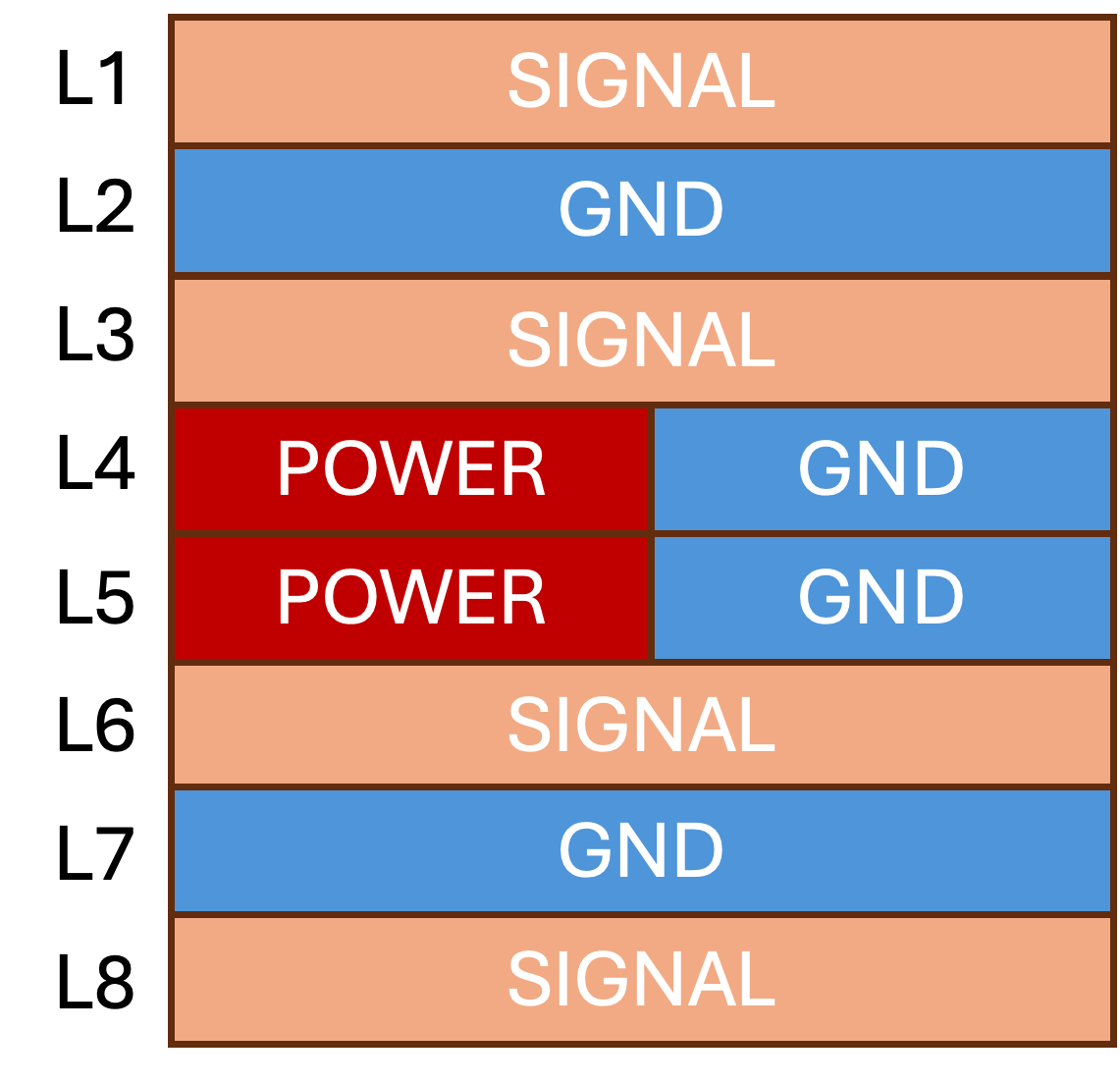

这里举个经典的八层板为例:把L1、L3、L6、L8当作主要讯号层,L2、L7作为Ground,然后L4、L5为Power与Ground的混合。

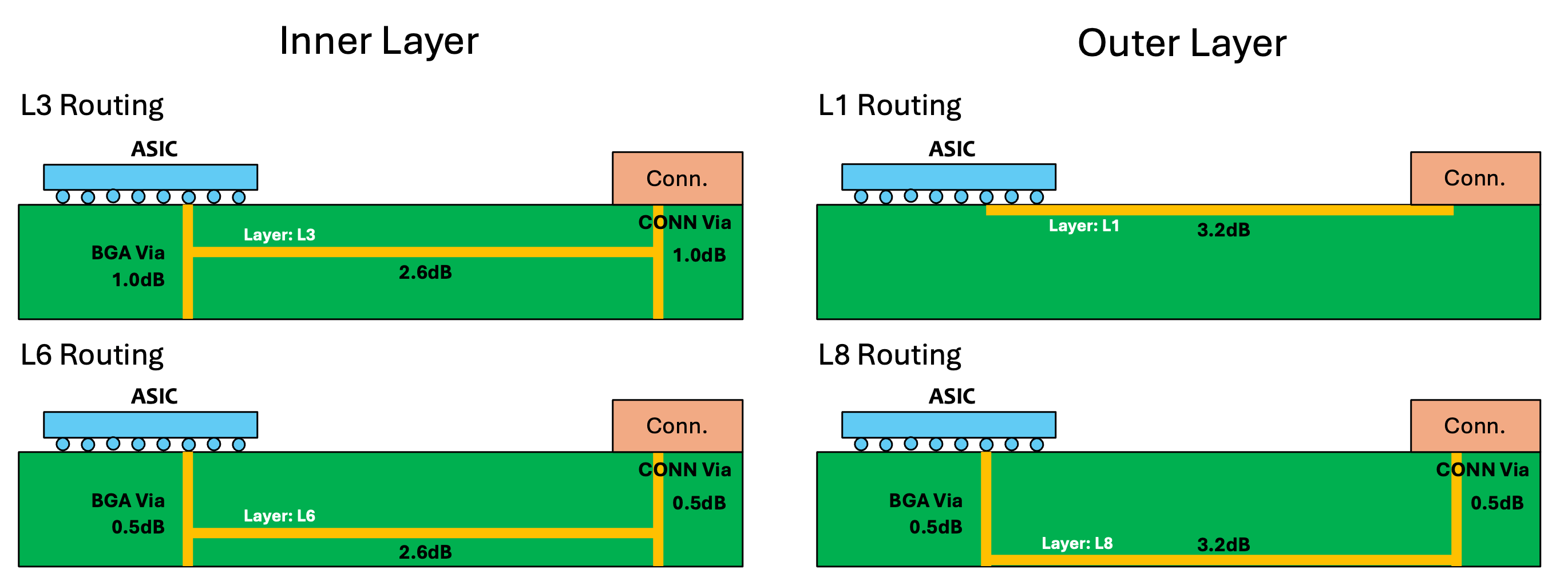

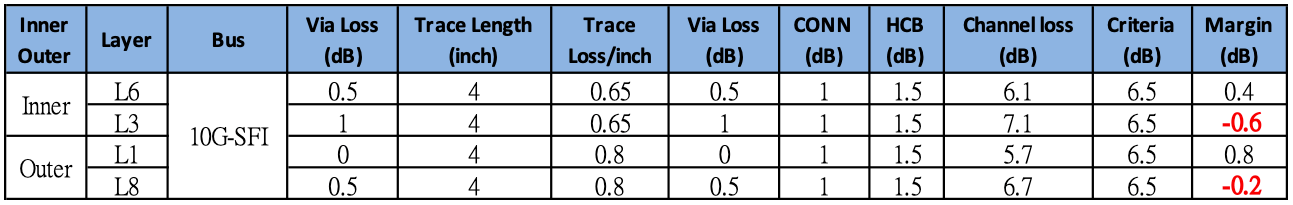

在进行初期SI评估的时候,我们通常不会一下子就确定所有走线层的配置,而是会先把这四个走线层面的情况分别列出来,逐层进行细部的评估,就像下面表格所呈现的方式。 这样的做法能够让我们更清楚地看到每一层走线对整体通道损耗的影响,也能更直觉地比较不同方案之间的差异性和优劣之处。

当我们通过这样分层的方式整理并分析数据后,就能从中找出最佳的走线配置,确保选定的方案能够带来最低的信号损耗。 接下来,我们再将这个筛选出来的设计提案与Layout设计团队进一步讨论,评估实际布局的可行性与困难点。

表层出线

表层出线在这个8层板的例子中,又分成L1出线与L8出线,或是说Top层与Bottom层出线。 我们先来分析走线损耗,再来看走线损耗与过孔损耗的搭配关系。

表层损耗概述

通常,表层(Microstrip)的PCB损耗会大过内层(Stripline),有几个原因:

电镀与表面处理导致铜箔粗糙度下降

在实际制作PCB时,过孔内的孔壁需要透过电镀的方式镀上一层金属来形成导电路径。 但电镀这个动作是没有办法选择性地只处理孔壁而避开其他区域的,所以原本放置在表层的铜箔也会被额外地镀上一层金属,所以有设计过叠构的各位你们会发现PCB厂都会写类似0.5oz+plating。 此外,表层之后还会再进一步进行表面处理,例如OSP或ENIG等,这些处理程序同样会对铜箔表面的粗糙度产生明显影响。 因此,实务上并不建议在表层使用好铜箔,因为经过电镀和表面处理后,原本好铜箔表面的光滑度会大幅降低,导致表面变得粗糙,最终增加了讯号传输时的铜箔损耗,讯号完整性也随之变差。

复合介质导致色散

表层的情况会比内层复杂许多,因为内层通常只会有一种介质,而表层基本就一定包含三种介质,除了CCL材料以外,还有Soldermask(SM)以及空气。 这三种介质各自有着不同的物理特性(DK/DF),特别是在高频下,它们对电磁波的反应不尽相同,就像每个材料都有自己专属的“截止频率”(Cut-off Frequency)。 当电磁波的频率接近或超过这个值时,该材料会显著改变信号的传播特性,例如吸收部分能量或改变传输速度。

由于表层同时包含三种材料,电磁波在这里传播时就必须同时“过关斩将”这三道不同的关卡。 结果,不同频率成分的信号就会因为各自受到的影响不同而产生传播速度上的差异,这种现象称为色散。 色散会导致信号中的高频与低频部分出现不同的延迟,使得原本整齐的波形变得模糊或失真。

表层出线搭配过孔配置

以表层出线来说,第一层走线具有明显优势,主要在于它不必经过PCB过孔,以一般两颗过孔的结构来看,可以省下约1dB的损耗,虽然表层的损耗较大,但是透过减少过孔数量,也是可以在短通道上(大约5 inch内)得到较佳的损耗特性。

不过第一层出线其实在执行面上不是那么容易,因为通常L1会有较多的元件挡住高速走线通道,导致难以找到适合高速讯号传输的干净走线区域。 所以更常做的是透过过孔将走线丢到L8去,当然这是不好的,除了要扛下较差的表层损耗,还要吃下两颗过孔的损耗,造成通道余裕不够,这时就得考量是否更换较好的材料,或是再将走线缩短又或是改到内层去!

况且除了损耗外的另一个原因,是表层有着较严重的Crosstalk现象,而内层对于这种Far-end crosstalk而言,是趋近于0或是说不受Crosstalk影响的,我们在这篇文章中有提到,所以这会使得绝大多数的高速讯号都被建议走在内层!

内层出线

内层出线的好处就很多了,有较优异的PCB制程管控,让损耗可以更小,还拥有较佳的Crosstalk效应,绝对是高速讯号设计首选,不过这世界真的没有100%好的,要能达到所有高速走线都走内层,大概还有两个缺点:

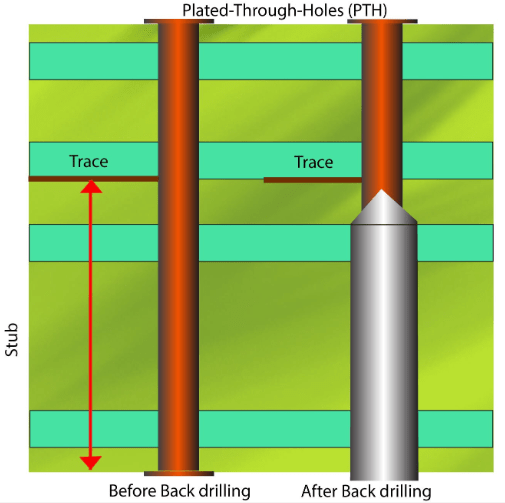

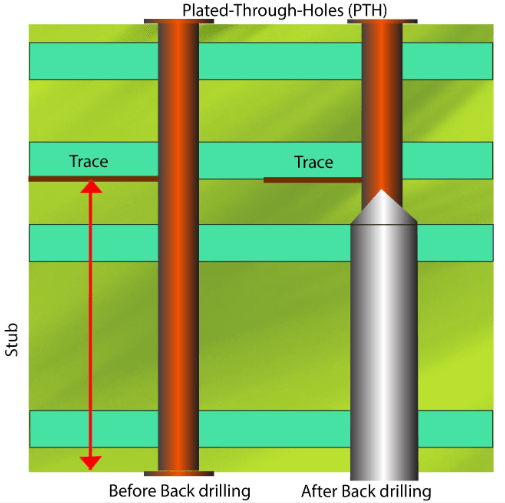

产生Via Stub

当我们使用机械钻孔的PCB来走内层信号时,难免一定会产生Via Stub的问题,我们能做的是尽量将Via stub控制的越短越好,这当然可以通过背钻技术控制Via stub在12mil内(现在最佳的能力在5mil),但是由于多一道PCB制程工艺,加钱无可避免,在一些中低阶产品中(例如10G/25G Router),因为这些产品本来利润就不高,多花一点成本就会明显压缩产品的毛利率。 因此我们在设计此类产品都会尽可能避免使用背钻。

除了背钻外,我们也可以透过将走线层控制在越低的层面,以得到更加的损耗控制,例如以这个8层板为例,走线可以在L6,这样Via stub只会出现在L6-L8这个长度(大概10-15mil),以中低端产品来讲,这个长度还不至于引起剧烈的损耗变化。

而如果在L3出线,与L6相同,会得到较佳的PCB走线损耗,可是较长的Via stub(以1.6mm板厚而言,大约40-50mil),会使得单颗过孔损耗从0.5dB上升至1.0dB,两颗过孔就增加了1dB,严重影响SI特性。

需要更多PCB层面

由于成本管控,大家还是会希望走线利用率能越高越好,尽量压缩PCB层数,可以将成本控制的越低。

高速SerDes走线会有TX跟RX信号,这两种信号不建议走在同一层,因为这会导致严重的Near-end Crosstalk(NEXT),尤其对内层而言,NEXT的影响理论上是外层的两倍大,换句话说,SerDes的走线层面至少需要两层!

以这种8层板来看,最经济的方式是走在L6与L8,完全不需要采取背钻技术,成本较优。 可是如果L8无法满足通道损耗要求,则两条路:第一是利用L3走线,并做背钻; 第二,加PCB层数至12层,将走线设计在L8与L10,虽然L8的Via stub会落在20几mil,可以透过3D电磁仿真软件,例如Cadence Clarity,分析一下是否可行,以我们的经验来讲这差异对于中低阶产品而言是不构成威胁的!