驱动开发硬核特训 · Day 24(上篇):走进Linux内核时钟子系统 —— 硬件基础全解析

一、前言

在 SoC(System on Chip)设计中,“时钟(Clock)”不仅是信号同步的基石,也是各个模块协调运作的前提。没有合理的时钟体系,CPU无法运行,外设无法通信,存储器无法读写。

Linux内核中,时钟子系统(Clock Subsystem)承担了统一管理硬件时钟资源的重要角色。要真正理解Linux内核的时钟子系统,必须先理解——底层硬件中的时钟控制器是如何构建的,它们解决了什么问题,提供了什么能力。

今天,我们将系统梳理时钟控制器硬件基础,从原理到组成,从具体示例到实际应用,一步步打好坚实基础,为明天学习内核软件架构做准备。

二、时钟控制器的本质:为什么需要它?

在现代SoC芯片中,通常集成了成百上千个模块。

每个模块都需要时钟信号才能正常工作,但不同模块对时钟的要求千差万别:

- CPU需要高速高稳定的时钟(如2GHz)

- UART串口只需要低速时钟(如115200bps)

- I2C控制器需要400kHz甚至1MHz

- GPU、VPU需要动态可变的高频时钟以适配性能需求

- 某些模块休眠时还需要极低功耗的时钟支持(如RTC)

如果每个模块独立产生自己的时钟,不仅芯片面积庞大、能耗剧增,而且管理混乱,难以同步。

因此,必须要有一个统一的“时钟源管理系统”——这就是**时钟控制器(Clock Controller)**存在的意义。

时钟控制器统一:

- 生成(产生时钟源)

- 配置(调整时钟频率)

- 分配(提供给不同模块)

- 控制(动态开关、节能管理)

它是系统大脑的节奏大师,管理整个芯片内部的节拍与律动。

三、时钟控制器硬件组成详解

一个完整的时钟控制器,通常包含以下基本模块:

1. 基础时钟源(Clock Sources)

-

晶体振荡器(Oscillator, OSC)

提供稳定的基准频率,如24MHz、32.768kHz等。 -

锁相环(Phase-Locked Loop, PLL)

将低频振荡器信号倍频成高频信号,例如24MHz通过PLL产生2.4GHz。

示例(i.MX8MP SoC):

- 24MHz OSC → System PLL(输出1GHz)

2. 时钟选择器(Clock Mux)

- 用于选择时钟源,比如CPU既可以用低功耗PLL,也可以用高性能PLL。

- 硬件上是多路复用器(MUX)。

示例(i.MX8MP CCM模块):

- CPU_CLK_ROOT 可以从 ARM_PLL 或 SYSTEM_PLL 分频器选择。

3. 时钟分频器与倍频器(Divider/Multiplier)

- 分频器(Divider):将输入时钟除以一个整数,得到低速时钟。

- 倍频器(Multiplier):将输入时钟乘以一个整数,得到更高速的时钟(较少使用)。

示例:

- 1GHz → 分频2 → 500MHz(供AXI总线)

4. 时钟门控(Clock Gating)

- 硬件开关,允许/禁止时钟信号向下游模块传输。

- 用于功耗优化,不用的模块关闭时钟以节能。

示例:

- 禁用I2C2模块时,关闭I2C2的根时钟。

5. 动态时钟调整(DVFS支持)

- 支持动态改变PLL参数或选择不同时钟源,来调整CPU、GPU频率,达到性能/功耗动态平衡。

- 与电源管理系统协同工作。

示例:

- CPU从1GHz降频至400MHz以节能。

6. 时钟域(Clock Domains)

- 每个时钟源及其分支形成一个独立时钟域。

- 跨时钟域通信时,需要同步逻辑防止亚稳态(如双触发器同步器)。

四、时钟控制器在SoC中的实际应用举例

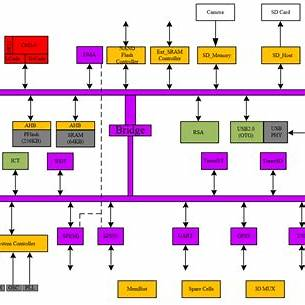

以 NXP i.MX8M Plus 这颗流行的SoC为例:

| 模块 | 典型时钟源 | 管理方式 | 特点 |

|---|---|---|---|

| CPU核 | ARM_PLL | 可动态调整频率 | 支持频率调节 |

| GPU | GPU_PLL | 高速、低延迟 | 动态频率调整 |

| DDR控制器 | SYSTEM_PLL_PFDx | 固定频率 | 高带宽稳定性 |

| I2C控制器 | OSC分频 | 固定频率 | 低速,功耗低 |

| USB控制器 | USB_PLL | 高速同步 | 与PHY紧耦合 |

| UART串口 | OSC/PLL分频 | 可选不同频率 | 适配不同波特率 |

| Audio子系统 | AUDIO_PLL1/2 | 高精度同步 | 支持低抖动 |

可以看到,不同模块需要不同源、不同频率、不同控制能力,时钟控制器必须高度灵活、细粒度可控。

五、时钟控制器的硬件寄存器结构

通常,一个时钟控制器(比如 i.MX8MP的 CCM)寄存器结构大致包括:

| 模块 | 寄存器功能 |

|---|---|

| PLL配置寄存器 | 配置倍频因子、分频因子 |

| MUX控制寄存器 | 选择时钟源 |

| Divider寄存器 | 设置分频系数 |

| Gating控制寄存器 | 开关各个模块的时钟 |

| 时钟状态寄存器 | 查询时钟有效性 |

每种配置一般对应一组固定地址寄存器,由时钟控制器硬件提供,内核驱动通过寄存器操作完成配置。

六、时钟控制器与低功耗设计

时钟管理直接关系到SoC的功耗控制:

- 模块休眠时关闭对应时钟

- 动态调整频率降低动态功耗

- 在芯片待机状态,只保留最基本的RTC或Wakeup Clock

时钟门控和**动态频率调整(DVFS)**成为现代低功耗芯片设计不可或缺的一部分。

七、总结:硬件角度下的时钟体系

时钟控制器解决了什么问题?

- 统一时钟源

- 按需分配频率

- 动态节能控制

- 保证模块时序同步

它的基本构成包括?

- 时钟源(OSC、PLL)

- 时钟选择(MUX)

- 时钟变换(Divider)

- 时钟开关(Gating)

- 时钟域管理(Clock Domain)

对系统的重要性?

- 没有合理时钟,整个芯片无法运转

- 时钟管理直接影响性能、功耗、可靠性

八、思考与预告

通过今天的学习,我们从硬件原理上彻底理解了:

- 为什么需要时钟控制器

- 时钟控制器由哪些模块组成

- 时钟控制器在SoC中的实际应用

明天(Day 24下篇),我们将正式进入Linux内核层面:

- 时钟子系统在Linux内核中的软件框架

- 关键结构体和接口(如

clk,clk_hw) - 驱动实现流程与设备树绑定关系

只有打好了硬件基础,才能真正深入理解Linux内核时钟子系统的设计哲学。