【EDA软件】【设计约束和分析操作方法】

1. 设计约束

设计约束主要分为物理约束和时序约束。

物理约束主要包括I/O接口约束(如引脚分配、电平标准设定等物理属性的约束)、布局约束、布线约束以及配置约束。

时序约束是FPGA内部的各种逻辑或走线的延时,反应系统的频率和速度的约束。

2. 物理约束

在Vivado中,物理约束通常是在*_pins.xdc文件实现,这也是推荐的使用方法。

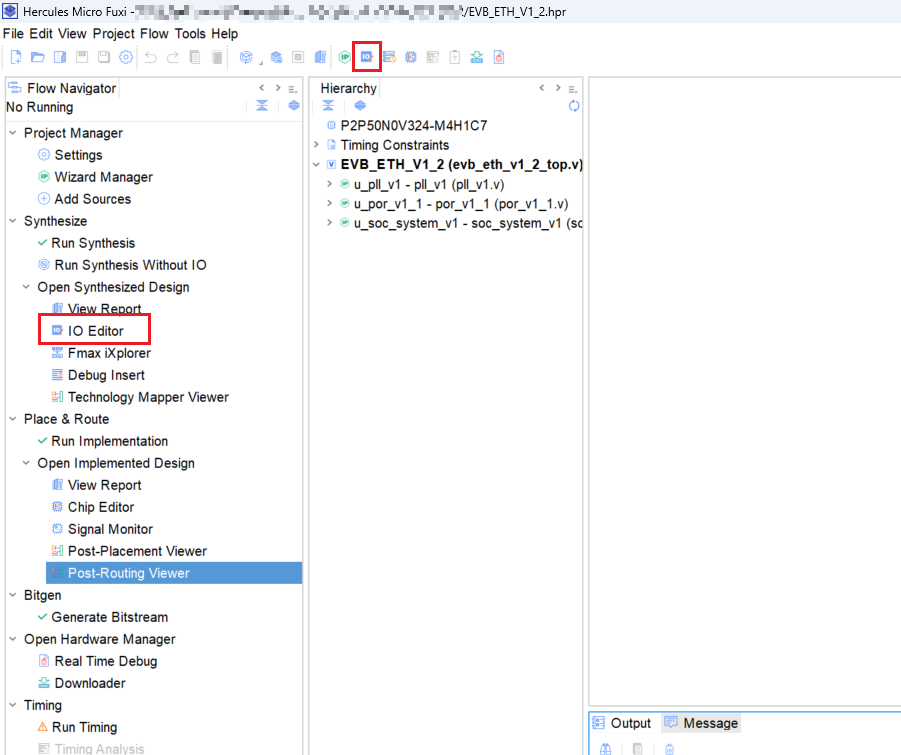

FUXI软件有专用的IO GUI界面,暂不支持手动编译。点击IO Editor,如下图所示。

注意:和Vivado类似,需要先完成Systhesize。

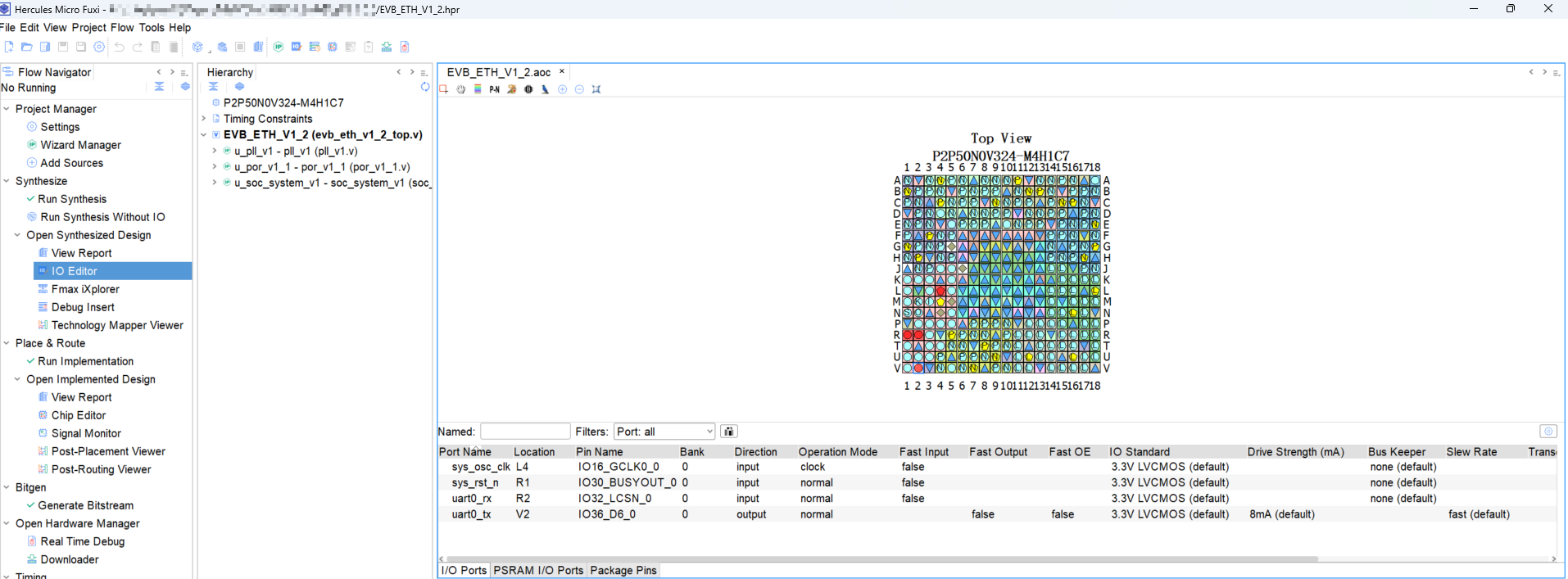

软件会打开*.aoc文件,根据硬件设计选择Pin Name,IO Standard等。

*.aoc文件内容:

<?xml version="1.0" encoding="UTF-8"?>

<aoc version="2.3" device="P2P50N0V324-M4H1C7"><ioConstraint><IO signal_name="sys_osc_clk" pad_name="io16_dmux5_clk0" location="IO16_GCLK0_0" pin_no="L4" inst_name="io_sys_osc_clk_inst" direction="input" operation_mode="clock"/><IO signal_name="sys_rst_n" pad_name="io30_busyout" location="IO30_BUSYOUT_0" pin_no="R1" inst_name="io_sys_rst_n_inst" direction="input" operation_mode="normal"/><IO signal_name="uart0_rx" pad_name="io32_lcsn" location="IO32_LCSN_0" pin_no="R2" inst_name="io_uart0_rx_inst" direction="input" operation_mode="normal"/><IO signal_name="uart0_tx" pad_name="io36_d6_dmux10" location="IO36_D6_0" pin_no="V2" inst_name="io_uart0_tx_inst" direction="output" operation_mode="normal"/></ioConstraint>

</aoc>3. 时序约束

在Vivado中,物理约束通常是在*_timing.xdc文件实现,这也是推荐的使用方法。

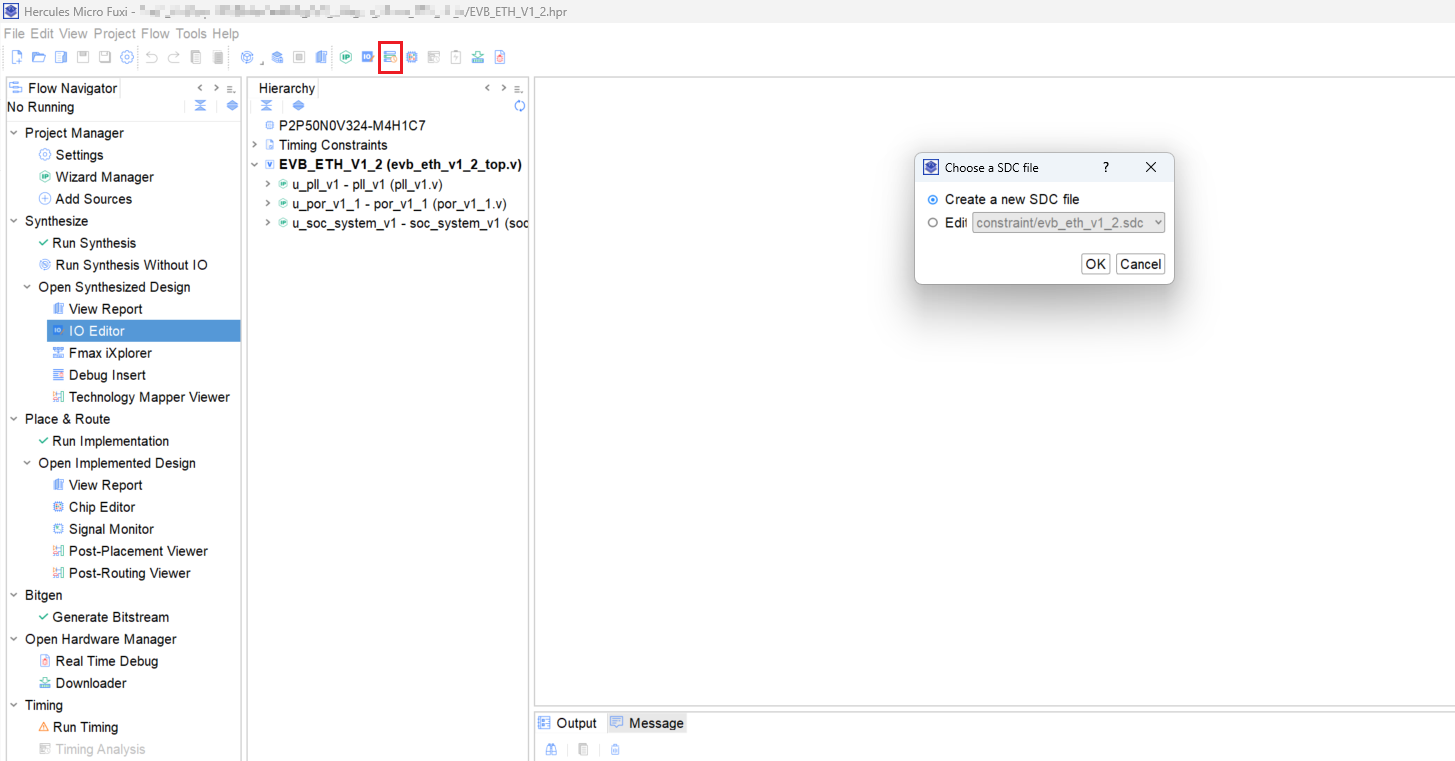

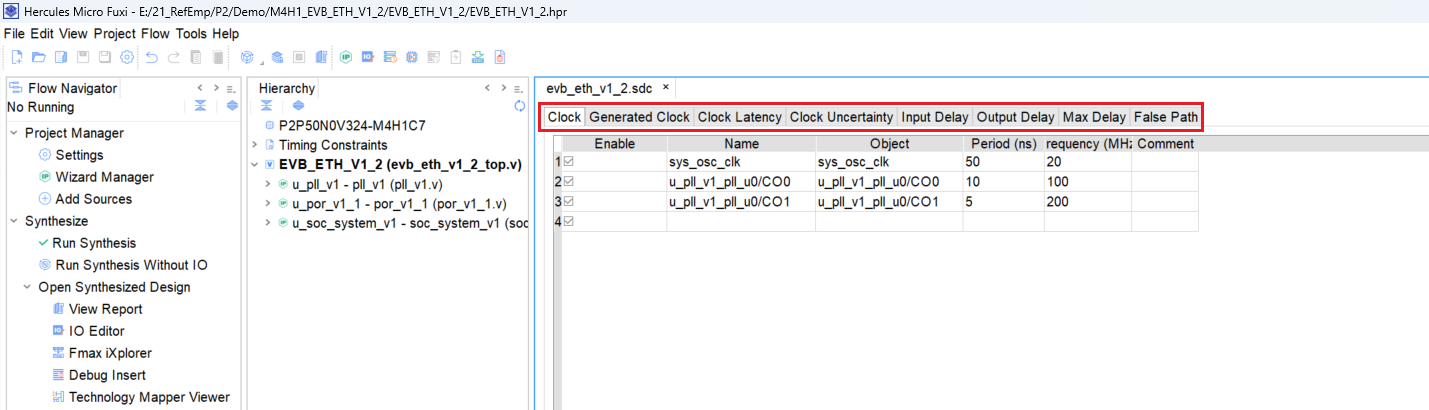

FUXI软件有专用的Timing Contrains GUI界面,不推荐手动编译。点击Timing Contrains Editor,如下图所示。

从上图可以看到,已经包含业界常使用的约束命令。

*.sdc文件内容:

create_clock -period 50 -name {sys_osc_clk} [get_ports {sys_osc_clk}]

create_clock -period 10 -name {u_pll_v1_pll_u0/CO0} [get_pins {u_pll_v1_pll_u0/CO0}]

create_clock -period 5 -name {u_pll_v1_pll_u0/CO1} [get_pins {u_pll_v1_pll_u0/CO1}]

set_false_path -from [get_clocks {sys_osc_clk}] -to [get_clocks {u_pll_v1_pll_u0/CO0}]

set_false_path -from [get_clocks {sys_osc_clk}] -to [get_clocks {u_pll_v1_pll_u0/CO1}]

set_false_path -from [get_clocks {u_pll_v1_pll_u0/CO0}] -to [get_clocks {sys_osc_clk}]

set_false_path -from [get_clocks {u_pll_v1_pll_u0/CO1}] -to [get_clocks {sys_osc_clk}]4. 时序分析

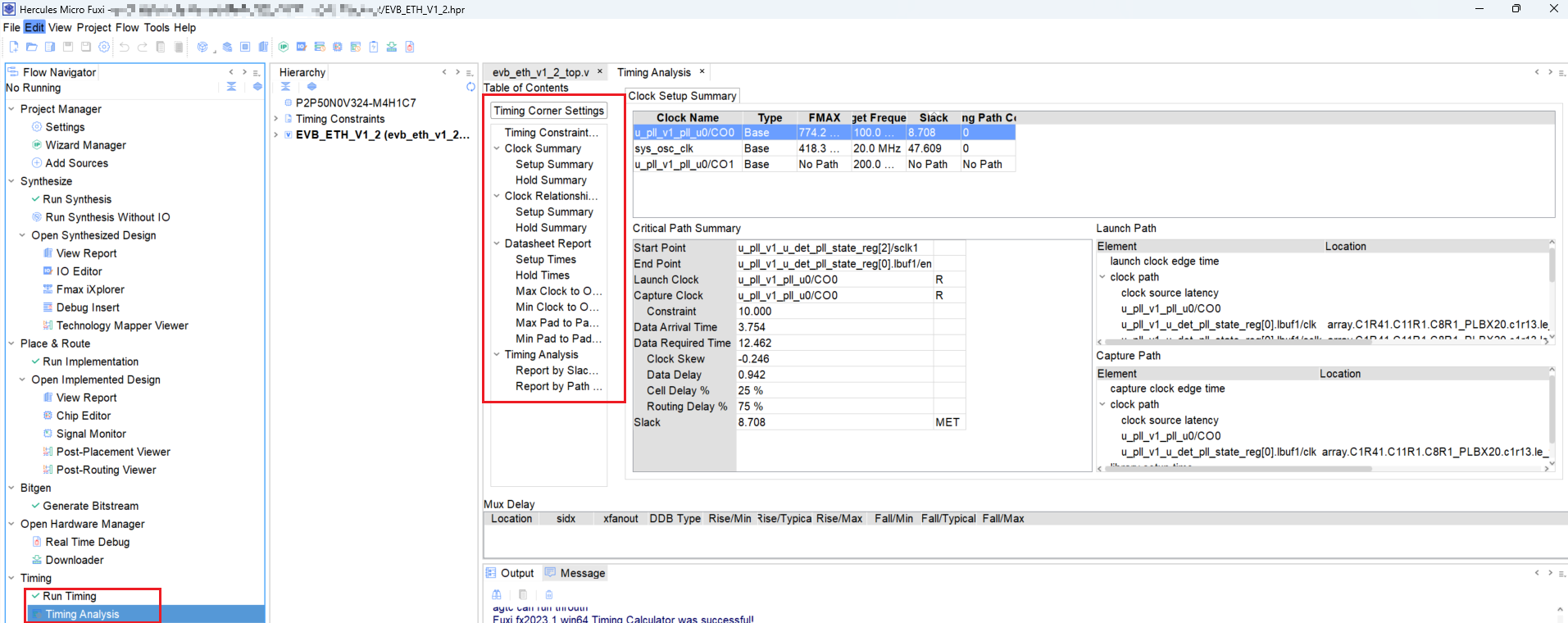

先运行Run Timing,完成后点击Timing Analysis分析时序报告。

小结:

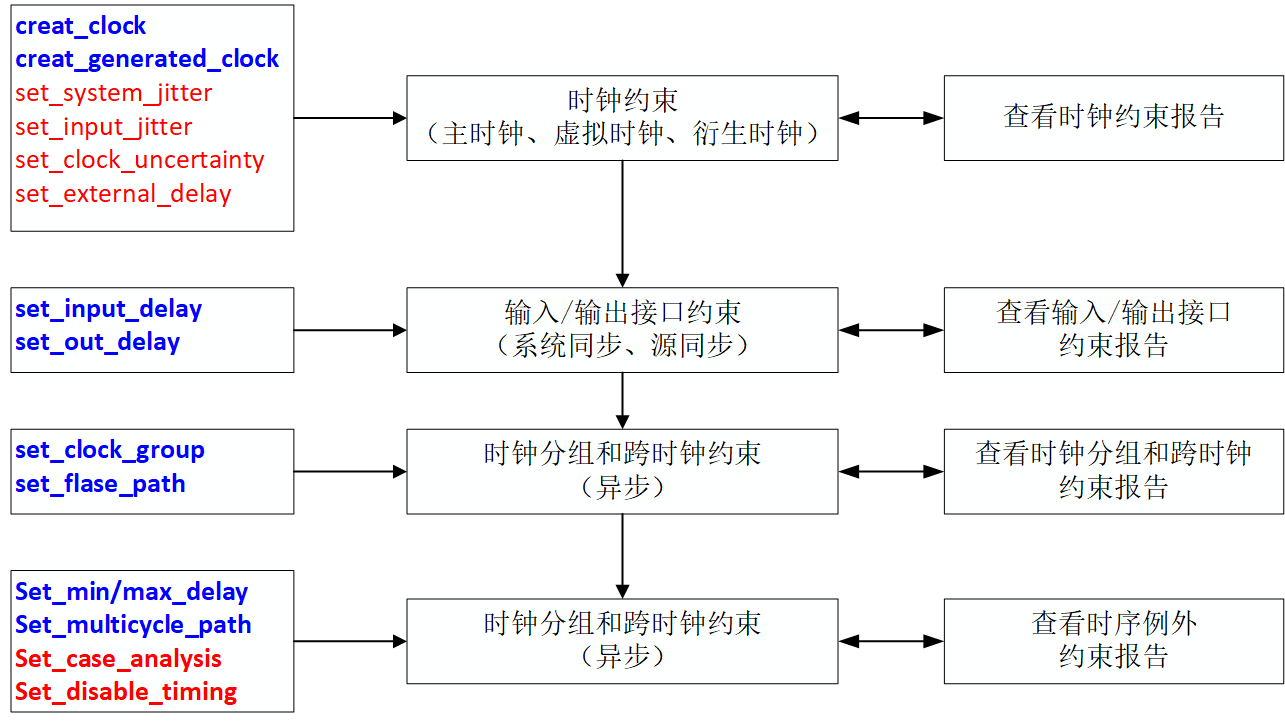

时序约束通常可以分为以下4个主要步骤:

始终约束(Create Clock)->输入/输出接口约束(Input/Output Delay,I/O约束)、时钟分组和跨时钟约束(Clock Group and CDC)、时钟例外约束(Timing Exceptions)。

注意:必选要正确的梳理时钟树。