静态时序分析STA——7.2 STA环境的配置(输入输出路径约束)

文章目录

- 三、约束输入路径

- 四、约束输出路径

- 例子A

- 例子B

- 例子C

参考文献

[1]Static Timing Analysis for Nanometer Designs A Practical Approach

三、约束输入路径

在一些示例中我们可能并不关心某些逻辑,因而这些输入路径可能可以不用约束。例如,设计人员可能并不在乎一些输入控制信号的时序,因此可能并不需要进行本节中将要介绍的时序检查。但是,目前假定我们要约束全部的输入路径。

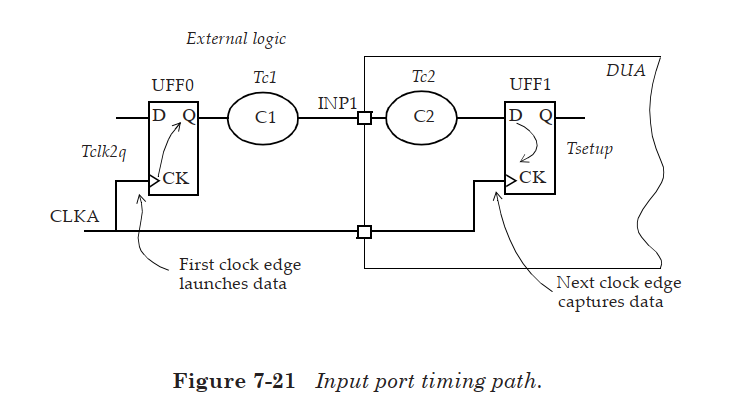

图 7-21 中为待分析设计(DUA)的输入路径。触发器 UFF0 在设计的外部,并向设计内部的触发器 UFF1 提供数据。数据通过输入端口INP1 连接两个触发器。

CLKA 的时钟定义指定了时钟周期,这是两个触发器 UFF0 和 UFF1 之间可用的总时间。外部逻辑所需的时间为 Tclk2q(数据发起触发器UFF0 的 CK 至 Q 延迟)加上 Tc1(通过外部组合逻辑的延迟),因此输入引脚 INP1 上的延迟定义指定了 Tclk2q 加上 Tc1 的外部延迟。并且这个外部延迟是相对于一个时钟指定的,在本示例中为时钟CLKA。

以下是输入延迟的约束

set Tclk2q 0.9

set Tc1 0.6

set_input_delay -clock CLKA -max [expr Tclk2q + Tc1] [get_ports INP1]

该约束指定输入端口 INP1 的外部延迟为 1.5ns,且这是相对于时钟CLKA 而言的。假设 CLKA 的时钟周期为 2ns,则 INP1 引脚的逻辑只有 500ps(= 2ns-1.5ns)可以在设计内部中传播。此输入延迟定义意味着输入约束为: Tc2 加上触发器 UFF1 的 Tsetup 必须小于 500ps,才可以确保可靠地捕获到触发器 UFF0 发起的数据。请注意,上述外部延迟值被指定为了最大值(max)。

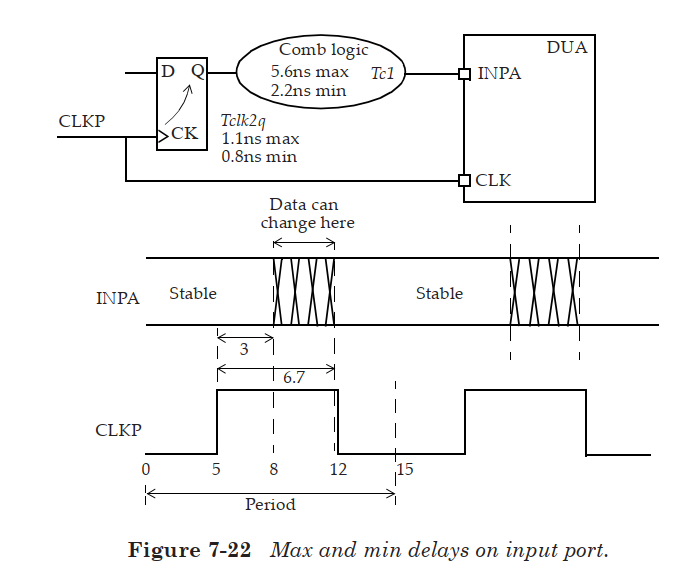

如果同时考虑最大和最小延迟情况,如图 7-22 所示。以下是此示例的约束:

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

INPA 的最大和最小延迟是从 CLKP 到 INPA 的延迟中得出的,最大和最小延迟分别是最长和最短路径延迟,这些通常也可以对应于最坏情况(worst-case)下的慢速(最大时序工艺角)和最佳情况(bestcase)下的快速(最小时序工艺角)。因此,最大延迟对应于最大时序工艺角下的最长路径延迟,最小延迟对应于最小时序工艺角下的最短路径延迟。在我们的示例中, 1.1ns 和 0.8ns 是 Tck2q 的最大和最小延迟值。组合逻辑路径延迟 Tc1 的最大延迟为 5.6ns,最小延迟为2.2ns。 INPA 上的波形显示了数据到达设计输入端的时间窗口,以及预计达到稳定状态的时间。从 CLKP 到 INPA 的最大延迟为 6.7ns(=1.1ns + 5.6ns),最小延迟为 3ns(= 0.8ns + 2.2ns),这些延迟是相对于时钟有效沿指定的。在给定外部输入延迟的情况下,设计内部的可用建立时间是慢角(slow corner)下的 8.3ns(= 15ns-6.7ns)和快角(fast corner)下的 12ns(= 15ns-3.0ns)中的最小值。因此, 8.3ns 是用来可靠地捕获 DUA 内部数据的可用时间。

注意,未指定 max 或 min 选项,因此 500ps 这个值将同时用于最大延迟和最小延迟。此外部输入延迟是相对于时钟 clk_core 的上升沿指定的(如果输入延迟是相对于时钟的下降沿指定的,则必须使用-clock_fall 选项)。

四、约束输出路径

以下通过三个例子来介绍输出路径的约束。

例子A

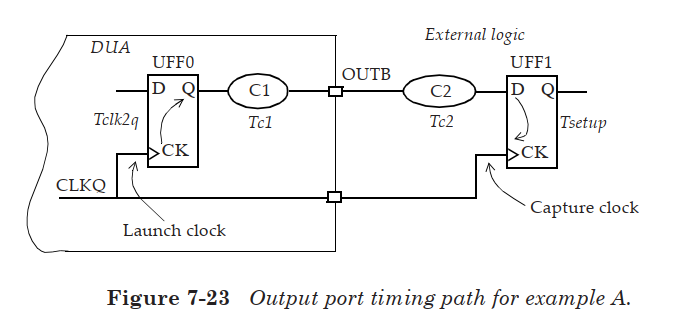

图 7-23 为一条通过待分析设计输出端口的路径示例,其中 Tc1 和 Tc2 是通过组合逻辑的延迟。

时钟 CLKQ 的周期定义了触发器 UFF0 和 UFF1 之间的总可用时间。外部逻辑的总延迟为 Tc2 加上 Tsetup,此总延迟 Tc2 + Tsetup 必须作为输出延迟约束的一部分来指定。注意,输出延迟是相对于捕获时钟指定的,数据必须及时到达外部触发器 UFF1 才能满足其建立时间要求。

set Tc2 3.9

set Tsetup 1.1

set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]

这指定了相对于时钟边沿的最大外部延迟为 Tc2 加上 Tsetup,即 5ns 的延迟。最小延迟可以类似地指定。最大输出延迟为Tc2_max+Tsetup。

例子B

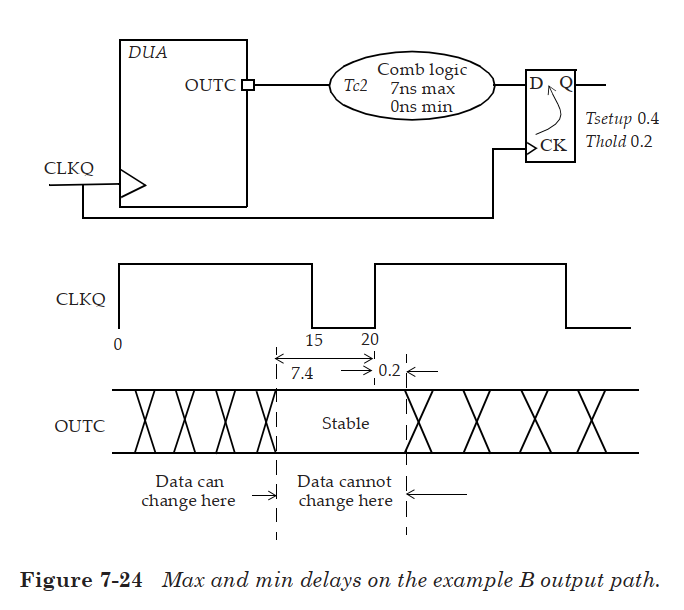

图 7-24 给出了同时具有最小和最大延迟的示例。最大路径延迟为7.4ns(=Tc2 最大值加上 Tsetup = 7 + 0.4),最小路径延迟为-0.2ns(=Tc2 最小值减去 Thold = 0-0.2)。因此,输出约束为:

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

图 7-24 中的波形显示了 OUTC 必须保持稳定状态的时间,以确保外部触发器能够可靠地捕获它。这说明在所需的稳定区域开始之前,数据就必须在输出端口准备就绪,并且必须保持稳定,直到稳定区域结束为止。这同样反映了 DUA 内部对输出端口 OUTC 逻辑的时序要求。最大输出延迟为Tc2_max+Tsetup,最小输出延迟为tc2_min-thold。

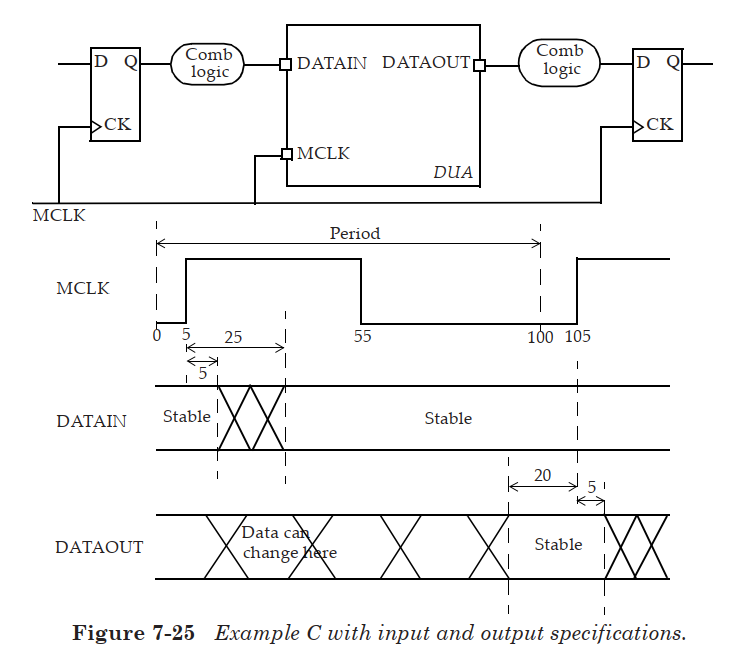

例子C

该模块具有两个输入端口DATAIN 和 MCLK,以及一个输出端口 DATAOUT。图 7-25 显示了预期的波形。

create_clock -period 100 -waveform {5 55} [get_ports MCLK]

set_input_delay 25 -max -clock MCLK [get_ports DATAIN]

set_input_delay 5 -min -clock MCLK [get_ports DATAIN]

set_output_delay 20 -max -clock MCLK [get_ports DATAOUT]

set_output_delay -5 -min -clock MCLK [get_ports DATAOUT]