【读书笔记·VLSI电路设计方法解密】问题61:扫描插入的目的是什么

如问题60所述,要构建可测试电路,必须确保电路中每个节点都具有可控性和可观测性。但对于包含时序元件(如触发器、锁存器等存储元件)的电路,若不采取特殊设计则难以实现这两项特性。这是因为时序元件关联节点的逻辑状态不仅取决于当前输入,还受其先前存储状态影响——它们具有记忆功能。为将节点状态确定性地设置为已知值,芯片内部通常采用称为扫描链的技术。

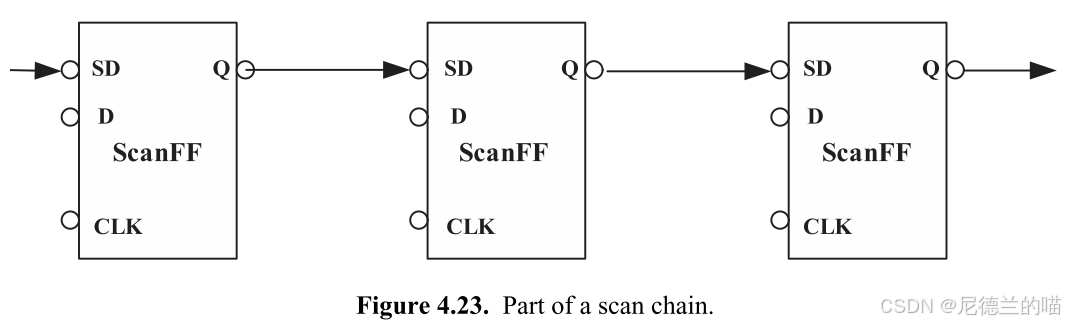

图4.23展示了扫描链的部分结构。如图所示,标准D触发器(具有D输入端、CLK时钟端和Q输出端)被替换为可扫描触发器,后者额外增加了SD输入引脚。其设计原理是通过SD引脚将触发器置为已知状态。这些可扫描触发器以链式结构连接,使得受控数值能通过该链从芯片主输入端传输至每个触发器。同时,内部节点的逻辑值也通过该链传输至芯片主输出端。

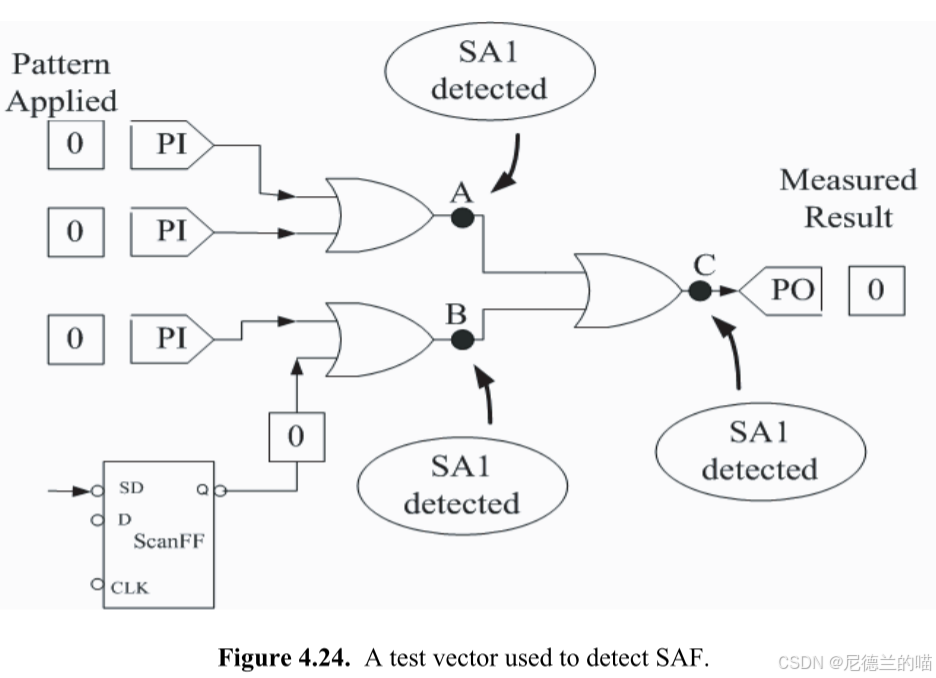

图4.24演示了使用测试向量检测电路内部固定型故障的实例。如图所示&#