VESA DSC 基于FPGA DSC_Encoder IP仿真

VESA DSC 基于FPGA DSC_Encoder IP仿真

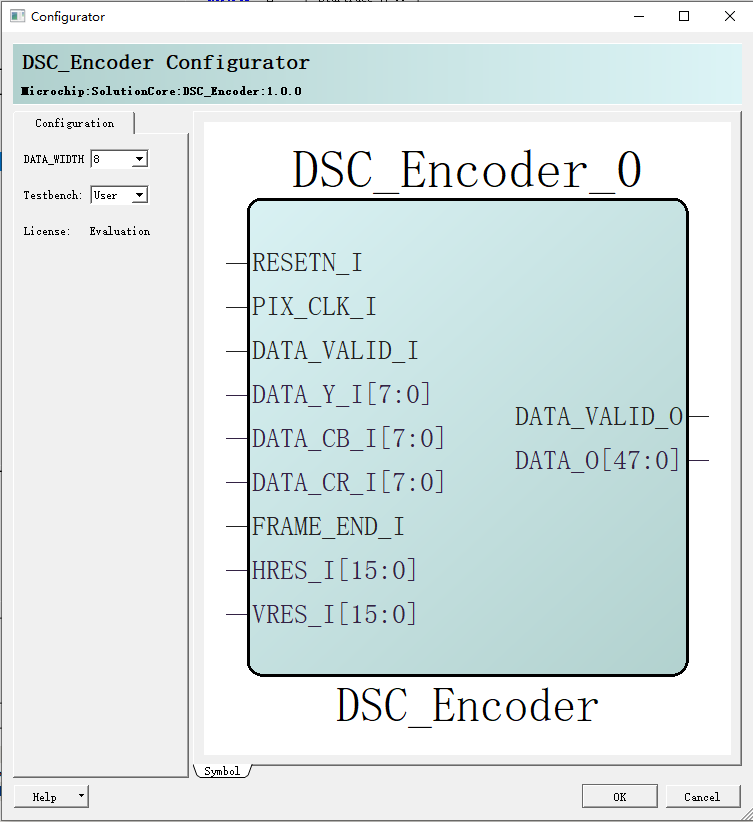

1:IP设置

2:仿真文件导入

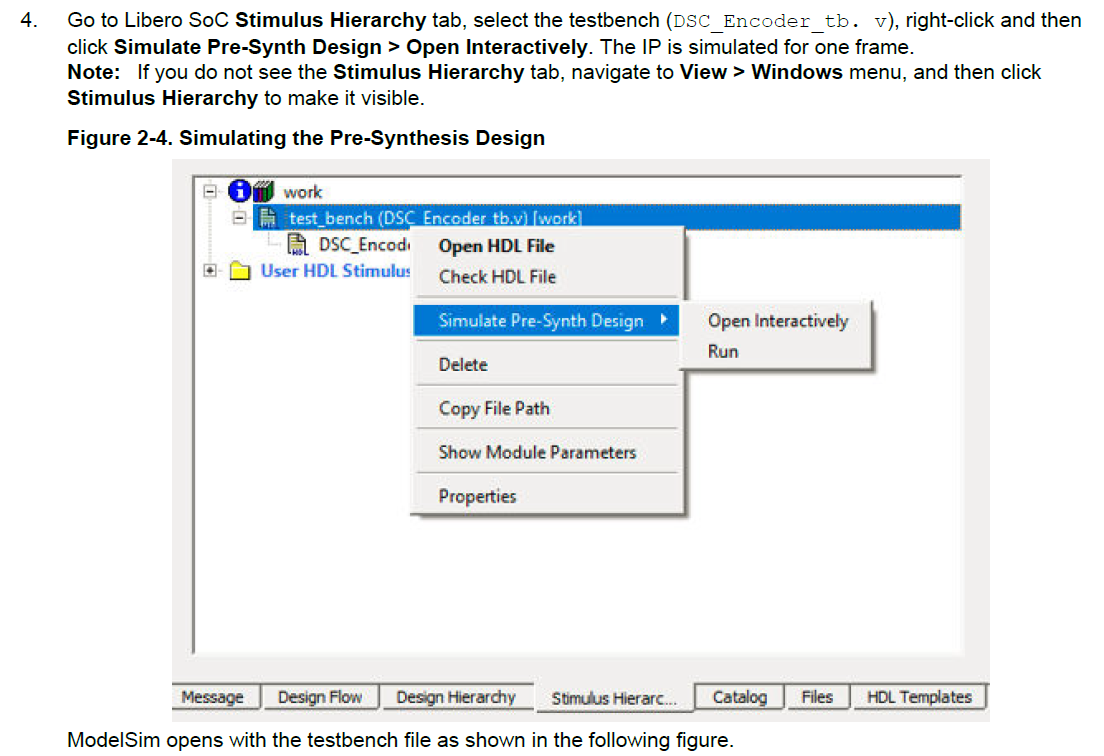

3:仿真

//

// Created by Microsemi SmartDesign Thu Oct 10 12:36:11 2019

// Testbench Template

// This is a basic testbench that instantiates your design with basic

// clock and reset pins connected. If your design has special

// clock/reset or testbench driver requirements then you should

// copy this file and modify it.

//

///

// Company: <Name>

//

// File: test_bench.v

// File history:

// <Revision number>: <Date>: <Comments>

// <Revision number>: <Date>: <Comments>

// <Revision number>: <Date>: <Comments>

//

// Description:

//

// <Description here>

//

// Targeted device: <Family::PolarFire> <Die::MPF300T> <Package::FCG1152>

// Author: <Name>

//

///

`timescale 1ns/100ps

module test_bench;

parameter SYSCLK_PERIOD = 10;// 100MHZ

parameter H_RES = 432;

parameter V_RES = 240;

parameter g_DATAWIDTH = 8;

reg SYSCLK;

reg NSYSRESET;

reg [15:0] h_resolution=H_RES,v_resolution=V_RES,h_blanking=280,v_blanking=20;

reg [15:0] h_counter,v_counter,h_total,v_total;

reg h_active,v_active,data_valid,data_valid_dly,eof,eof_dly;

reg[g_DATAWIDTH : 0] Y_array[0:(H_RES*V_RES)-1];

reg[g_DATAWIDTH : 0] Cb_array[0:(H_RES*V_RES)-1];

reg[g_DATAWIDTH : 0] Cr_array[0:(H_RES*V_RES)-1];

reg[47 : 0] bitstream_quant_array[0:(H_RES*V_RES)-1];

reg[11 : 0] bitstream_array[0:(H_RES*V_RES)-1];

wire [g_DATAWIDTH - 1 : 0] Y_data,Cb_data,Cr_data;

wire [47 : 0] bitstream_quant;

wire bitstream_quant_valid;

reg [7 : 0] dsc_out_ref [0 : 262143];

reg [17 : 0] ref_addr;

reg [15 : 0] err;

reg pulse=0;

integer i;

//

// Reset Pulse

//

initial

begin

SYSCLK = 0;

NSYSRESET = 0;

#(SYSCLK_PERIOD * 10 )

NSYSRESET = 1'b1;

end

//

// Clock Driver

//

always @(SYSCLK)

#(SYSCLK_PERIOD / 2.0) SYSCLK <= !SYSCLK;

/

// initialize the hexadecimal reads from the file

initial $readmemh("img_in_luma.txt", Y_array);

initial $readmemh("img_in_cb.txt", Cb_array);

initial $readmemh("img_in_cr.txt", Cr_array);

initial $readmemh("dsc_out_ref.txt", dsc_out_ref);

assign Y_data = Y_array[i][7:0];

assign Cb_data = Cb_array[i][7:0];

assign Cr_data = Cr_array[i][7:0];

initial

begin

h_total = h_resolution + h_blanking;

v_total = v_resolution + v_blanking;

end

always @(posedge SYSCLK or negedge NSYSRESET) begin

if(~NSYSRESET) begin

pulse <= 0;

end

if(data_valid==1 && data_valid_dly==0) begin

pulse = 1;

end

else begin

pulse = pulse;

end

end

always@(h_counter,h_resolution) begin

if(h_counter >= (h_blanking+1)) begin

h_active = 1;

end

else begin

h_active = 0;

end

end

always@(v_counter,v_resolution) begin

if(v_counter >= (v_blanking+1)) begin

v_active = 1;

end

else begin

v_active = 0;

end

end

always@(h_active,v_active) begin

data_valid = h_active && v_active;

end

always@(v_counter) begin

if((v_counter == 15)&&(pulse==1)) begin

eof = 1;

end

else begin

eof = 0;

end

end

// Horizontal counter

always @(posedge SYSCLK or negedge NSYSRESET) begin

if(~NSYSRESET) begin

h_counter <= 0;

i <= 0;

data_valid_dly <= 0;

eof_dly <= 0;

end

else begin

data_valid_dly <= data_valid;

eof_dly <= eof;

if(h_counter < h_total) begin

h_counter <= h_counter + 1;

end

else begin

h_counter <= 0;

end

if(eof == 1) begin

i <= 0;

end

else begin

if (data_valid == 1) begin

i = i + 1;

end

end

end

end

// Vertical counter

always @(posedge SYSCLK or negedge NSYSRESET) begin

if(~NSYSRESET) begin

v_counter <= 0;

end

else begin

if(h_counter == h_total) begin

if(v_counter < v_total) begin

v_counter <= v_counter + 1;

end

else begin

v_counter <= 0;

end

end

end

end

//

// Instantiate Unit Under Test: data_gather

//

DSC_Encoder #(.G_DATA_WIDTH(g_DATAWIDTH)) DSC_Encoder(

// Inputs

.RESETN_I(NSYSRESET),

.PIX_CLK_I(SYSCLK),

.DATA_Y_I(Y_data),

.DATA_CB_I(Cb_data),

.DATA_CR_I(Cr_data),

.HRES_I(H_RES[15:0]),

.VRES_I(V_RES[15:0]),

.DATA_VALID_I(data_valid),

.FRAME_END_I(eof),

// Outputs

.DATA_O(bitstream_quant),

.DATA_VALID_O(bitstream_quant_valid)

);

always @ (posedge SYSCLK, negedge NSYSRESET)begin

if(~NSYSRESET) begin

err <= 0;

ref_addr<= 0;

end

else if(eof==0 && eof_dly==1) begin

err <= 0;

ref_addr<= 0;

end

else if (bitstream_quant_valid)begin

ref_addr <= ref_addr + 6;

if(bitstream_quant != {dsc_out_ref[ref_addr],dsc_out_ref[ref_addr+1],dsc_out_ref[ref_addr+2],dsc_out_ref[ref_addr+3],

dsc_out_ref[ref_addr+4],dsc_out_ref[ref_addr+5]}) begin

err <= err + 1;

end

end

end

always @ (posedge SYSCLK, negedge NSYSRESET)begin

if(eof==1 && eof_dly==0) begin

$display(" ***********************************");

$display(" ***********************************");

$display(" H_RES:%d V_RES:%d",H_RES,V_RES);

if(err == 0) begin

$display(" DSC Compression Test Passed");

$display(" ***********************************");

$display(" ***********************************");

end

else begin

$display(" DSC Compression Test Failed");

$display(" ***********************************");

$display(" ***********************************");

end

$stop;

end

end

endmodule

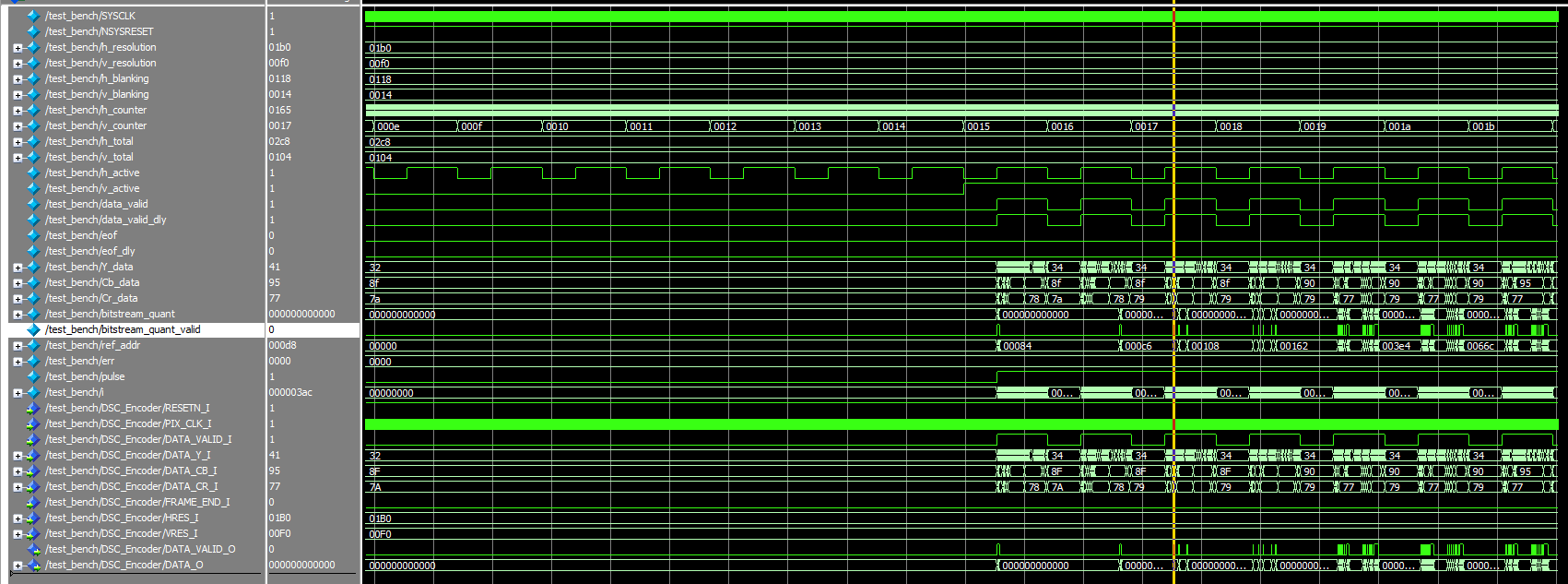

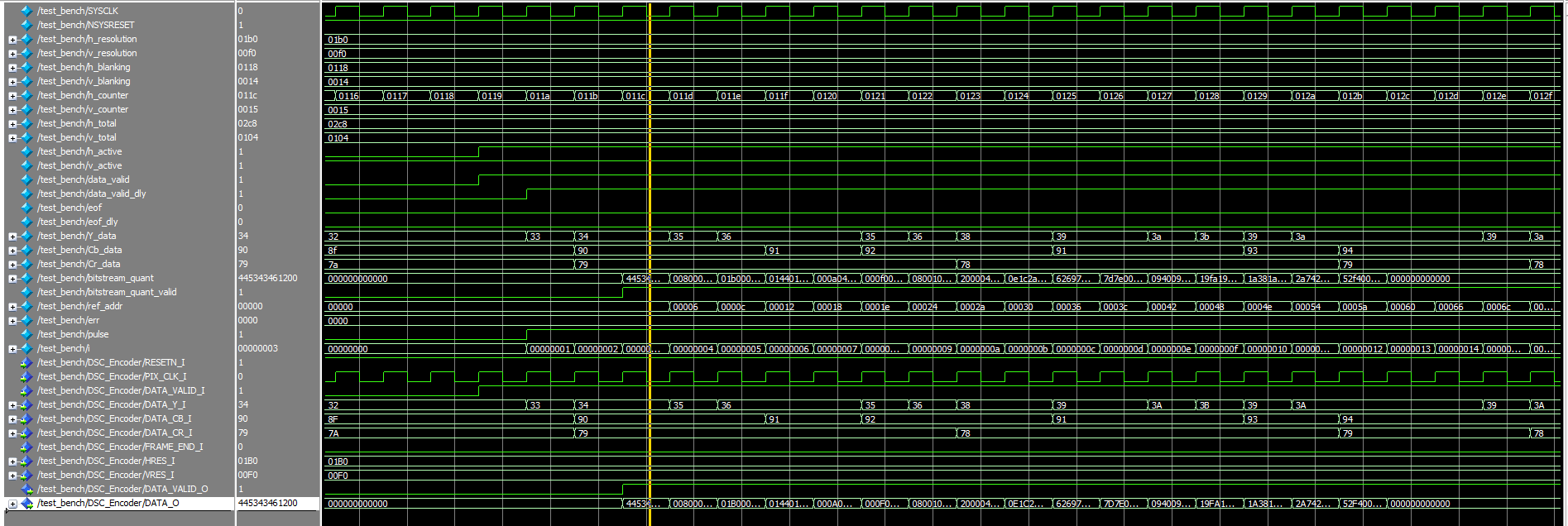

4:仿真运行

5:欢迎讨论交流

微:moning_hello