VCS elab选项 -simprofile功能

#废话不多说,直接上干货

1.简介

VCS提供的simprofile功能是用于分析仿真过程中的CPU time和machine memory消耗情况,可以协助定位一些垃圾代码写法导致的仿真资源消耗过大问题;本篇内容包含,应用此功能的必要工具准备、makefile代码写法、仿真结束时simprofile_REPORT报告的结果分析策略,以及实战应用举例。

也许你在观看此博客之前,会有如下问题:

(1)我的仿真时间 & 内存消耗超出了预期,我该怎么定位问题?

(2)simprofile能做到哪种程度?是否可以具体定位到某行代码?

(3)仿真过程中,耗费资源的具体行为都有哪些?

(4)我是一名DE/DV,这个功能对我有用吗?

(5)我现在就要试一下这个功能,怎么快速上手操作?

希望能够在看完博客后,解决你的疑惑,帮助到深受垃圾代码折磨的ICer们(如果你觉得有用,请点赞此博客,谢谢)。

2.准备工作

2.1 PYTHON准备

VCS官方文档中表明,需要python的最低版本为python 2.3,用于产生HTML reports;(笔者应用的是python 3.7.3)

2.2 VCS准备

VCS版本最好2023及以上;(笔者应用的是V-2023.12-SP2)

2.3 HTML查看工具准备

Firefox或其他工具;(笔者用的是Mozilla Firefox 115.12.0esr)

Firefox需要做如下配置的更改:

(1)地址栏键入:

(2)接受风险提示:

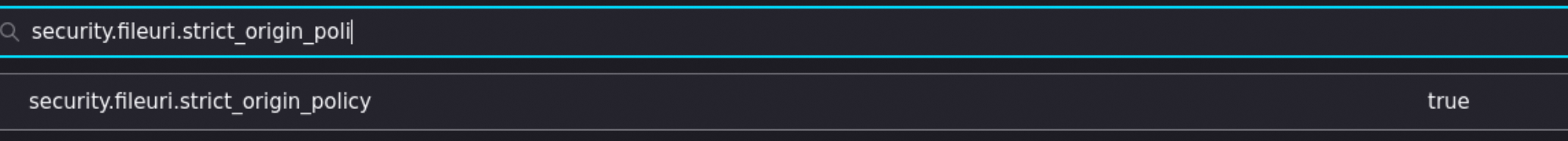

(3)搜索 security.fileuri.strict_origin_policy,将其值改为faulse,并刷新firefox;

3.makefile关键代码

3.1 编译 & elab & 仿真流程

如果你采用2步法编译&仿真,则需要在makefile中加入如下编译 & 仿真指令:

vcs -simprofile -f file_list.fvcs /xxx/xxx/simv -simprofile time -l vcs_run.log +ntb_random_seed=1234如果你采用3步法编译&仿真,则需要在makefile中加入如下编译 & elab & 仿真指令:

vlogan -lca -kdb xxxx(anycode you want) -f file_list.fvcs -simprofile xxxxvcs /xxxx/xxxx/simv -simprofile time需要注意的是,如果已经存在了simv/simv.daidir/csrc文件,则需要提前删除这些文件,增量式开发暂不支持;

其中,仿真阶段的simprofile命令的使用很重要,该命令的标准应用格式如下:

simv -simprofile [argument] -simprofile_dir_path [pathname][argument]可配置选项为:time、mem、fastmem、noprof、noreport;

time:表示收集CPU时间消耗分布情况;

mem:表示收集机器内存使用分析情况;

fastmem:当你的design很大时,为了尽快收集mem profile时,采用该选项;

noprof:当你在编译阶段加了-simprofile命令时,但不想在仿真阶段收集profile并生成数据库,采用该选项(不建议编译时加入-simprofile但仿真时不加);

noreport:每次仿真结束时,若不添加该选项,则会自动产生report报告;

3.2 仿真后处理流程

当你的仿真选项如下时:

simv -simprofile time -simprofile_dir_path ./profile_dir则每次仿真后,VCS会将产生的profile相关数据库存放于./profile_dir内,并生成如下目录及文件:

simprofile_dir/profileReport/profileReport.html/profileReport.txt/profileReport.json

其中profileReport.html可直接用firefox打开;

若你的仿真选项如下时:

simv -simprofile noreport -simprofile_dir_path ./profile_dir4.报告解读

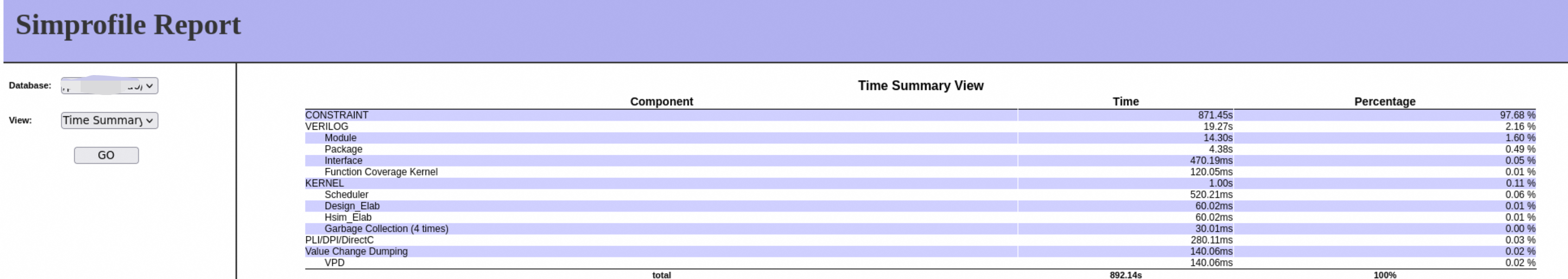

4.1 TimeSummary信息总览

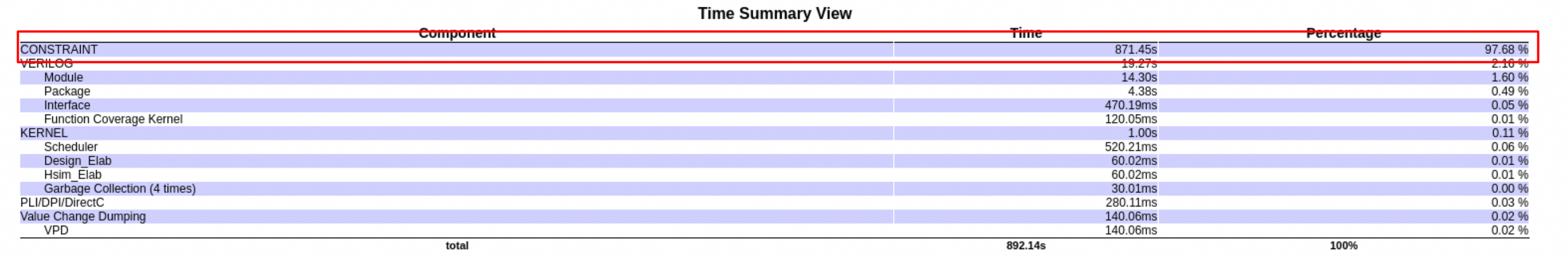

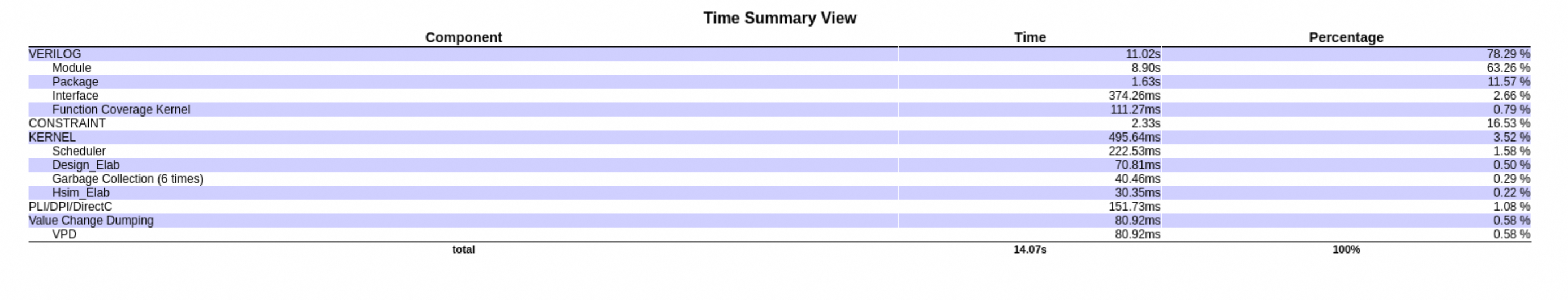

TimeSummary能够提供的是最高层次的仿真耗时信息,如下所示,该信息包括:Constraint时间、Kernel时间、Verilog时间、PLI/DPI/C时间等关键信息:

(1)Constraint时间:顾名思义,constraint时间列出了仿真过程中所有约束求解器工作时所占用的CPU Time;

(2)Verilog时间:verilog代码耗时,包含module耗时、interface耗时、功能覆盖率耗时等;

(3)Kernal时间:核心仿真引擎总耗时,包含事件调度(scheduler)、设计仿真维护(Design Elab)、仿真时间推进(Hsim_Elab)、垃圾回收(Garbage collection);

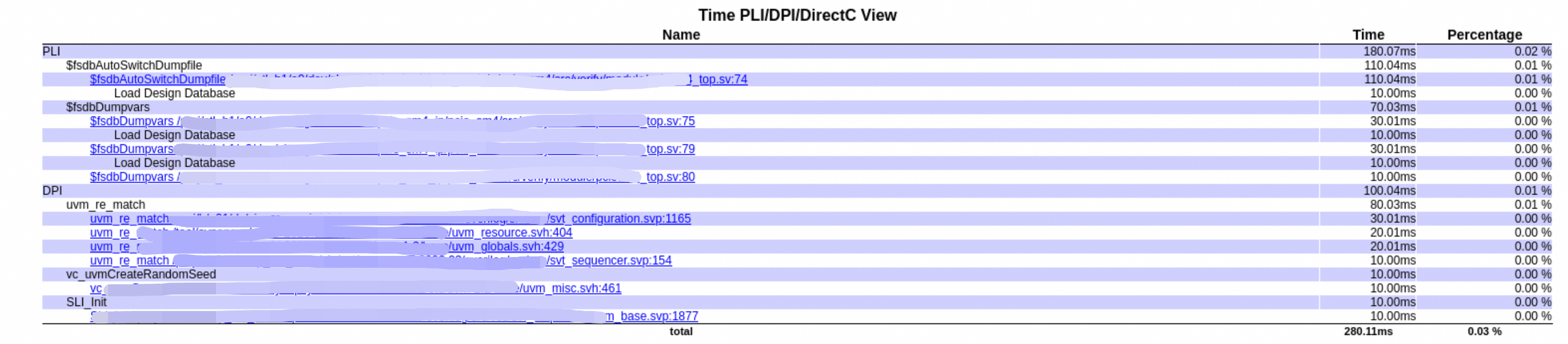

(4)PLI/DPI/C时间:一些PLI/DPI接口调用时间及C代码执行时间,(其中dump_wave时间也统计于此);

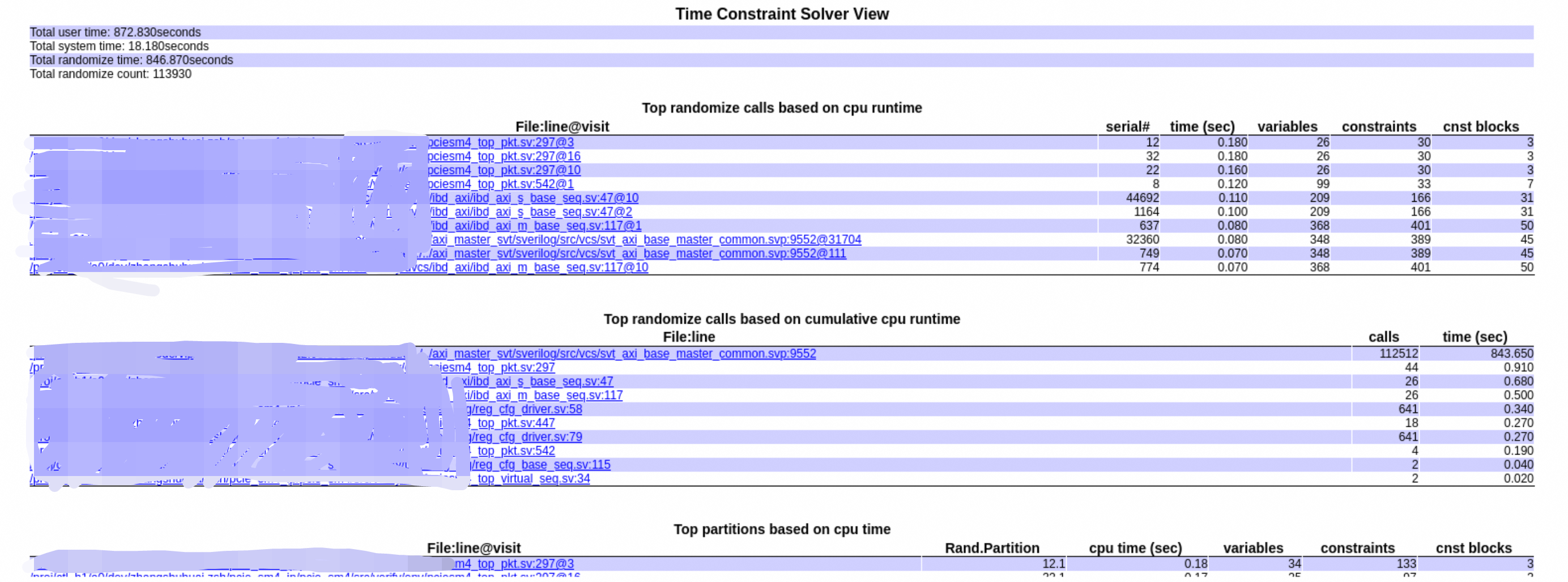

4.2 Time Constraint Solver View

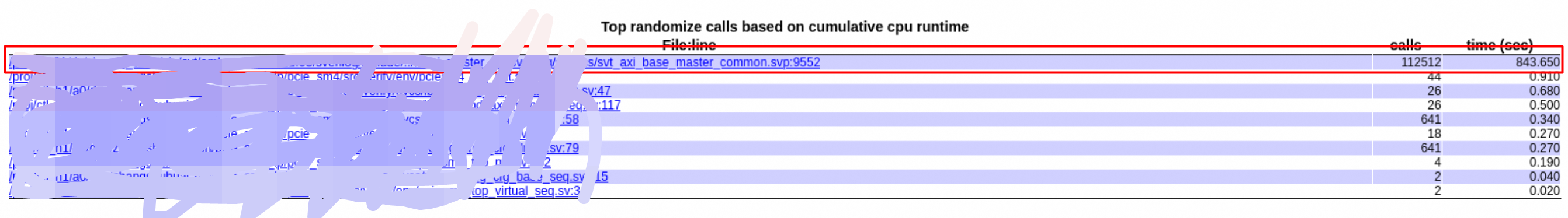

最耗费CPU Time的Solver求解器细节,可具体到某行代码,某个pkt.randomize();

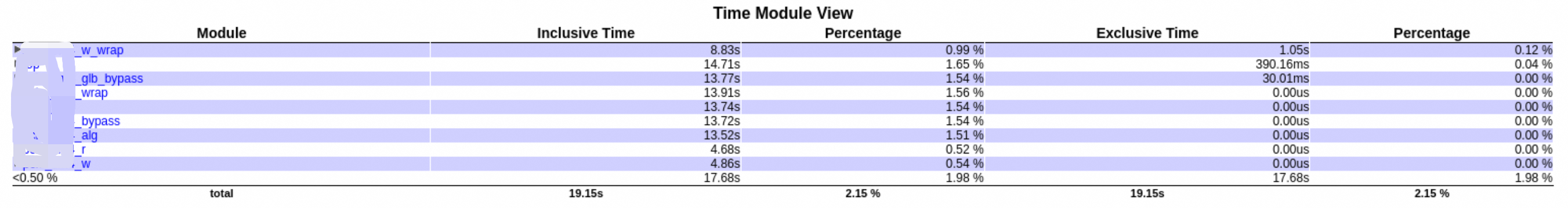

4.3 Time Module View

最耗时的Module,其中耗时<0.5%的模块不做统计;

4.4 Time PLI/DPI/C View

最耗时的PLI/DPI/C调用,其中耗时<0.5%的模块不做统计;

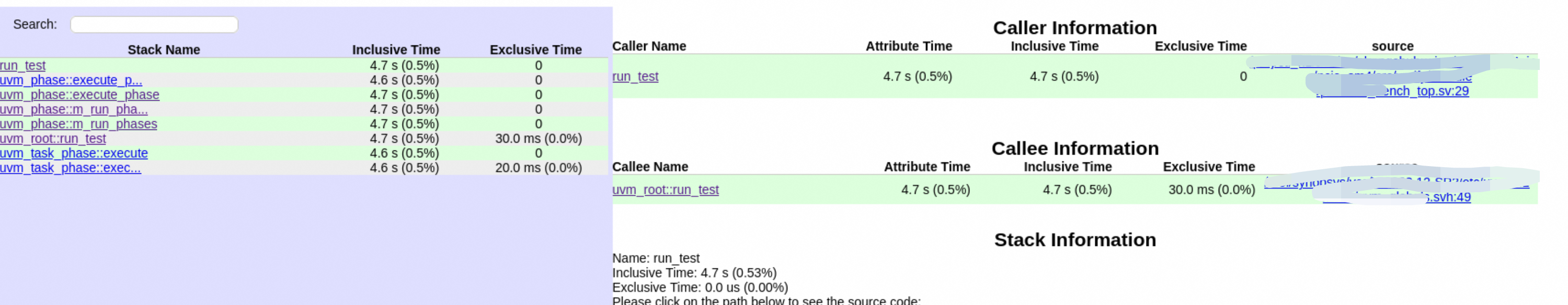

4.5 UVM-Time Caller

UVM环境各个phase执行时间统计,可详细展开查看;

4.6 Time Coverage View

顾名思义,功能覆盖率时间消耗统计,不展开了;

5.实例;

5.1 解决AXI VIP写操作仿真耗时过大问题

问题描述:使用VIP仿真时发现,对于AXI写操作,每当环境在产生W CH激励时,CPU time都会超长,从而导致仿真时间大大增加,但却难以定位VIP内部问题;

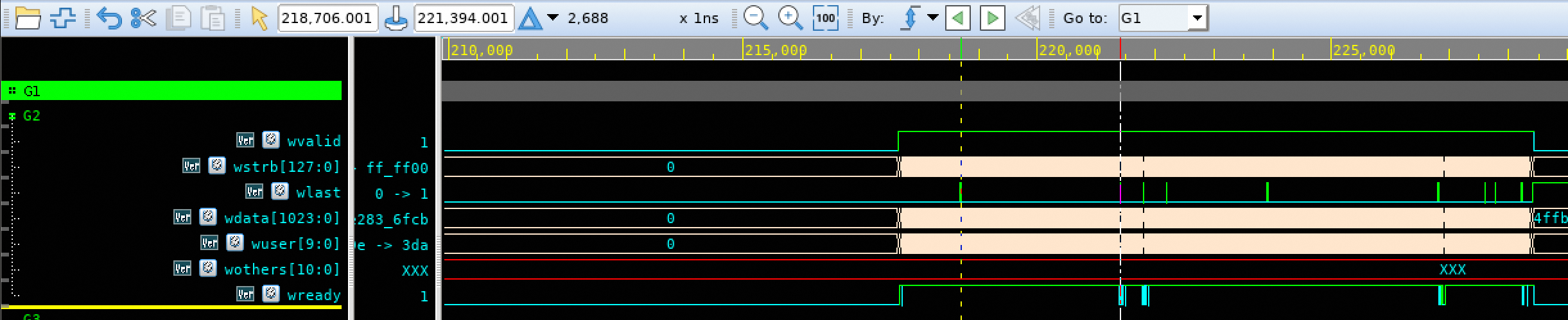

具体波形如下:W CH发送数据这一段,仿真时间只有短短的2688ns,但CPU Time长达5~8min;

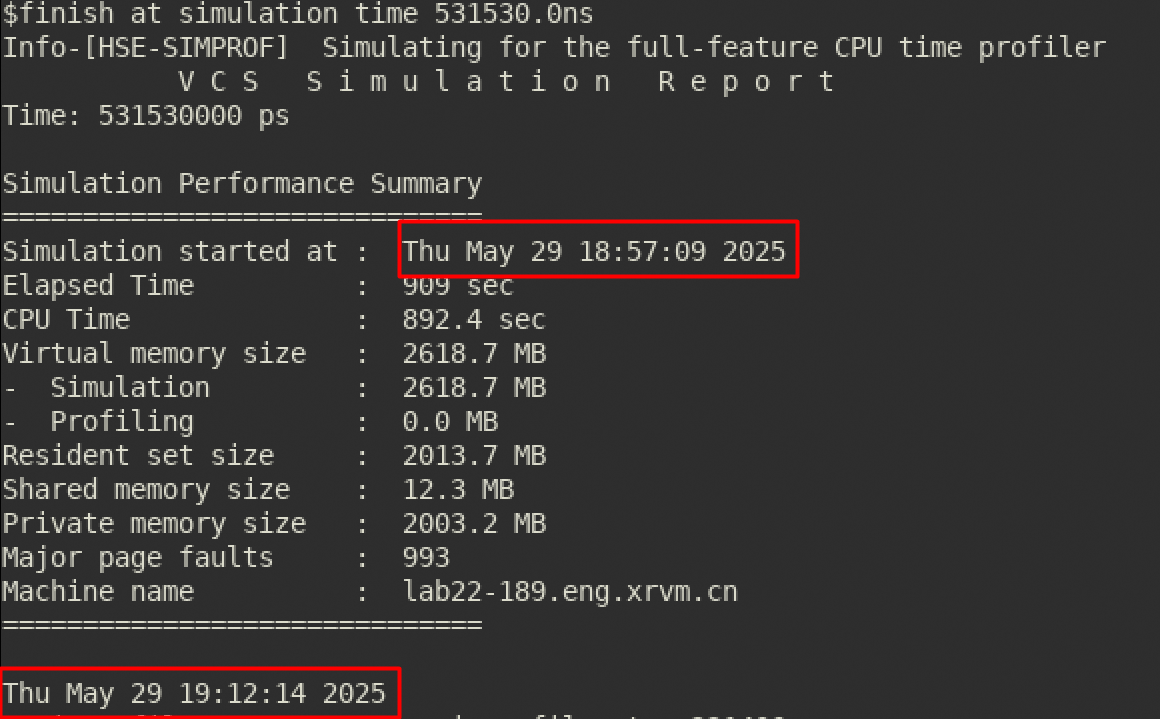

本用例中发送了这种长度的wr包3~4次,结果就是导致整个用例跑下来的时间长达15min;

解决方案:打开simprofile功能,跑仿真,profile_dir内产生了profileReport.html报告如下:

报告提示我,Constraint消耗仿真资源太大了,好那就去看Time constraint章节:

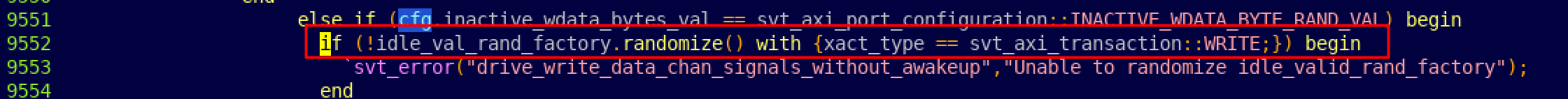

提示AXI VIP svt_axi_base_master_common.svp的第9552行代码疯狂调用了112512次(笔者发现是每个axi clk调用一次),总共耗时CPU Time 843s,好家伙,一个15分钟的case,被这行垃圾代码坑了14分钟(这难道就是Synopsys VIP的含金量吗):

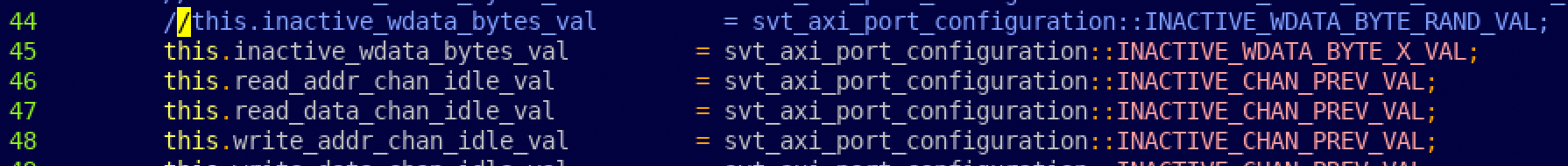

已经定位到原因了,VIP在IDLE时候W CH可以配置随机值或者X态/Z态等,如果选择随机值,在idle时候驱动写数据进行随机,会导致VIP每个clk疯狂调用randomize(),改成idle时候驱动X态即可。

重新编译 & 仿真:

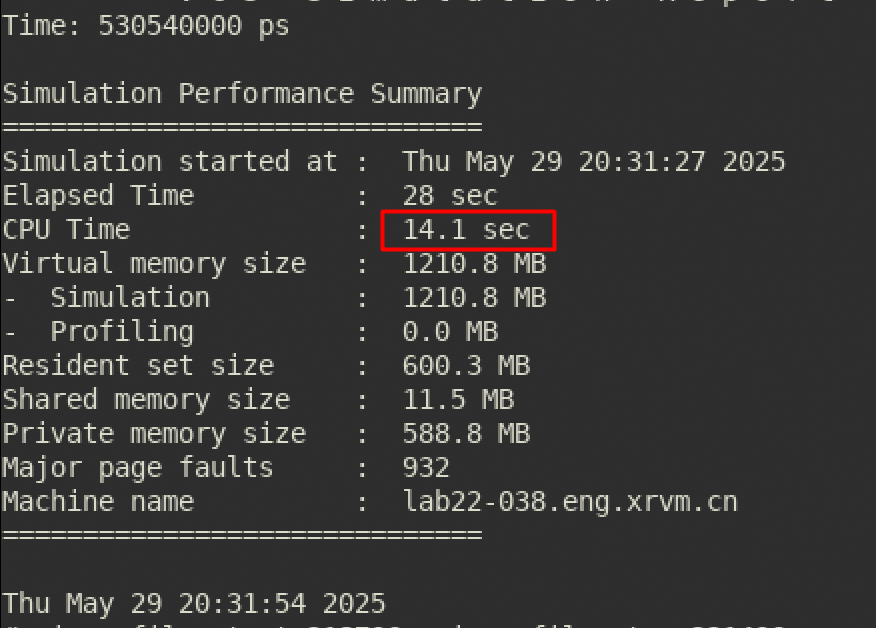

是的,你没有看错,原来15min的用例,只需要27s就可以跑完了,速度提升30倍。就这样简单粗暴!

再看下summary view,发现VERILOG运行占据78%的时间,环境其他只占用了22%,debug成功!