Allegro X PCB设计小诀窍--07.如何在Allegro X中进行3D布局DRC

背景介绍:我们在进行PCB设计时,为了避免设计缺陷,保证设计的可制造性,通常会使用DRC功能,对印制板布局进行检查,但是这些检查通常只针对印制板上的二维视图。为了帮助设计人员更好的对设计进行检查,Allegro X PCB设计工具增加了3D布局DRC功能,支持在3DX Canvas中验证3D模型、PCB和刚柔结合板之间的物理冲突,并且支持交互式缩放、平移和旋转设计,极大提升了设计可靠性。

下面我们就开始分享具体的操作步骤:

一、3D间距约束集配置

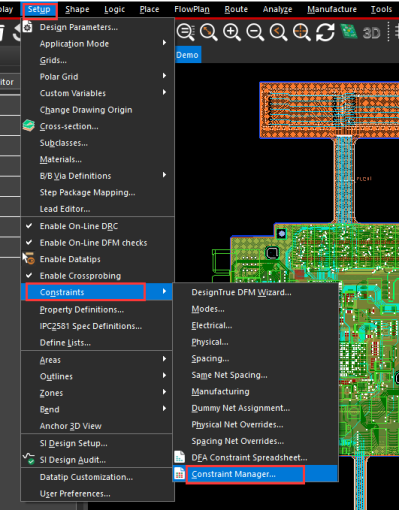

步骤一:使用Allegro X PCB设计工具打开PCB文件,在菜单栏中依次选择【Setup】→【Constraints】→【Constraint Manager...】,如图1所示。

图1 打开约束管理器

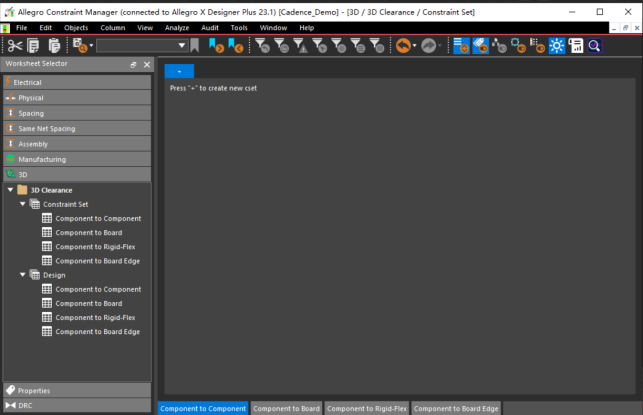

步骤二:在约束管理器中选择3D,即可展开3D布局DRC配置界面,如图2所示。可以看到,在3D Clearance的Constraint Set中共包含四类规则,分别是Component to Component、Component to Board、Component to Rigid-Flex、Component to Board Edge。

图2 3D布局DRC配置界面

3D Clearance下的四类约束集说明,如下表1所示。

表1 3D Clearance约束集说明

| 序号 | 功能名称 | 说明 |

| 1 | Component to Component | 可以设置器件封装或封装类之间的水平、垂直间距约束,检查的封装或者封装类几何形状可选3D模型、Place Bound以及DFA Bound。 |

| 2 | Component to Board | 可以设置封装或封装类与钻孔/插槽和印制板边缘的间距约束,检查的封装或者封装类几何形状可选3D模型、Place Bound以及DFA Bound。 |

| 3 | Component to Rigid-Flex | 可以设置封装或封装类与刚柔结合板可变形的刚性区域或者柔性区域之间的水平、垂直间距约束,检查的封装或者封装类几何形状可选3D模型、Place Bound以及DFA Bound。 |

| 4 | Component to Board Edge | 可以设置封装或封装类与印制板的物理边缘之间的间距约束,印制板的物理边缘包括印制板边缘、Cutout区域边缘以及NC Route paths等,检查的封装或者封装类几何形状可选3D模型、Place Bound以及DFA Bound。 |

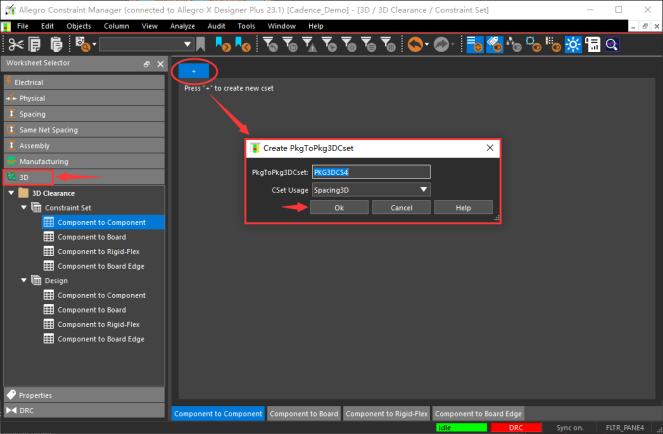

步骤三:我们以Component to Component规则为例进行说明。在Constraint Set中选择Component to Component,然后在右侧界面点击“+”,在弹出的窗口中输入约束集名称,点击OK,如图3所示。

图3 添加Component to Component约束集

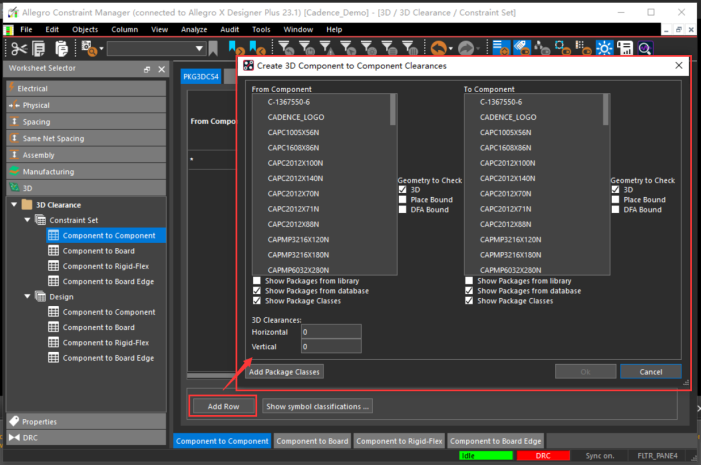

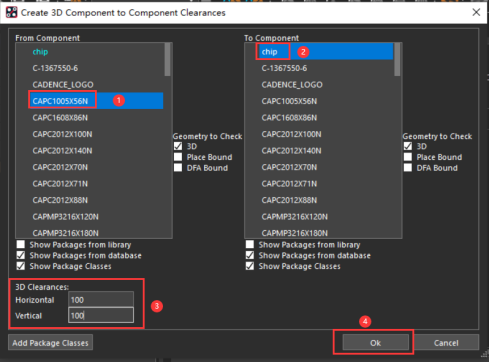

步骤四:在如图4所示约束集界面,点击”Add Row”菜单,即可弹出要进行3D Clearance检查的Component选择界面。

图4 选择Component界面

Create 3D Component to Component Clearances界面说明,如下表2所示。

表2 Create 3D Component to Component Clearances界面说明

| 序号 | 功能名称 | 说明 |

| 1 | Geometry to Check | 几何体检查对象。根据需求可以勾选3D、Place Bound或者DFA Bound作为约束条件的检查对象。 |

| 2 | Show Packages from library | 显示库(PSMPATH目录)中的封装 |

| 3 | Show Packages from database | 显示设计中的封装 |

| 4 | Show Package Classes | 显示添加的封装类 |

| 5 | 3D Clearances | 可设置水平和垂直方向的间距约束值 |

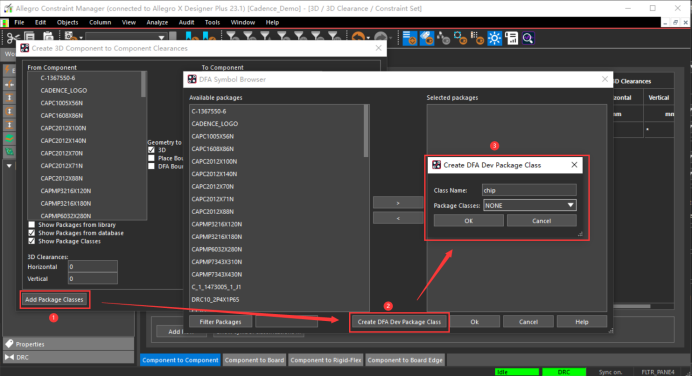

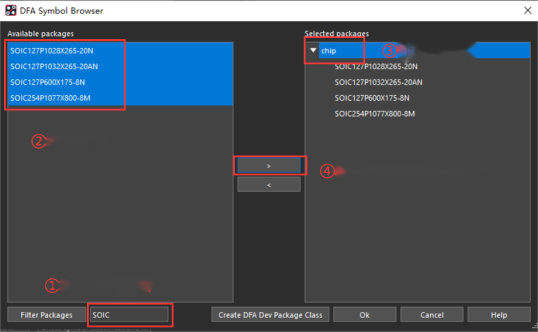

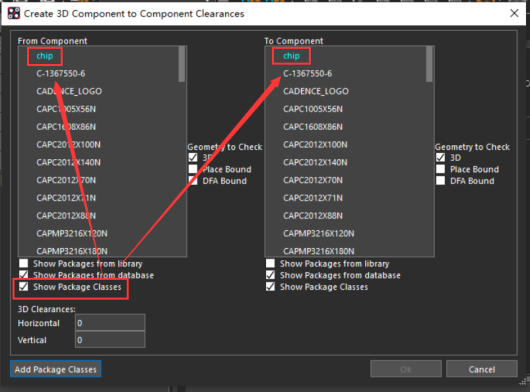

说明:除了可以设置封装与封装的间距规则,也可以通过如下图5、6和7所示方式,创建封装类,设置封装类相关规则。

图5创建封装类

图6 将封装添加到封装类

图7 添加的封装类显示到创建约束集界面

步骤五:如图8所示,选择要检查3D Clearance的器件封装或者封装类(From Component栏和To Component栏均支持多选,可以通过拖动鼠标左键或者Shift+左键多选封装),设置水平和垂直距离,点击OK,则Component to Component约束集创建成功,效果如图9所示。

图8约束集设置

图9 约束集设置完成

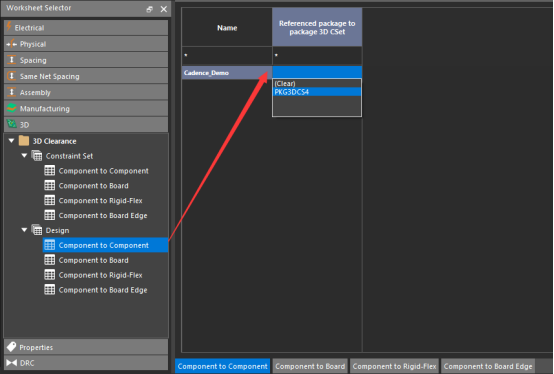

步骤六:约束集配置完成后,选择Design下的Component to Component,为设计选择对应约束集即可,如图10所示。

图10 选择3D约束集

二、Analysis Mode设置

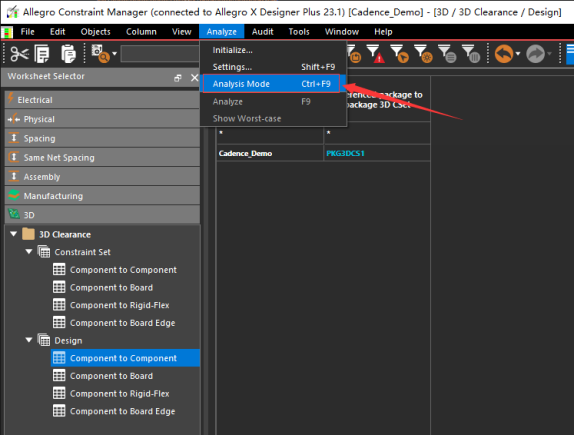

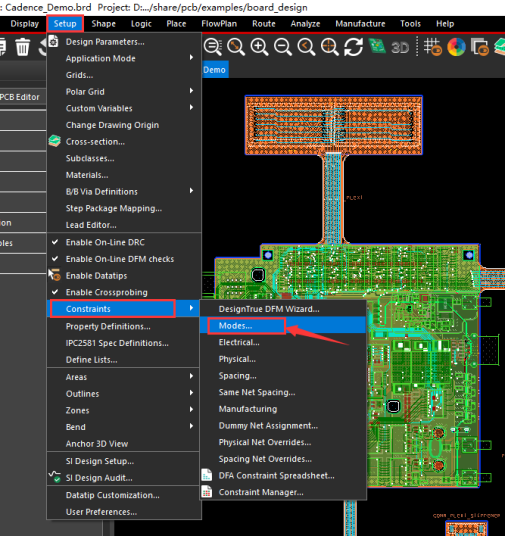

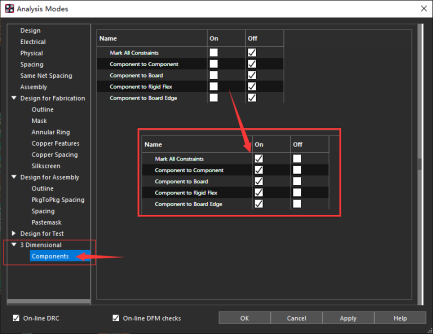

步骤一:在约束管理器菜单栏中依次选择【Analyze】→【Analysis Mode】,或是在PCB菜单栏中,依次选择【Setup】→【Constraints】→【Modes...】,打开Analysis Modes设置窗口,如图11和12所示。

图11 在约束管理器中打开Analysis Modes设置窗口

图12 在PCB界面中打开Analysis Modes设置窗口

步骤二:在Analysis Modes设置窗口中,选择”3 Dimensional”下的“Components”,然后在右侧将要检查的规则勾选为”ON”,点击OK即可,如图13所示。勾选”Mark All Constraints”即可设置该页面所有规则。

图13 勾选要检查的规则

三、查看3D布局DRC结果

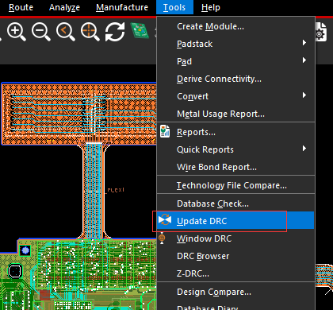

步骤一:在PCB菜单栏中依次选择【Tools】→【Update DRC】,如图14所示。

图14 更新DRC

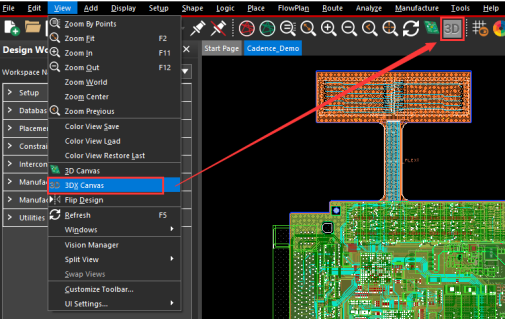

步骤二:然后在PCB菜单栏中依次选择【View】→【3DX Canvas】,或者在工具栏中直接点击3DX图标,如图15所示。

图15 选择3DX Canvas菜单

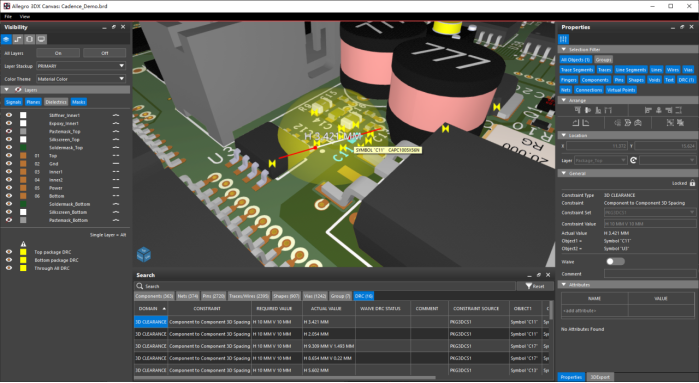

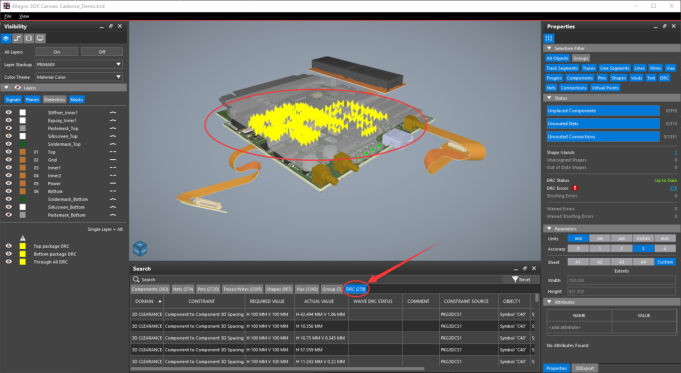

步骤三:在弹出的3DX Canvas界面就可以同步显示3D布局DRC的检查结果,如图16所示。

图16 3DX Canvas界面下的3D布局DRC结果显示

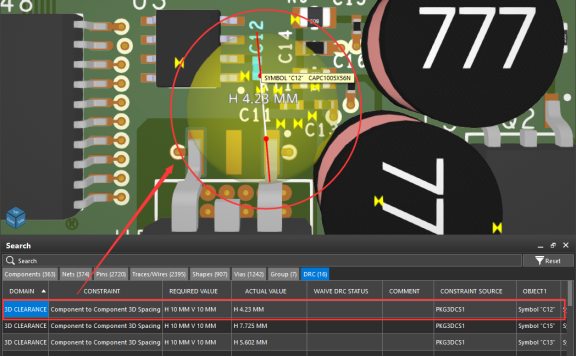

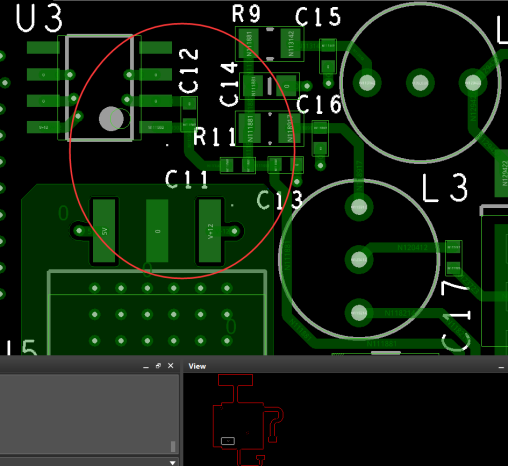

步骤四:在DRC分页中,点击错误信息,会在3DX Canvas界面自动跳转到错误所在位置,同时PCB界面也会同步调整至错误所在区域,如图17、18所示。

图17 3DX Canvas中跳转到错误所在位置

图18 PCB界面同步跳转到错误所在位置

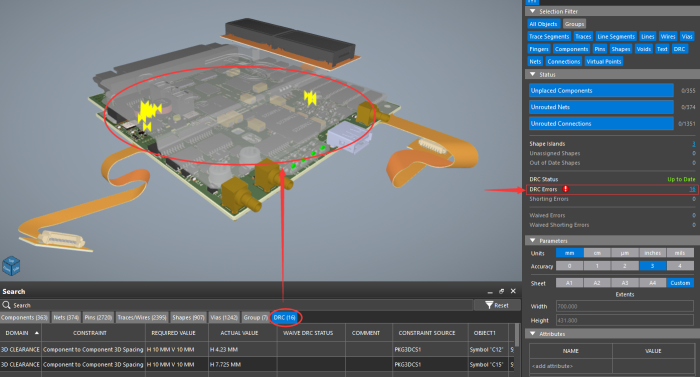

步骤五:我们根据3D布局DRC的报错信息,对PCB进行调整后,重新执行Update DRC操作,3DX Canvas界面会进行同步更新,效果如图19所示。

图19 3DX Canvas界面同步更新后的DRC情况

四、小结

本节主要介绍了如何在Allegro X PCB设计工具中,对3D布局DRC的约束集进行配置,然后利用3DX Canvas界面,对PCB的3D布局进行检查和调整,帮助设计人员提升PCB布局合理性,提高设计的可靠性和可制造性。