同步buck型降压DCDC芯片外围电路详解

参考资料:

嵌入式-硬件-DCDC(BUCK)电路分析_dcdc buck-CSDN博客

本文的目的,学习buck DCDC基本原理,然后使用厂商的DCDC芯片、或DCDC控制器芯片,加上所需的外围电路,制作出自己的DCDC降压模块。本文不涉及深入的数学计算,只做应用级的概述。

毕竟比葫芦画瓢,跟着厂商的芯片数据手册直接画原理图和PCB,搞不懂原理让人很慌,怕产品会出问题,只有了解了内部机理,才能知道PCB布线的坑在哪里。

1、基本原理

上图左是异步BUCK,右图是同步BUCK。右边使用元件较多,一个实际的降压模块,左边一般20多个元件,右边得30多个,但是效率高,发热小。同样输出功率的前提下,虽然右边元件多,但是因为效率高,可以使用封装更小的元器件,实际设计出的PCB仍然会比左边小。右边除了成本略高,其他方面比如性能、PCB布局面积、转换效率,都比左边好。左边只有一个优点,成本略低,对成本敏感,PCB面积大一点也无所谓的产品,左边更好。

先来看下基本原理:

以左边为例,Q1是MOS,且大多是NMOS,D1是肖特基二极管,特点是正向压降小,可以减小Q1关闭后的损耗。

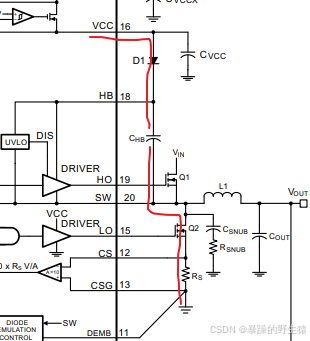

Q1导通后,会给L1充电,电流流向是:电源正极->Q1->L1->负载->GND,如上图红色线所示。

Q1关闭后,由于电感电流不能突变,L1会继续给负载供电,电流流向是:L1->负载->D1,如上图绿色线所示。二极管的作用是在L1给负载供电时,提供回流路径,所以叫“续流二极管”。

根据伏秒平衡原则,控制Q1的通/断时间的比例,就可以控制输出电压。

虽然肖特基二极管比普通二极管正向压降低,但是损耗仍然很大,所以才有了右图,用另一个NMOS(Q2所示)取代二极管,提供续流功能。

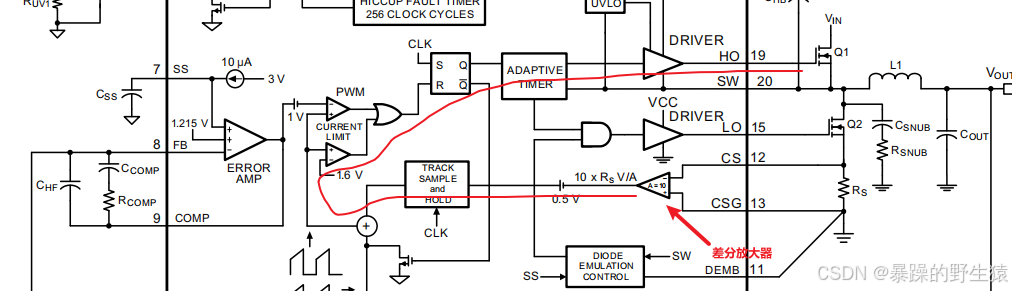

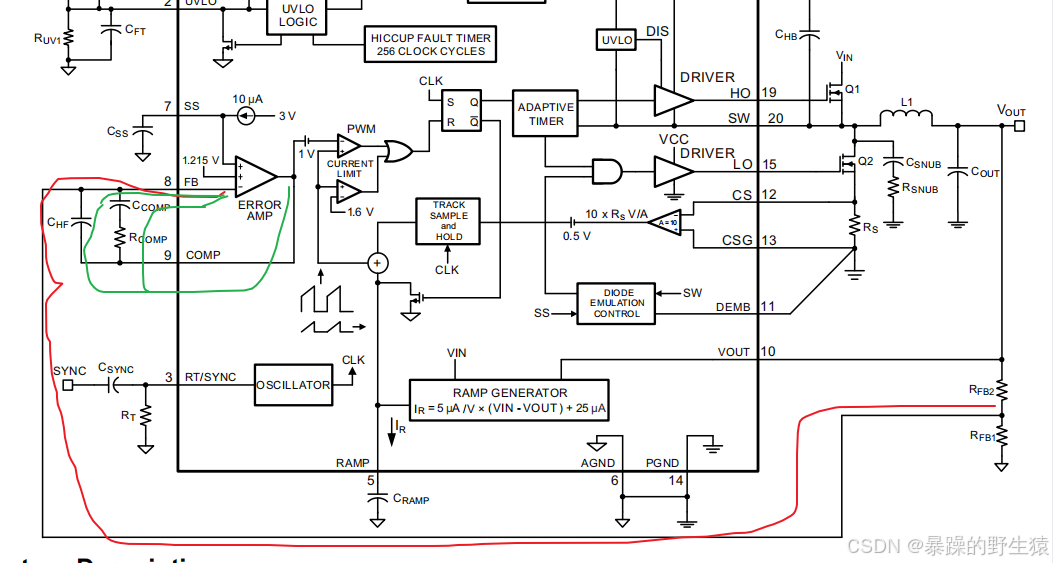

Q1的通电时间,是由DCDC芯片内部控制逻辑电路控制的,DCDC芯片都有个FB引脚,也即feedback负反馈引脚,可以实时采集输出电压的变化,如果输出电压低于设定值,就会让Q1导通,进行充电以便提高输出电压;反之亦然。判定是低于还是高于,靠的是DCDC芯片内部的一个比较器,比较器有两个输入,一个是基准电压(比如1.2V,不同的芯片有所不同),另一个就是FB引脚的电压,如下图所示,然后经过误差放大器(下图ERROR AMP所示),这就是个最简单的P比例控制。当然下图这个逻辑器的功能更强,又增加了第3个输入:SS(Soft-Start)软启动功能,当然这个功能不是DCDC标配,暂且不表。

图 DCDC芯片内部原理示意图

上图来自TI的DCDC控制器数据手册,型号见上图标识。

2、为什么不用PMOS

同步BUCK一般会用两个NMOS,如上图。

(1)PMOS的导通电阻R_ds_on比NMOS高,所以损耗大。注:_ds代表D和S之间,_on代表导通。

(2)NMOS的开关速度比PMOS快,这也有助于减小损耗,众所众知,MOS的损耗主要发生在开关瞬间,也即半打开的状态时。

(3)同样指标参数下,PMOS更贵,成本高。

3、2个NMOS的使用方法

先来回顾一下NMOS的导通条件:G极电压需超过S极电压一定范围(数据手册中一般标记为VGSth,threshold),D和S之间才能导通。大多数MOS的VGSth在2~3V左右。

NMOS日常使用中有2个常用规则:(1)负载一般放在MOS的D端,S端接地,这样G极只需要少许电压即可导通DS。(2)一般让电流从D->S。

不过在DCDC的外围电路中,以上2个规则,都分别被Q1和Q2被打破了。。。下面分别介绍:

(1)高侧的NMOS,也即上图的Q1,电感和负载都接在了S极,这种情况下,由于S极的对地电压为VOUT+VL,G极需要>=VOUT+VL+VGSth,才能导通,不是2~3V电压就能搞定的,这个要求过于苛刻。在DCDC中是这样解决的:增加一个自举电路,把G极电压抬到很高,这样就能满足导通条件了。

在前面的DCDC原理框图中,我们可以看到第PIN16_VCC和PIN18_HB之间有个二极管,这个叫自举二极管,在HB和PIN20_SW之间有个电容叫CHB,叫自举电容了。他们负责给Q1的栅极提供大驱动电流。由于SW接的就是Q1的S极,CHB的能量就会加在MOS的GS上,促进MOS的导通。

(2)Q2是用来在Q1关断时,给电感和负载提供续流回路的,电流的流向是S->D。自己搜索一下关键词【MOS的双向导通性】就知道了。原来我们平时的常规用法束缚了思想,MOS只要满足G极和S极的电压要求,D和S之间就会变成一根存在小电阻的导线,电流是可以双向流动的。下面是英飞凌的知乎官号的一个回答。

4、高侧MOS也可以使用PMOS

前面说了,市面上大多数同步BUCK DCDC芯片都设计成了使用两个NMOS,但也不是绝对的,

例如美国MPS(芯源半导体)的MP2162A、MP2158A这两个DCDC芯片,它的高侧MOS就选用了PMOS,这时就不需要自举电路了。

5、自举电路

把前面大框图的自举电路部分单独截图出来看看,如下:

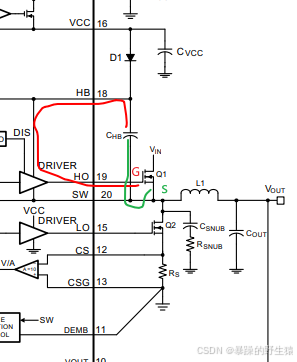

图左 CHB的充电路径 图右 CHB放电给Q1

Q1和Q2两者的通断是互斥的,当Q1关闭时,Q2会被打开。

电路组成与连接:自举电路主要由 HB 引脚、SW 引脚、外部自举二极管(图中的 D1)和自举电容(图中的CHB)构成。HB 引脚连接自举二极管阴极与自举电容正极,SW 引脚连接自举电容负极和高侧 MOSFET 源极。

充电过程:在高侧 MOSFET Q1关断期间,低侧MOS Q2会打开,此时SW 引脚电压约Q2内阻和电流采样电阻Rs的分压,Q2内阻和Rs都是毫欧级别,所以SW的电压一般为负0.x伏。此时,VCC 通过外部自举二极管D1向自举电容CHB充电,使电容储存电荷。由于自举电容与高侧 MOSFET 栅极G相连,其充电后的电压为 VCC 减去二极管正向导通压降,这个电压是比较高的,一般为10几伏。

驱动工作:当控制器发出指令使高侧 MOSFET 导通时,自举电容的两端会被上图的DRIVE模块跨接在HB引脚和SW引脚上,也即Q1的G极和S极之间,自举电容向Q1的栅极G放电,提供足够的栅极驱动电压和电流,使高侧 MOS迅速导通。在高 PWM 占空比工作时,为确保自举电容能充分充电,控制器会强制高侧 MOSFET 每个周期关断 几百ns,保证自举电容有足够时间从 VCC 充电,维持高侧 MOSFET 稳定的驱动电压,从而保证电路正常工作。

这里的自举二极管D1的作用主要是防止电流回灌,比如SW引脚的电压会随着Q1 Q2的开关而发生剧烈跳变,SW的电压可以达到Vin的高度,如果没有D1,必然会给CHB反向充电,导致电流从SW流向VCC,造成VCC电压不稳定。

6、电流采样

上图中看到有个采样电阻Rs,这就是个最简单不过的电流采样电路了,通过测量电阻Rs上的电压,然后DCDC内部除以Rs的阻值,就能知道电流了。众所周知的原因,采样电阻不能取得太大,如果太大的话,有2个坏处,一是发热太大,输出没用的纯损耗,二是分压太大,影响负载的分压。Rs一般取几毫欧,这样Rs的分压也就0.0x伏,甚至0.00x伏,这样分压极小,发热也极小,要想测量这么小的电阻分压,可以用差分放大器,把差分电压放大到适合ADC输入的范围。实际上DCDC内部就是这么做的。

DCDC一旦获得了电流值,就可以做出有用的功能:限制电流上限、做恒流闭环控制、做短路保护等。这些动作都可以通过对Q1的开关控制来实现。

如上图红线所示。上图中的算是比较简单的逻辑,差分电压被放大后,经过一个名为【电流限制CURRENT LIMIT】的比较门,如果超过限制,这个门输出1,后面连接的是一个或门,这样或门就会输出1,或门又接到了触发器的Reset上,这样触发器的输出Q就会关闭,最终传递到MOS Q1被关闭。

7、FB与COMP引脚之间的反馈补偿网络

FB引脚反馈的电压,会被DCDC内部用作负反馈,这就是个最简单的闭环控制,前面已经讲过了。但是FB引脚和COMP引脚之间还接了3个元件CHF/ CCOMP / RCOMP,这个电路叫type II 补偿网络。顺便科普下以下三种补偿网络,实际上用type II 效果就已经很棒了。type III最强,但是成本和设计复杂度就上来了。

(1)Type I 补偿网络

组成:通常由一个电容和一个电阻串联组成。

原理:它主要提供一个低频增益提升,适用于对带宽要求不高、负载变化缓慢的场合。电容在低频时呈现高阻抗,使得低频信号能够得到较大的放大,而在高频时电容阻抗变小,增益下降。

(2)Type II 补偿网络

组成:由一个电容与一个电阻串联后再与另一个电容并联组成。

原理:在 Type I 的基础上增加了一个零点和一个极点。零点可以提升中频段的增益,改善系统的动态响应;极点则用于在高频段降低增益,保证系统的稳定性。

(3)Type III 补偿网络

组成:结构相对复杂,包含多个电阻和电容。

原理:它具有两个零点和两个极点,可以更精确地调整控制环路的增益和相位特性。在中低频段提供较高的增益以保证稳态精度,在高频段迅速降低增益以避免振荡,同时在较宽的频率范围内保持合适的相位裕度。

补偿的详解可参考”安森美半导体“官号的一篇文章:《考量运算放大器在Type-2补偿器中的动态响应》考量运算放大器在Type-2补偿器中的动态响应(第一篇)-电子发烧友网

在没有补偿网络时,这就是个纯P控制,对于0型系统,P控制是存在静态误差的。而加上type I,就会变成PI控制,可以消除静态误差,type II是PID控制,学过《自控原理》的同学应该再熟悉不过了。

这个补偿网络值的单独写一篇,等后续再补吧。大体思路就是推导这个运放网络的传递函数,如果能推导出PID的标准型(out = kp * e + ki * ∫e + kd * e')就好了,过段时间试试。

实际上在没有补偿网络时,运放的输出就是out = kp * e = kp * (vref - vfb),这就是p控制啊,kp就是这个运放的增益。