动态功耗与静态功耗

0 英文缩写

- SOI(Silicon on Insulator)绝缘体上硅

- FET(Field-Effect Transistor)场效应管

- CMOS(Complementary Metal Oxide Semiconductor)互补金属氧化物半导体

1 功耗分类

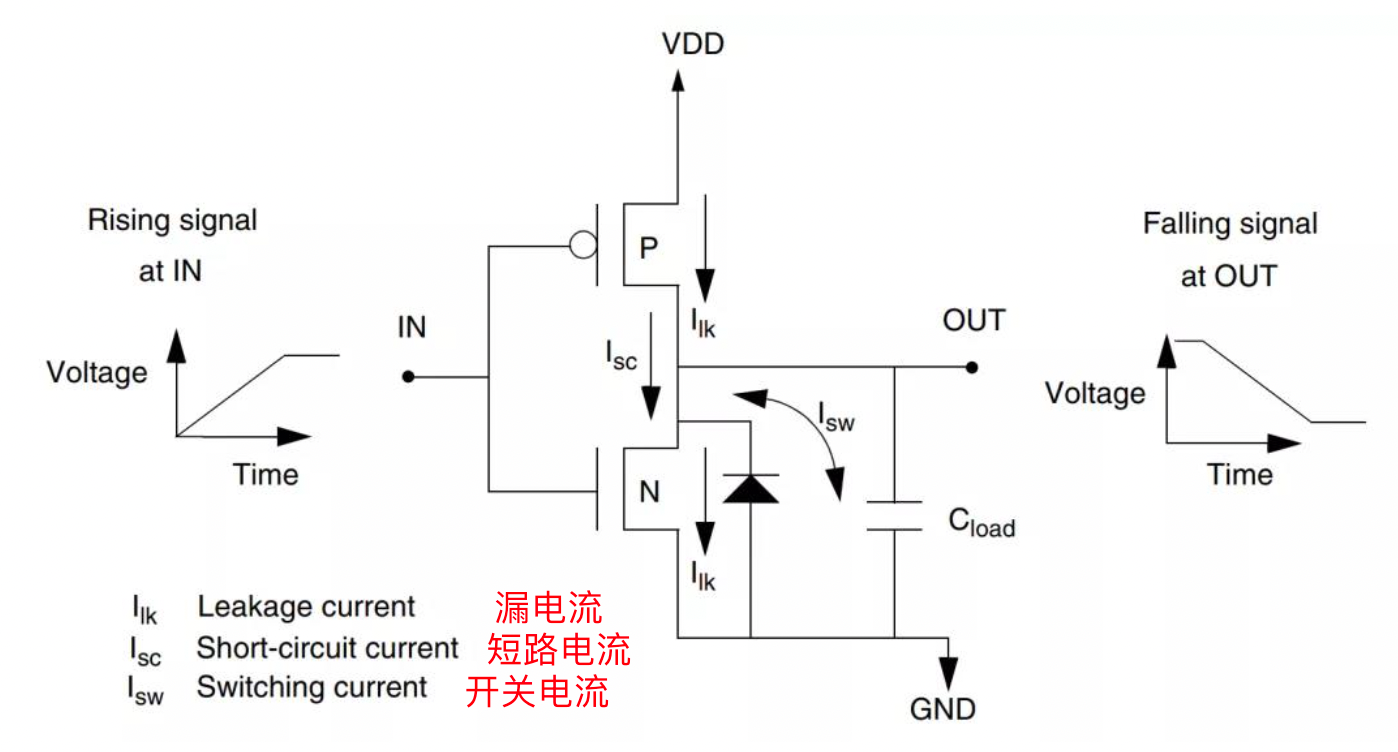

CMOS电路功耗主要可以通过如下方式切分:

- 动态功耗

- 开关功耗(又称为反转功耗)(switching power)

- 短路功耗(又称为内部功耗)(internal power)

- 静态功耗(也称为待机功耗、泄露功耗,包含有电路中晶体管的漏电流所导致的功耗)(Static Power、Leakage power)

2 动态功耗

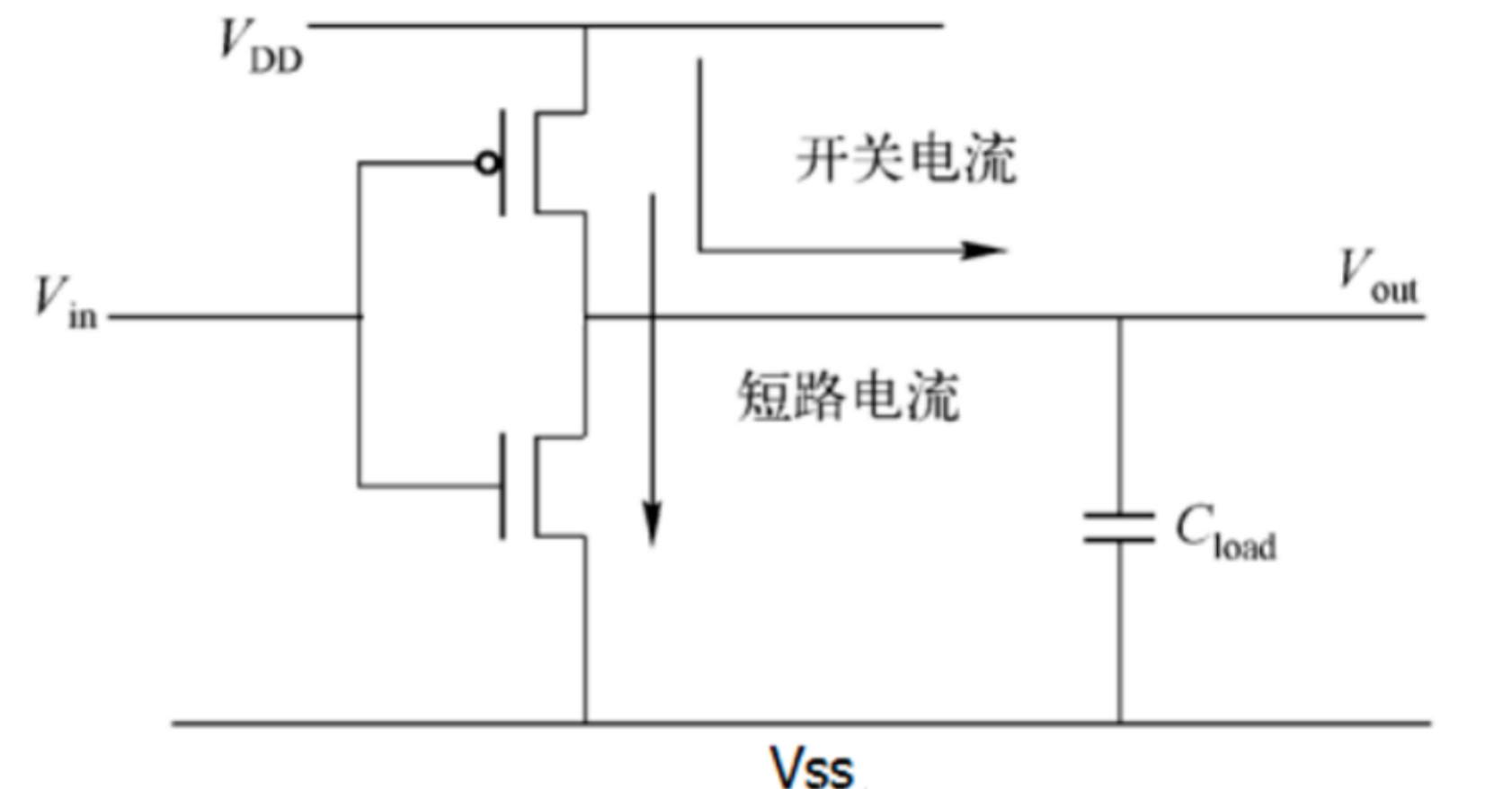

2.1 开关功耗

定义:电路在开关过程中对输出节点的负载电容充放电所消耗的功耗

比如对于下面的CMOS非门中:

- 当 V i n V_{in} Vin=0时,上面的PMOS管导通,下面的NMOS管截止; V D D V_{DD} VDD对负载电容 C l o a d C_{load} Cload进行充电

- 当 V i n V_{in} Vin=1时,上面的PMOS管截止,下面的NMOS管导通; V S S V_{SS} VSS对负载电容 C l o a d C_{load} Cload进行放电

这样开关的变化,电源的充放电,形成了开关功耗,开关功耗的计算公式如下

P switch = 1 2 V D D 2 ∗ C load ∗ T r P_{\text {switch }}=\frac{1}{2} V_{D D}^2 * C_{\text {load }} * T_r Pswitch =21VDD2∗Cload ∗Tr

V D D V_{D D} VDD为供电电压

C load C_{\text {load }} Cload 为后级电路等效的电容负载大小

T r T_r Tr为输入信号的翻转率,也有另外一种写法, f f f为时钟频率,一个周期信号翻转两次,所以这里没有 1/2

P switch = V D D 2 ∗ C load ∗ f P_{\text {switch }}=V_{D D}^2 * C_{\text {load }} * f Pswitch =VDD2∗Cload ∗f

通过这个式子可以发现只要有时钟,或者信号跳变,就存在动态功耗。

它与电路的工作频率成正比,与负载电容成正比,与电压的平方成正比。

开关功耗是由于电路对负载的充放电引起。同时负载会导致transition time的增加,从而影响短路功耗的增加。

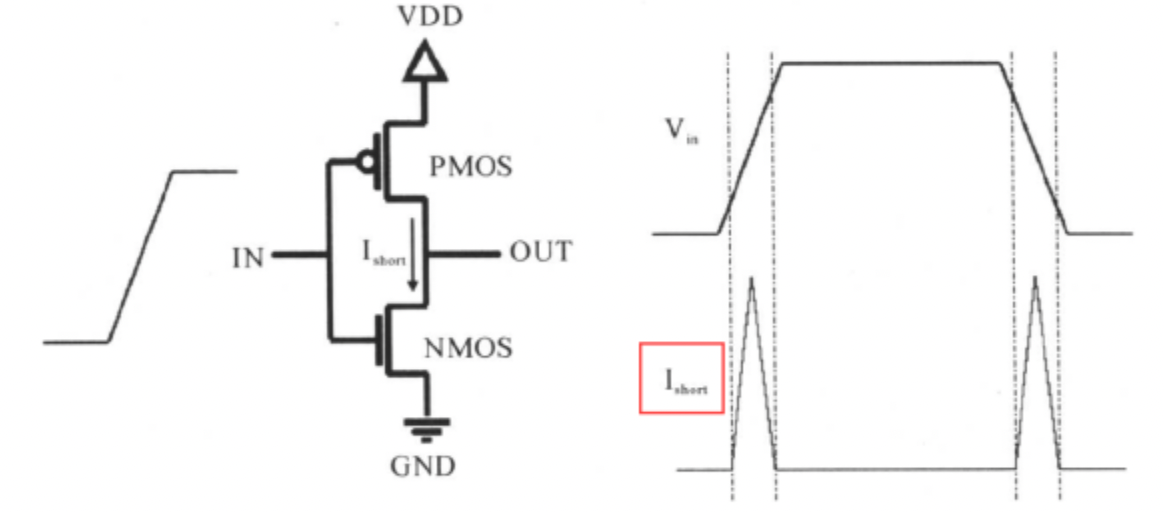

2.2 短路功耗

由于输入电压波形并不是理想的阶跃输入信号,有一定的上升时间和下降时间,在输入波形上升下降的过程中,在某个电压输入范围内,NMOS和PMOS管都导通,这时就会出现电源到地的直流导通电流,这就是开关过程中的短路功耗。短路功耗产生的条件一样是需要信号产生跳变。

当一个简单的cell的transition time非常长时,它的短路时间会变长,从而显著增加短路功耗。而对于一个复杂的cell,它的internal power有可能主要组成部分是对内部电容的充放电所组成。

3 静态功耗

3.0 简述

静态功耗是指电路在等待或者没有翻转情况下的功耗。 Static Power 与 CMOS的各种泄漏电流有关,静态功耗的概念非常重要,某种意义上它与MOS管本身的结构有关,受温度等外界温度的影响。它与频率无关,所以不能通过降频的方式降低静态功耗,同时Static Power与温度成指数关系,在温度较高时,Static Power会变得非常大。 Leakage Power可以从lib/db中得到,跟input pin的状态有关。

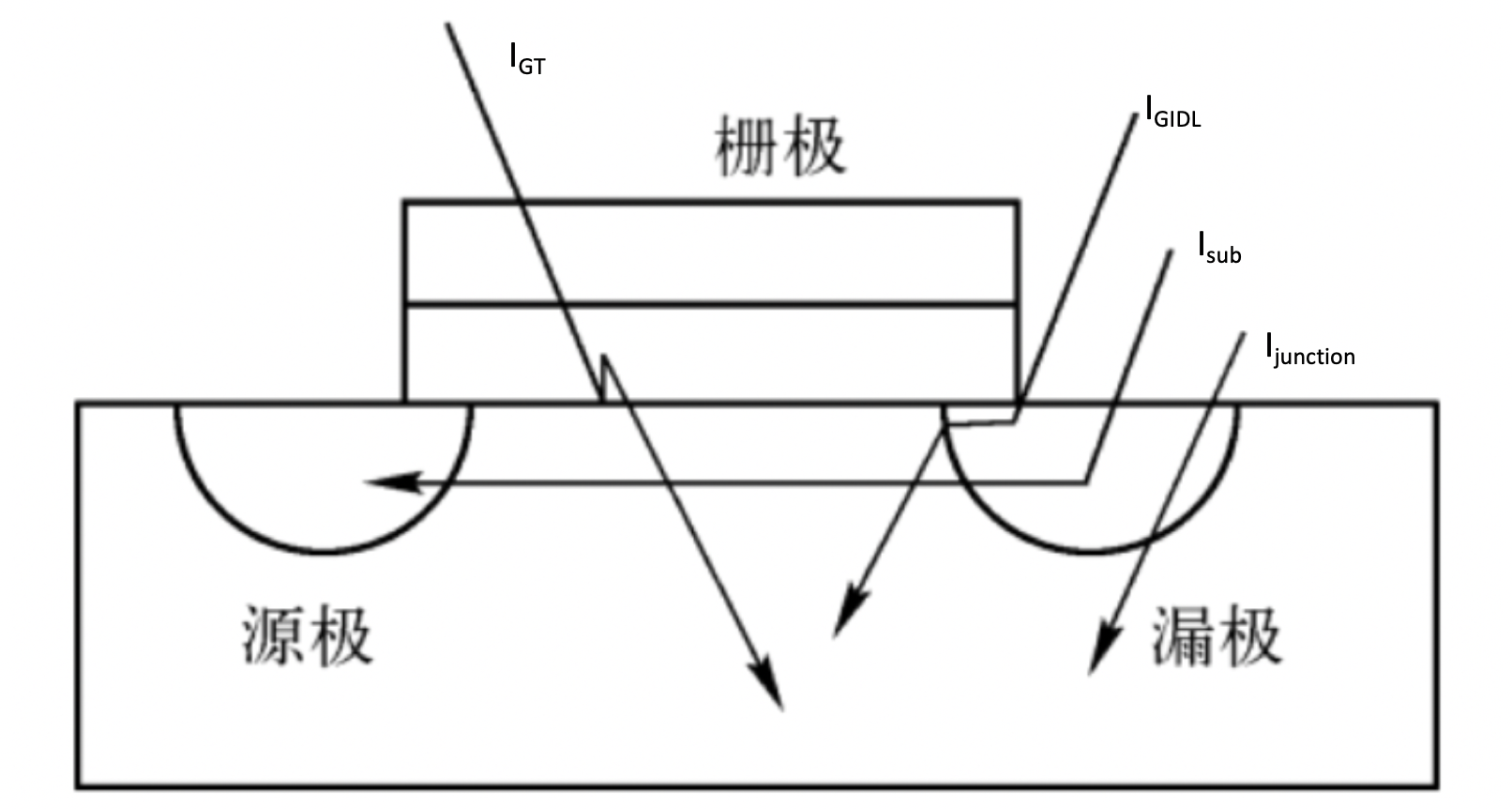

在CMOS电路中,静态功耗主要是漏电流引起的功耗。对于常规CMOS电路,在稳态时不存在直流导通电流,理想情况下静态功耗为0,但是由于泄露电流的存在,使得CMOS电路的静态功耗并不为0。一般情况下,漏电流主要是指栅极泄漏电流和亚阈值电流,CMOS泄露电流主要包括:

- PN结反向电流 I junction I_{\text {junction }} Ijunction

- 亚阈值漏电流 I sub I_\text{sub} Isub

- 栅极感应漏极泄漏 I GIDL I_\text{GIDL} IGIDL

- 栅极隧穿电流 I G T I_{GT} IGT

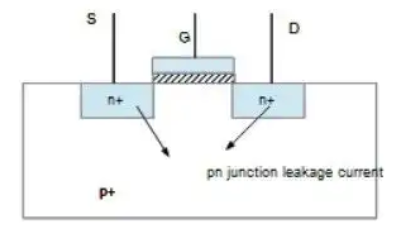

3.1 PN结反向电流( I junction I_{\text {junction }} Ijunction )

- 英文:PN-junction Reverse Current

- 成因:源/漏区与衬底形成的PN结在反偏时,耗尽区内的少子漂移和热生成载流子(反向饱和电流)。即为反偏二极管的泄漏电流。

- 公式: I junction ∝ e − q V b i / ( k T ) ⋅ V R I_{\text {junction }} \propto e^{-q V_{b i} /(k T)} \cdot \sqrt{V_R} Ijunction ∝e−qVbi/(kT)⋅VR

- V b i V_{b i} Vbi为内建电势

- V R V_R VR为反向偏压

- 抑制手段:

- 优化阱掺杂浓度

- 采用SOI(绝缘体上硅)技术消除衬底漏电路径

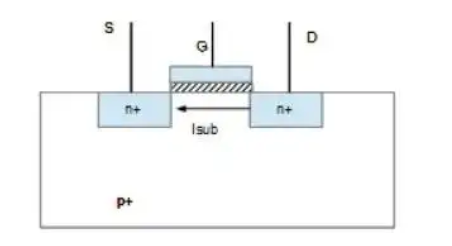

3.2 亚阈值漏电流( I sub I_\text{sub} Isub)

- 英文:Sub-threshold Current

- 成因:指源极和漏极之间的亚阈值泄漏电流,即为栅极电压低于导通阈值( V G S < V t h V_{G S}<V_{t h} VGS<Vth)时,仍会产生从FET漏极到源极的泄漏电流,是弱反型层电流(量子隧穿效应主导)。

- 公式: I sub ∝ e ( V G S − V t h ) / ( n ⋅ k T / q ) I_\text{sub} \propto e^{\left(V_{G S}-V_{t h}\right) /(n \cdot k T / q)} Isub∝e(VGS−Vth)/(n⋅kT/q)

- n n n 亚阈值摆幅因子

- V G S V_{G S} VGS 栅压

- V t h V_{t h} Vth 阈值电压

- 设计对策:

- 采用高阈值电压(HVT)器件

- 动态阈值调整(Body Biasing),通过衬底偏置进行增加阈值电压

- 电源门控(Power Gating)切断闲置模块供电

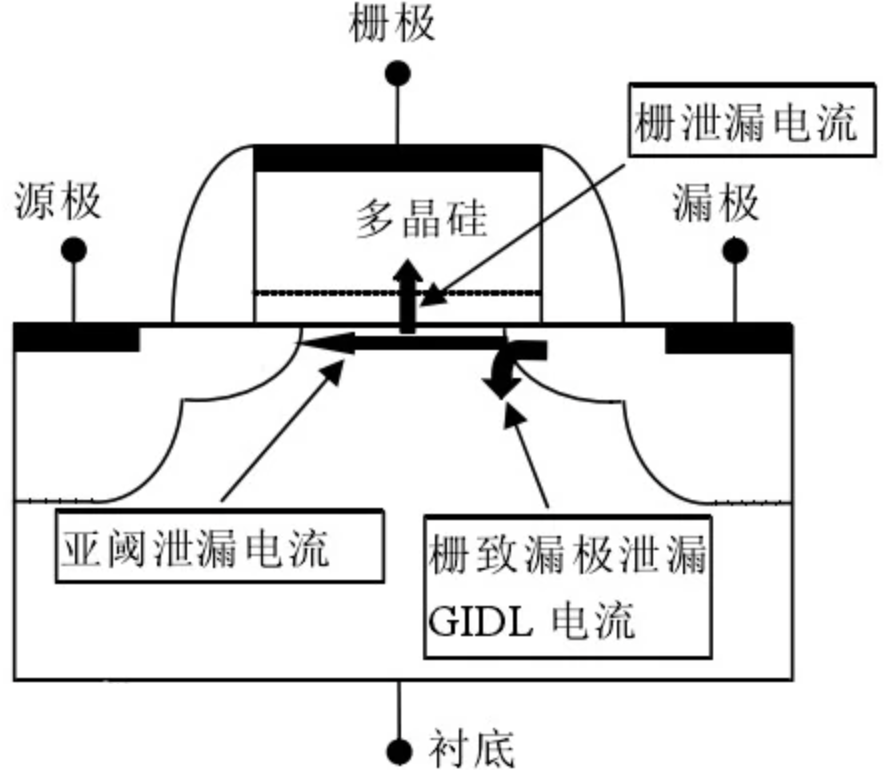

3.3 栅极感应漏极泄漏( I GIDL I_\text{GIDL} IGIDL)

- 英文:Gate Induced Drain Leakage

- 成因:高 V D S V_{DS} VDS下,漏极强反型导致栅-漏重叠区产生带间隧穿电流。在栅极上加信号后(即栅压),从栅到衬底之间存在电容,因此栅极和漏极之间存在感应漏电流,由此产生功耗。

- 触发条件:

- 深亚微米工艺(栅氧化层薄,电场强度高)

- 高漏极电压(如I/O接口电路)

- 缓解方案:

- 优化栅漏交叠区结构(如LDD轻掺杂漏)

- 降低工作电压(如从1.2V降至0.8V)

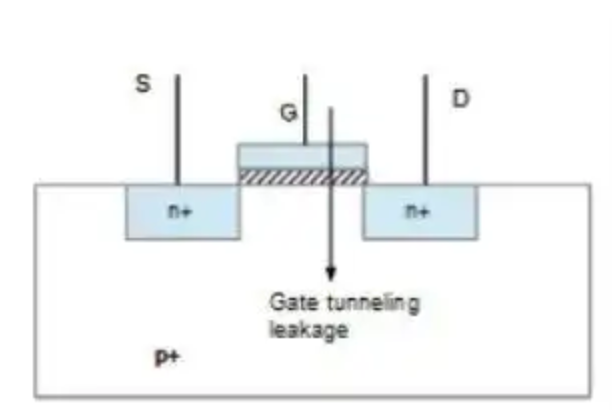

3.4 栅极隧穿电流( I G T I_{GT} IGT)

- 英文:Gate Tunneling Leakage

- 物理机制:栅极和衬底之间的隧道漏电流,超薄栅氧(<2nm)下,电子通过量子隧穿穿透栅介质层(直接隧穿/Fowler-Nordheim隧穿)。

- 公式: J t u n n e l ∝ E o x 2 ⋅ e − B / E o x J_{t u n n e l} \propto E_{o x}^2 \cdot e^{-B / E_{o x}} Jtunnel∝Eox2⋅e−B/Eox

- E o x E_{o x} Eox为栅氧电场强度

- B B B为材料相关常数

- 技术演进:

- 传统SiO₂ → High-K介质(如HfO₂)

- 金属栅(消除多晶硅耗尽效应)

3.5 静态功耗总结

静态功耗是深亚微米芯片设计的核心挑战之一,需从器件物理、电路架构、系统调度多层级协同优化。理解其微观机制(如量子隧穿)和宏观模型(如库文件参数化),是低功耗芯片设计的关键基础。

单个模块的静态功耗计算公式如下:

P leakage = ( I junction + I sub + I GIDL + I GT ) ∗ V D D P_\text {leakage } = (I_\text{junction}+I_\text{sub}+I_\text{GIDL}+I_\text{GT})*V_{DD} Pleakage =(Ijunction+Isub+IGIDL+IGT)∗VDD

整个芯片的静态功耗计算公式如下:

P static = ∑ i = 1 N ( P leakage , i ⋅ T active , i ) P_{\text {static }}=\sum_{i=1}^N\left(P_{\text {leakage}, i} \cdot T_{\text {active}, i}\right) Pstatic =i=1∑N(Pleakage,i⋅Tactive,i)

- T active , i T_{\text {active}, i} Tactive,i 为模块的上电活动时间占比

3.6 静态低功耗设计

当一个芯片温度过高时,一般采取什么措施是降频,降频的动作可以由控制系统自动完成。但是leakage不同于dynamic power,它与频率无关,所以降频对leakge power没有任何影响。

同时leakage与温度可成指数关系,当温度越高时,温度的影响越大。某些工艺下,90升至100度变化时,leakage可成十倍以上关系,leakage的暴增,导致温度进一步升高。形成恶性循环,直至芯片功能失效或烧毁。

这就是leakage power的可怕之处,也就是为什么我们需要非常谨慎的使用LVT ULVT,关注LVT比例。我在这里的建议是leakage功耗尽量控制在总功耗的15%以下(85°c)。

低功耗设计策略:

- 多阈值电压设计:关键路径用LVT,非关键路径用HVT

- 电源域划分:通过PMU动态关断闲置模块电源

Last 参考链接

- “IC常用知识4-静态功耗和动态功耗-CSDN博客”

- “为什么需要对芯片的leakage功耗特别关注? - 极术社区 - 连接开发者与智能计算生态”

- “(数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续) - IC_learner - 博客园”

- “数字电路低功耗设计-CSDN博客”

- “CMOS电路的功耗_cmos动态功耗-CSDN博客”

- “反向漏电流_百度百科”

- “GIDL_百度百科”

- “静态功耗 计算 - 春风一郎 - 博客园”

- “聊聊芯片中的静态功耗(Leakage Power)-CSDN博客”

- “CMOS IC功耗类型及其影响因素_芯片设计功耗组成和影响因素-CSDN博客”