昆明网站建设SEO公司网址最新连接查询

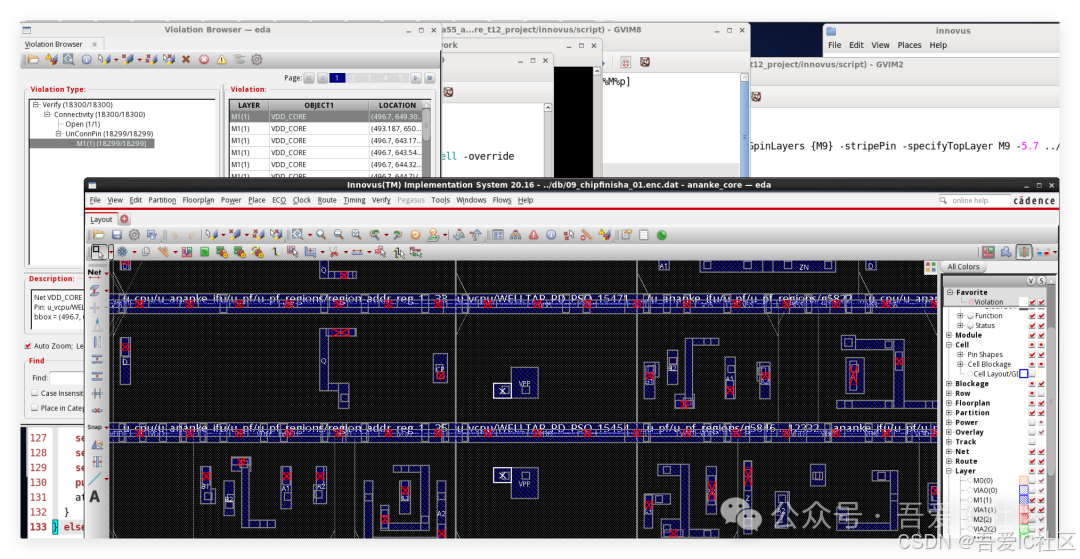

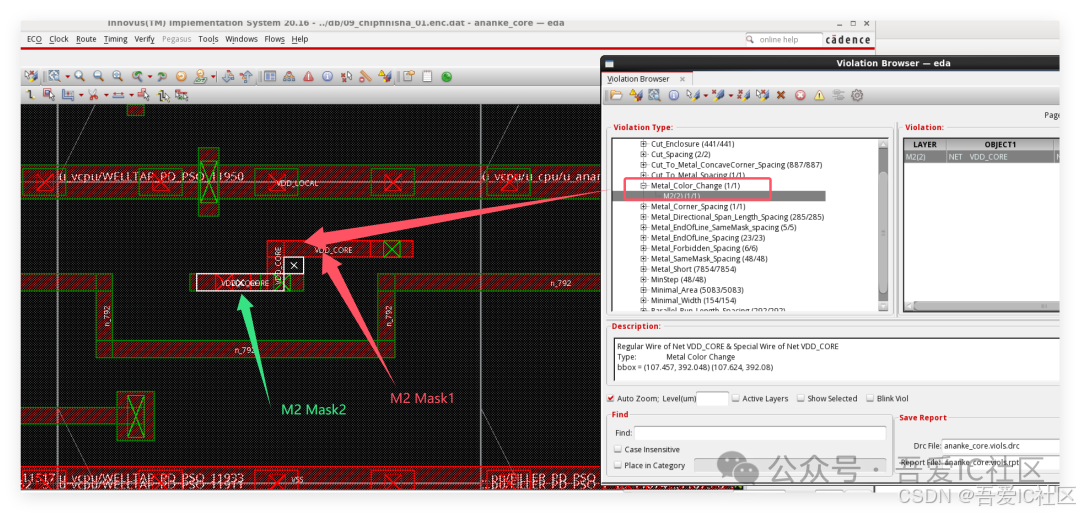

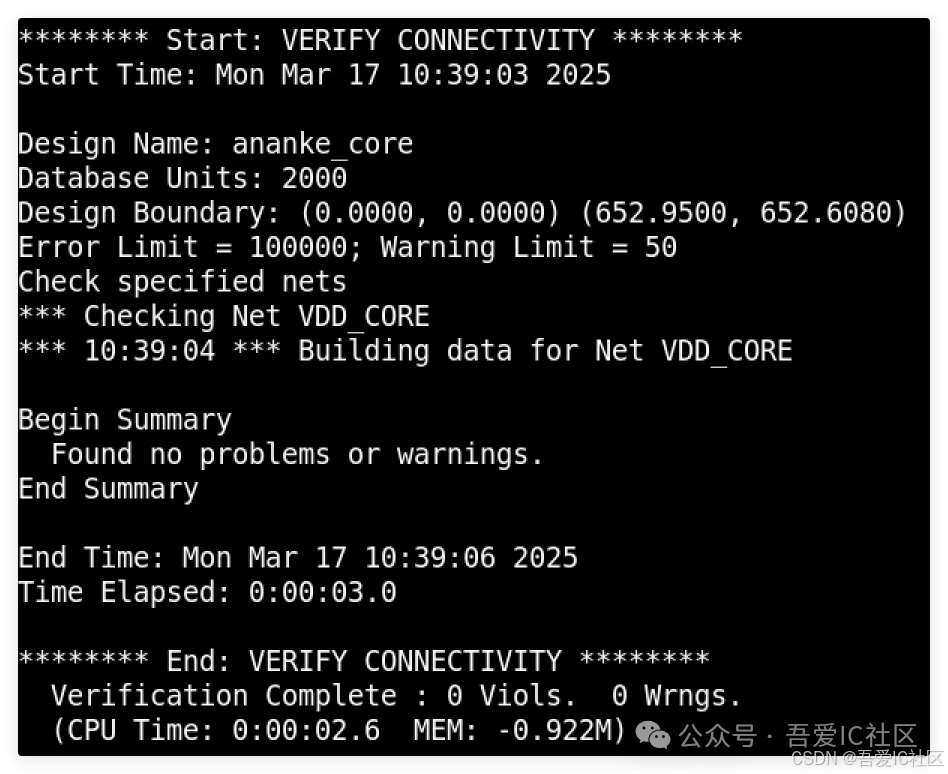

Q1:为了更高效过掉Calibre LVS,我们要求学员在chipfinish阶段需要先做Online LVS检查。该学员在做verifyConnectivity检查发现设计中存在大量的M1 VDD_CORE Un-Connect Pin的violation,具体violation如下图所示。

数字后端培训实战项目六大典型后端实现案例

根据Violation Browser可以很容易定位到这些violation都是出现在我们A55项目Tapcell上的M1 VPP Pin(Secondary PG Pin),而且的确这个M1 Pin没有和VDD_CORE有物理通路(缺VIA1)。

而我们项目的Secondary PG Pin走线是在powerplan阶段就做好的,为何这里会缺VIA1呢?

经过debug发现,powerplan.enc.dat中的确也有VIA1。但这个学员听咱们直播课一直强调powerplan做完后一定要做PG Connectivity检查并写GDS到Calibre 进行DRC检查这件事情,于是就开始插filler和添加dual power rail M1和M2之间的VIA1。

这个行为本身也没有问题,而且这个学员也记得这个加过dual power rail VIA1的项目数据仅仅是拿来验证PG连接性检查,但他在想不就一个VIA1嘛,我可以通过命令来批量删除。删除后仍然可以继续使用这个database来接着做后续其他流程。

set box [dbGet top.fPlan.box]

set via1_list [dbQuery -layers 1 -objType sViaInst -areas $box]dbDeleteObj $via1_list

但他没想到的是设计中除了power rail上存在 special net VIA1,Tapcell的Secondary Pin也有VIA1,而且也是special route的类型。

routePGPinUseSignalRoute -nets VDD_CORE -pattern trunk -maxFanout 8 -nonDefaultRule vddl_rule}

setAttribute -net VDD_CORE -skip_Routing trueconvertNetToSNet -net VDD_CORE

数字后端实现之Innovus中open net原因解析及解决方案

那既然Tapcell上的VIA1 VDD_CORE也被删了,我们是不是可以再重新对secondary pg pin VPP进行绕线呢?

routePGPinUseSignalRoute -nets VDD_CORE -pattern trunk -maxFanout 8 -nonDefaultRule vddl_rule

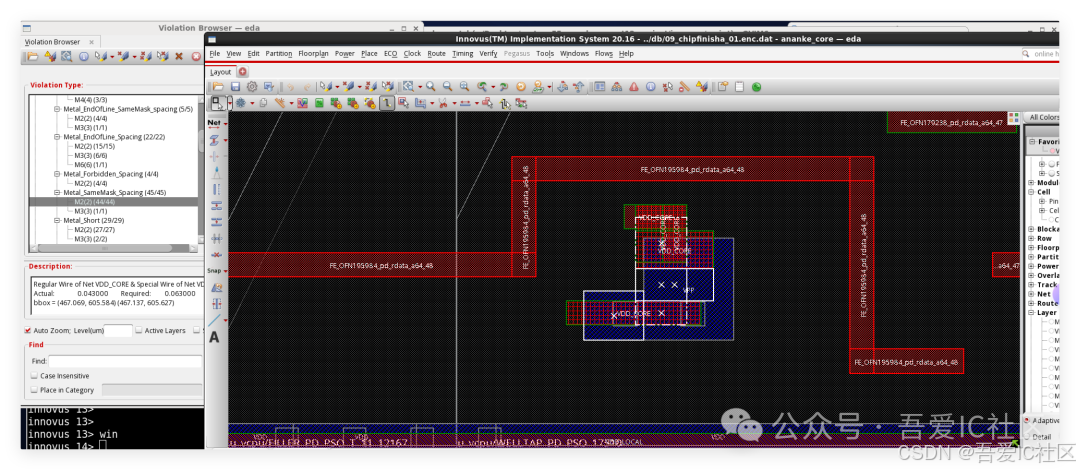

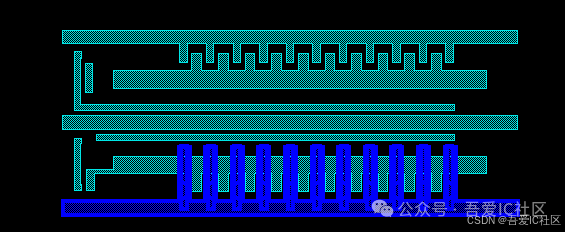

使用上述命令绕线后的结果如下图所示。

数字IC后端设计实现之分段长clock tree经典案例

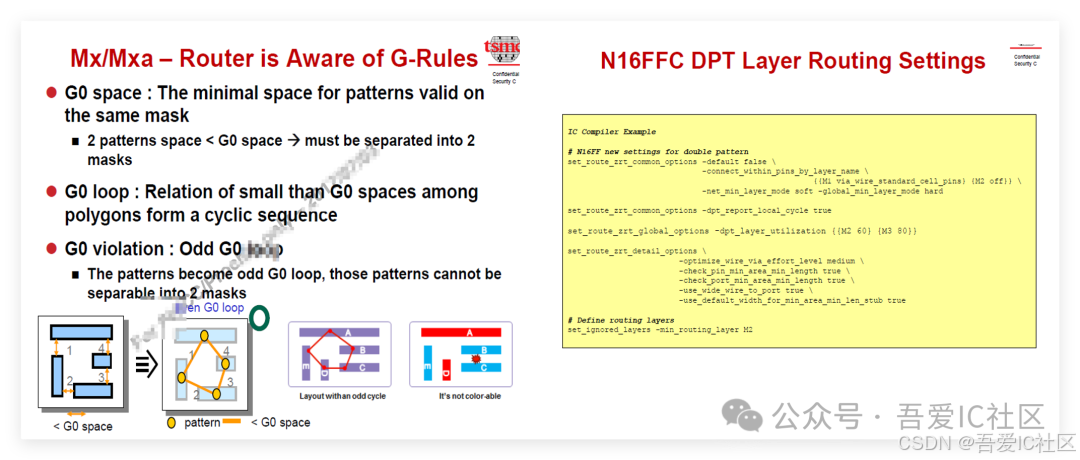

此时我们看到大量M2的drc violation。这里主要有两个原因:

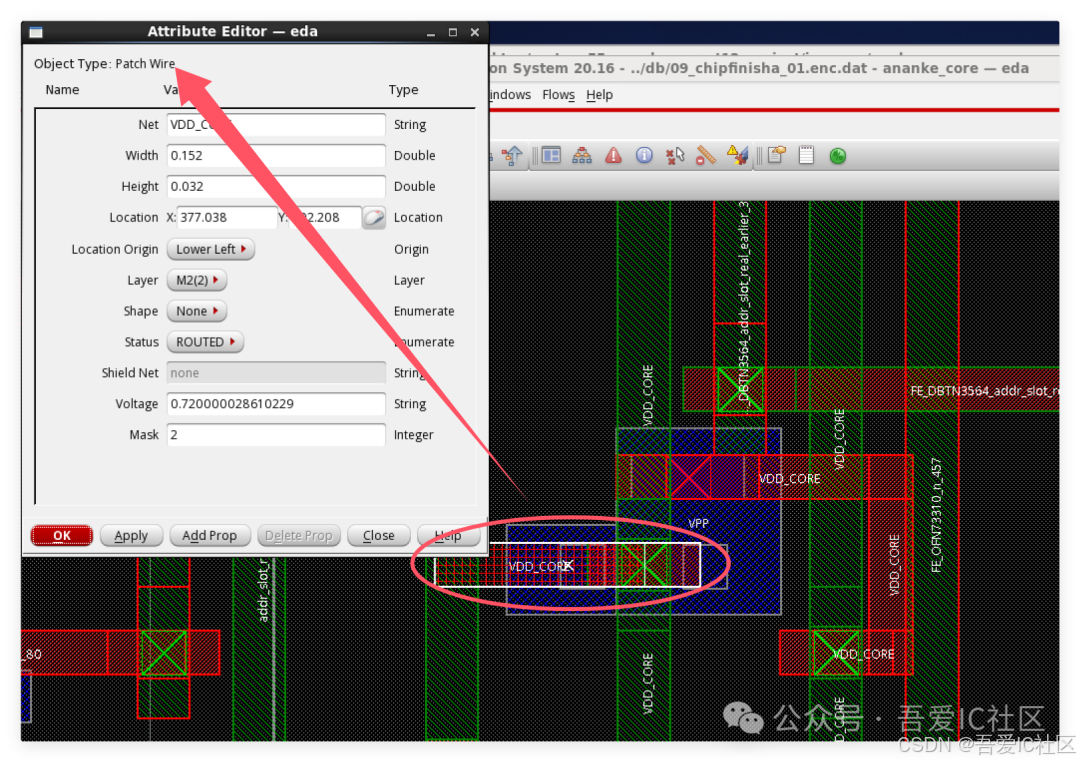

1)原来secondary pg pin走线部分的net shape类型是patch wire

2)当前设计已经有信号走线,新绕的PG Routing与现有的signal routing存在drc violation

而且细心的同学还能看到当前DRC Violation还存在不同color的M2间距不够问题。这个就是我们一直所说的un-colorable问题。

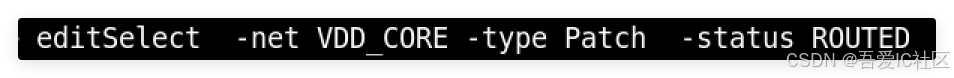

所以不能在现有chipfinish的数据中再做一遍VPP pin的绕线。如果非要这么做,必须提前把原来VPP pin对应的net routing删掉,然后再重新做secondary pg pin的routing。

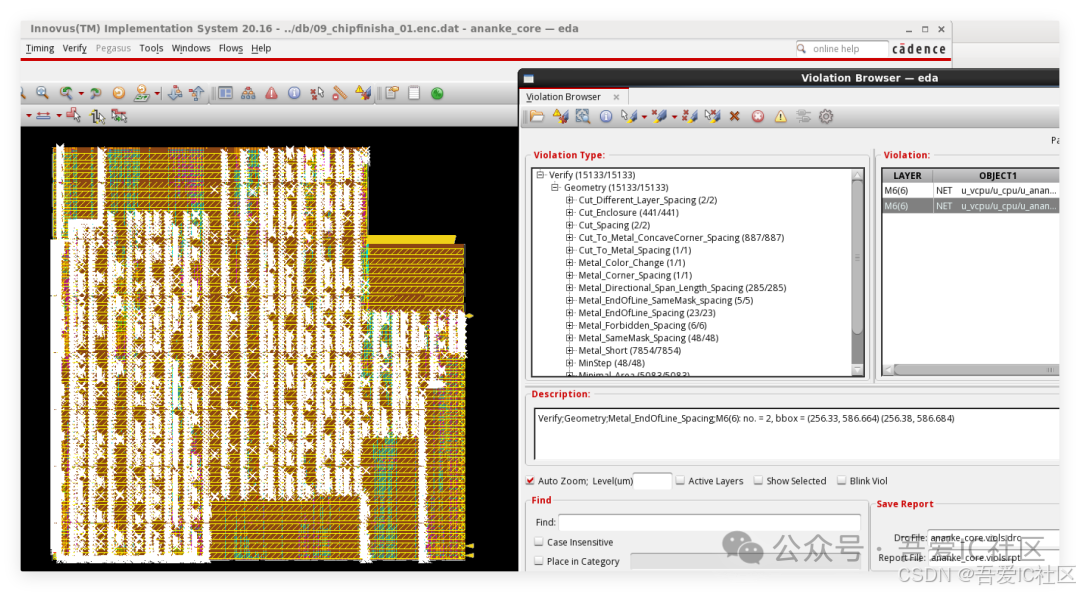

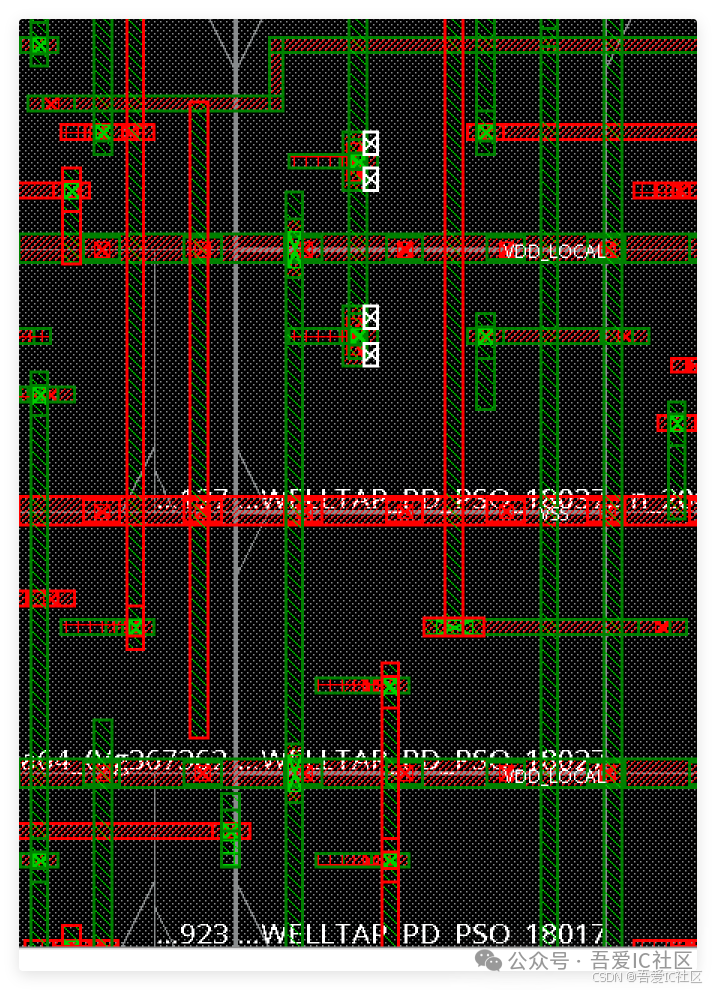

但你会发现即便这么做,你还会看到如下所示的drc violation——M2 min step violation。

仔细对比后你会发现部分VPP pin走线受边上信号线的影响,走出来的net shape pattern跟原来不一样了。

遇到这种情况还得根据DRC Violation Marker来筛选到影响到它走线的信号线。

那遇到本案例出现的VIA1丢失问题,我们是否还有更便捷的方法呢?

答案是有的。我们可以直接打开powerplan.enc.dat,通过defOut写出所有powerplan信息,再把这个def文件defIn到最新的database后重新做下ecoRoute即可。

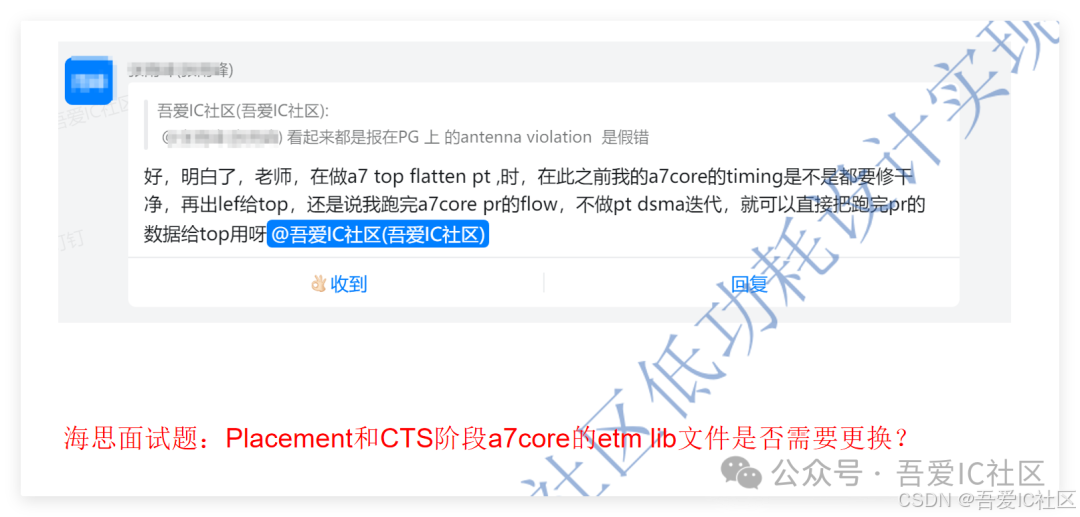

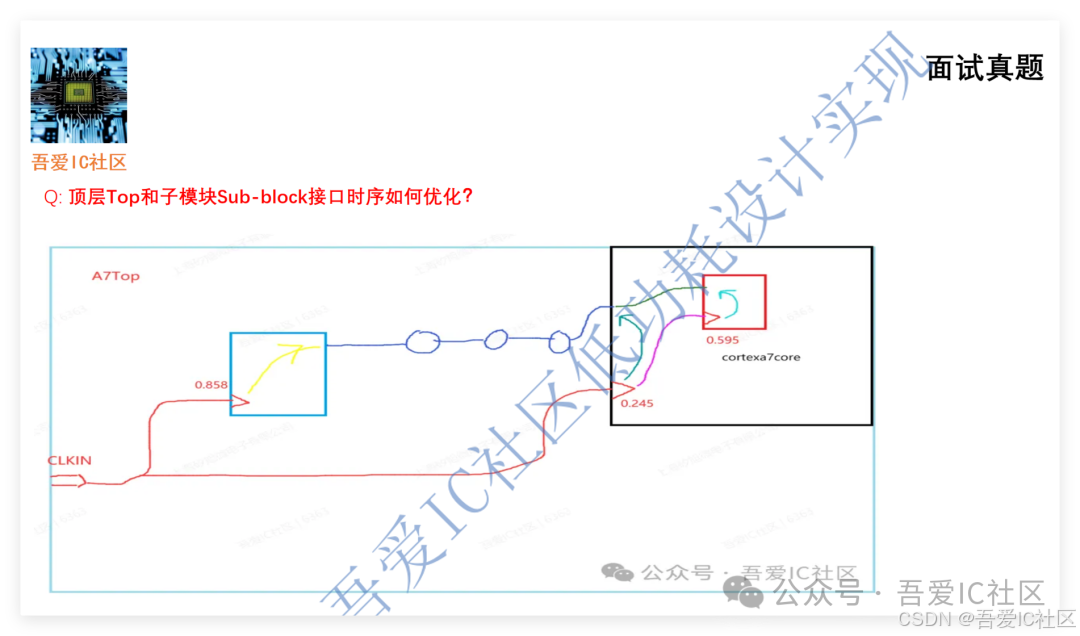

Q2: 在低功耗四核A7 Top Hierarchical Flow实现中,子模块cortexa7core的ETM Model应该使用ideal还是postCTS的?还有placement阶段和CTS阶段a7core的etm lib是否需要更换?如何更换?

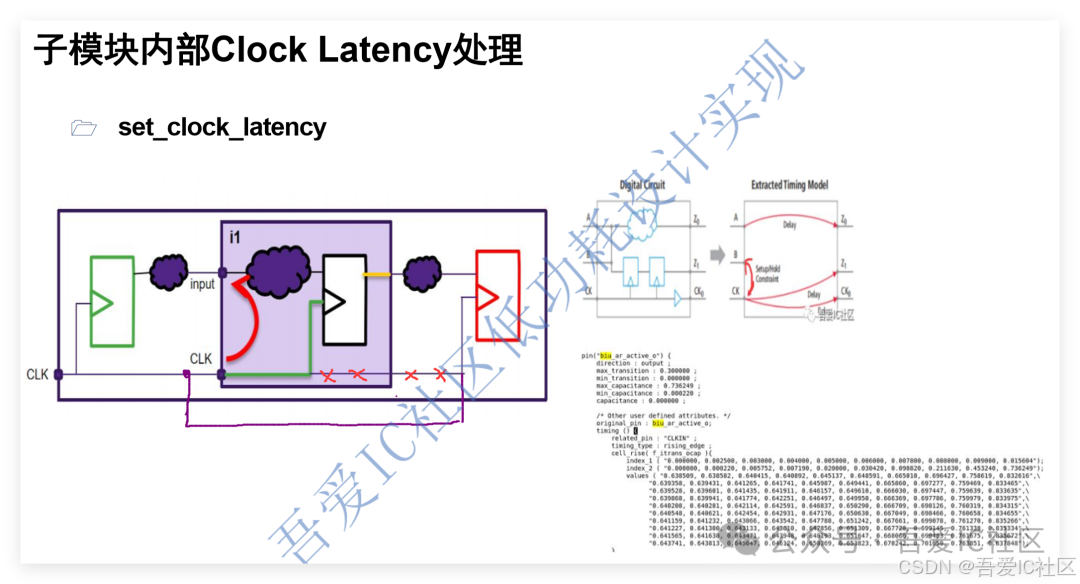

PreCTS阶段a7top可以使用子模块ideal的etm,此时不需要对子模块设置set_clock_latency。

如果这个阶段使用的是a7core postRoute的etm,那么就需要对cpu子模块设置一个负值的clock latency,其值约为子模块a7core内部clock tree的平均长度。

咱们社区a7top在preCTS阶段设置的子模块clock latency命令如下所示。

set_clock_latency -0.49 u_cortexa7/cortexa7core_0_u_cortexa7core_0/CLKIN

set_clock_latency -0.49 u_cortexa7/cortexa7core_1_u_cortexa7core_1/CLKIN

set_clock_latency -0.4 u_cortexa7/cortexa7core_2_u_cortexa7core_2/CLKIN

set_clock_latency -0.4 u_cortexa7/cortexa7core_3_u_cortexa7core_3/CLKIN

如果preCTS阶段使用的是子模块ideal etm,CTS阶段需要换成postRoute的etm。更换的方式可以使用类似mmmc创建方式,创建一个新的view即可。

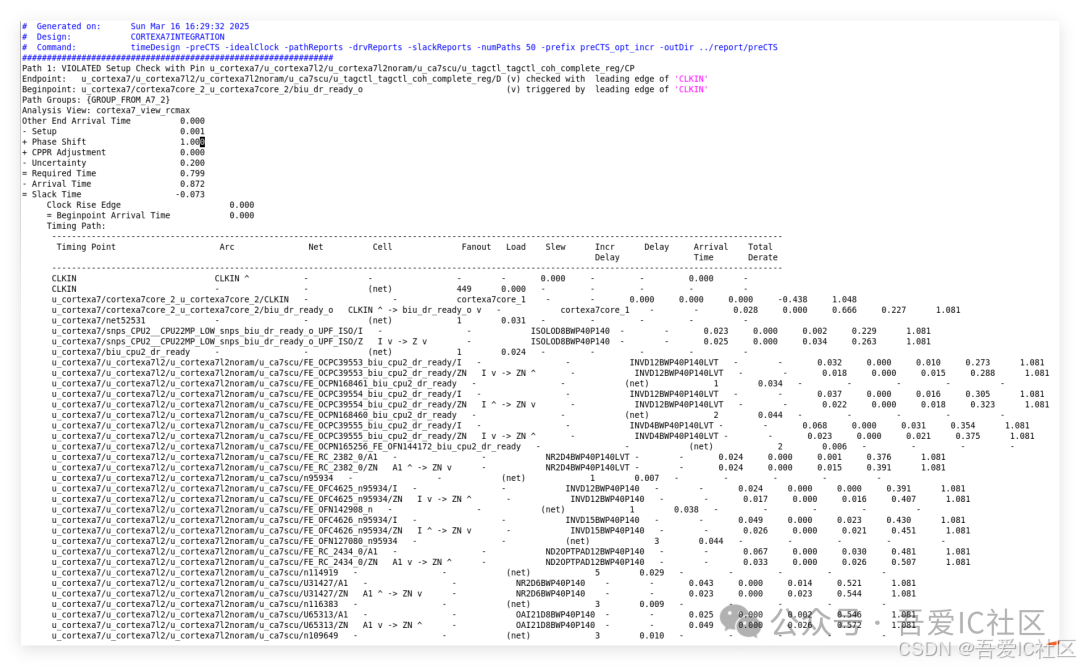

Q3:对于下图所示的从CPU2到A7 Top顶层寄存器D的一条timing path,它的WNS是-73ps。请问应该如何看这个timing report,以及如何修复这类timing path的violation?

时序优化可以从以下几方面入手:

1)cpu子模块reg到output data逻辑delay优化

2)把顶层与子模块相关的寄存器摆放至各个cpu门口,缩短a7top层data path路径

3)data path使用阈值电压更低的LVT

4)利用useful skew,给子模块cpu设置一个更小的clock latency

当前这条timing path是preCTS阶段的。如果后续CTS做完,我们还可以通过调整优化子模块CLK的insertion delay值来把clock skew做小来优化timing。

同样,对于a7top reg到子模块接口的timing path的优化方法也需要熟练掌握。

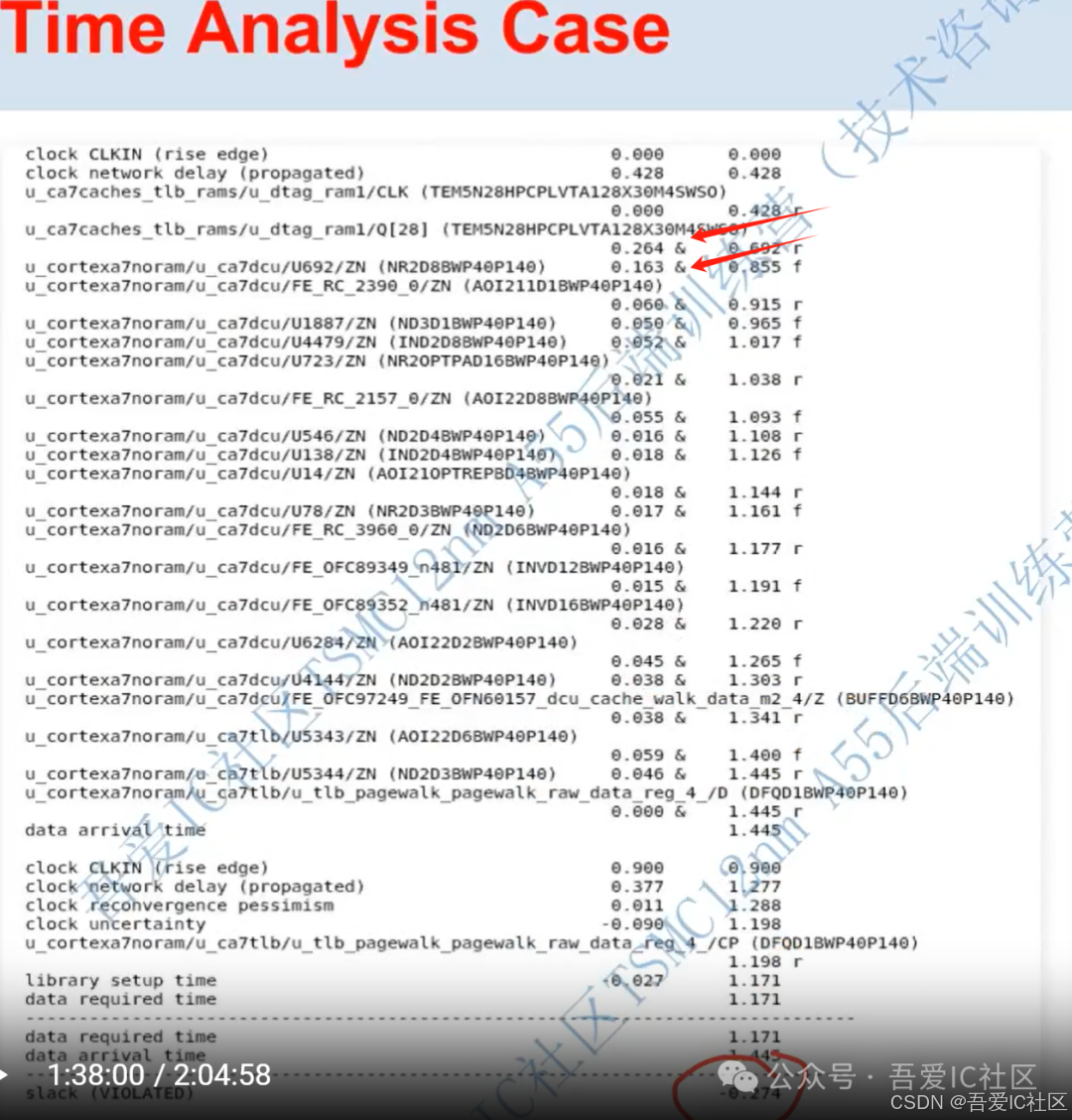

Q4: 对于老师直播课布置的这个作业,我的想法是:

1)箭头指的那两个cell的delay比较大,上面那个是reg,应该没办法,下面这个cell可以换一个更大尺寸的

2)去掉data path上的两个inverter

3)在pr阶段把clock uncertainty调大,让工具看到更大的违例

1)Memory CLK–Q的delay可以通过换High Speed的Memory来解决,但是leakage也更大

2)DCU module和TLB module摆放得更近一些,且均靠近tlb_tag_ddata_ram

3)把Memory的Clock Tree进一步做短(可以在CTS阶段做,也可以通过Clock Tree ECO来实现)

4)使用部分LVT来换RVT cell

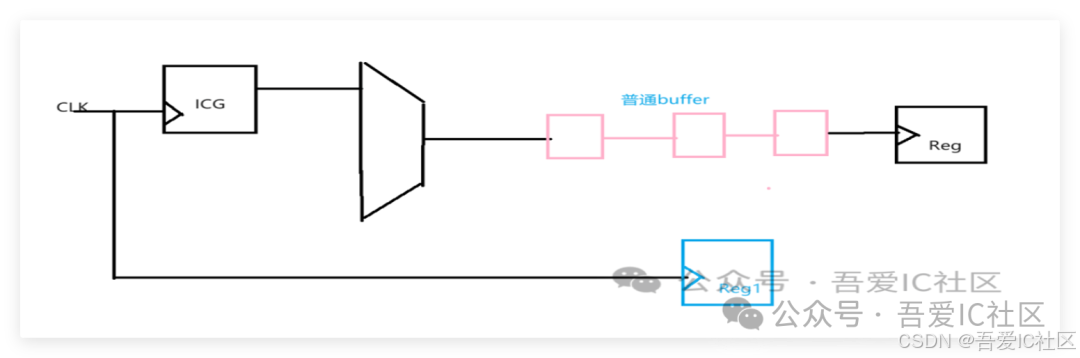

Q5: 下图所示的电路,什么场景下会出现遗漏clock tree的情况?为何说也会存在较大的hold violation和clock transition violation?

数字IC后端实现教程| Clock Gating相关clock tree案例解析

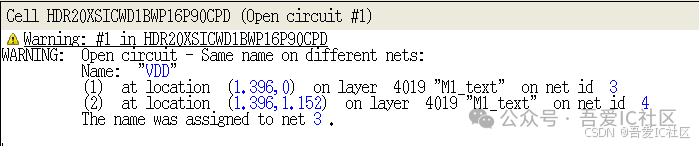

Q6: 星主,使用Hcell模式跑Calibre LVS,出现如下所示的GDS抽取警告——提示VDD Open!这个我定位看了一下,思考了一下,这是不是因为M3的via pillar没有把上下两个VDD连起来,导致calibre lvs认为两个net加上了同一个text导致open?

提示这里的M1 Text是power switch cell内部pg pin身上的。当前设计的Global VDD没有连成一个整体!