FPGA系统架构设计实践5_IP的封装优化

控制集(control set)

a)概念

1)控制集是一个与触发器FF时序逻辑紧密相关的概念,主要用于描述影响触发器行为的控制信号组合。它是FPGA逻辑实现、资源利用、时序优化的关键考量因素,并非物理上的硬件模块,而是从逻辑和布线角度对触发器控制信号的抽象归类。控制集定义为一组共同作用于触发器的控制信号(clock、reset、set、enable等)的唯一组合。具体来说,每个触发器的行为由两类信号决定:数据信号+控制信号。当两个触发器的所有控制信号(时钟源、复位类型、使能信号等)完全一致时,它们属于同一个控制集,只要有一个控制信号不同(哪怕时钟源相同但复位类型不同,或使能信号不同),就属于不同的控制集。

2)与底层硬件关联:7系列FPGA每个slice包含8个FF,这些FF共享部分控制信号的布线资源。同一控制集的触发器可以共享控制信号的布线资源,而不同控制集的触发器需要独立的布线资源。这直接决定了控制集对资源利用和时序的影响。在Xilinx FPGA的slice中,触发器的控制信号接口是有限的,即一个slice的8个触发器可能只能接入2个不同的时钟源或3个不同的复位信号。若多个触发器属于同一控制集,它们可以被打包到同一slice中,共享控制信号布线,充分利用slice资源;若触发器分属不同的控制集,每个控制集可能需要占用独立的slice控制端口,导致slice中未使用的触发器资源被浪费。

3)此外,控制信号的布线延迟是时序预算的重要组成部分。同一控制集的触发器共享控制信号布线,延迟一致性好,工具可更精确地优化时序。不同控制集的触发器需要独立布线,可能导致:控制信号布线长度增加(尤其是全局时钟网络被占用后,不得不使用区域布线,延迟更大);控制信号到达不同触发器的skew增大,恶化建立时间和保持时间;工具在布局布线时需要为每个控制集单独优化,增加了时序收敛的难度。

b)量化指标

1)可以通过资源利用率、时序性能、控制集分布特征等维度的量化指标间接评估。这些指标的核心逻辑是:合理的控制集应在满足功能需求的前提下,使资源利用率最大化、时序性能最优,且控制集数量与设计规模匹配。

2)直接量化指标:控制集自身的分布特征。

①控制集总数量:对于小规模设计(<1K触发器),控制集数量应该<50。中大规模设计(1~100K触发器),控制集数量应该<触发器总数的5%。

②平均每个控制集包含的触发器数量:理想值通常应该>5。=1时表明每个触发器独占一个控制集,此时slice资源利用率很低。

③小控制集占比:仅包含≤2个触发器的控制集数量÷控制集总数量。合理范围应该<20%。

④slice的触发器利用率:若slice的总利用率高,但触发器利用率低,说明大量slice因控制集冲突被占用,但内部触发器未充分利用。触发器利用率应与slice总利用率匹配。

⑤时钟偏斜:合理控制集下,同一控制集的时钟skew应较小(通常小于1ns)。若某控制集的时钟skew显著大于其他集,可能因控制集过多导致布线资源紧张。类似的有复位/使能信号的最大延迟。

⑥可查看vivado在布局布线后报告的控制信号布线拥挤程度。

使用QoR建议和QoR评估帮助时序收敛

a)QoR建议报告命令(report_qor_suggestions)可使Vivado对设计进行分析,并提供自动化解决方案以提升结果质量。该命令可在综合后或实现流程的任意阶段,对已打开的设计运行。RQS命令会评估设计并提出修复或改进建议,其建议形式分为以下两类:

1) RQS对象:此类对象可向指定命令添加开关,或向指定设计对象添加属性,还允许借助机器学习算法,添加为设计定制的实现策略。

2)需用户干预的文本建议:此类建议需用户手动操作才能生效(如修改RTL代码、调整约束等)。

b)借助相同的分析技术,QoR评估报告命令(report_qor_assessment)可评估设计满足时序要求的可能性,并提供设计指标的快速汇总。

c)report_qor_assessment(简称RQA)命令可在实现流程的任意阶段执行,包括synth_design、opt_design、place_design、phys_opt_design、route_design之后。RQA会生成一个评估分数,用于指示设计满足时序要求的可能性,同时提供快速初步分析,列出需进一步排查的问题项。此操作将打开评估报告,该报告包含三个核心章节:评估汇总、需排查的难点时序路径、含DONT_TOUCH属性的对象。

1)

本章节展示了评估分数(如2 - 实现流程可能完成,但时序无法满足),并推荐运行report_qor_suggestions (RQS) 来获取优化QoR的具体建议。通过RQA命令可以检测是否存在可优化的RQS建议,并提供相应的问题排查指南。

2)

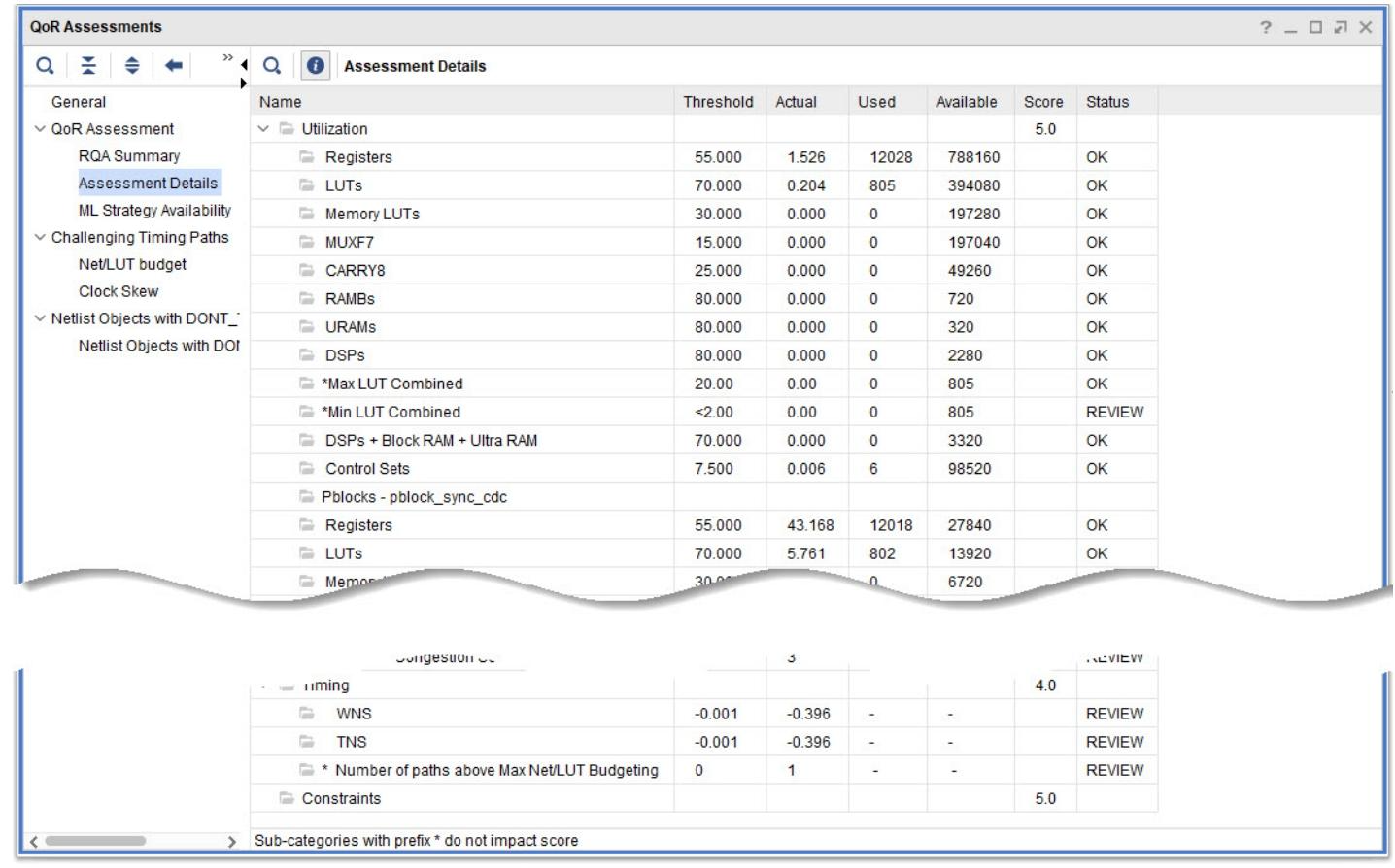

该章节列出导致当前评估分数的具体项(因勾选了报告达标指标,会显示标注为OK的达标项;默认仅显示需REVIEW的问题项)。以本实验为例,可看到WNS(最差负建立裕量)和TNS(总负建立裕量)指标标注为REVIEW(如 WNS=-0.396、TNS=-0.396),同时存在路径超过Net/LUT预算的问题。注:时序路径的指标通常反映最佳场景下的理论值,并非所有路径都能达到该值;而Net/LUT预算检查会用更贴近实际的Net延迟和LUT延迟值替代理论值,对因网表结构或资源稀疏导致的高难度路径进行惩罚标记,需优先排查这些路径。

3)

在难点时序路径选项中选择Net/LUT预算(Net/LUT budget)后,重点需关注以下两个参数:

i)Net检查裕量(Net Check Slack):替换为更高网线延迟值后的路径时序裕量;

ii)LUT检查裕量(LUT Check Slack):替换为更高LUT延迟值后的路径时序裕量。

通过双击路径可快速调出时序路径报告(Timing Path report),或使用F4快捷键查看路径原理图。这些操作均支持Vivado的cross-probing功能,方便用户深入分析路径延迟原因。

4)

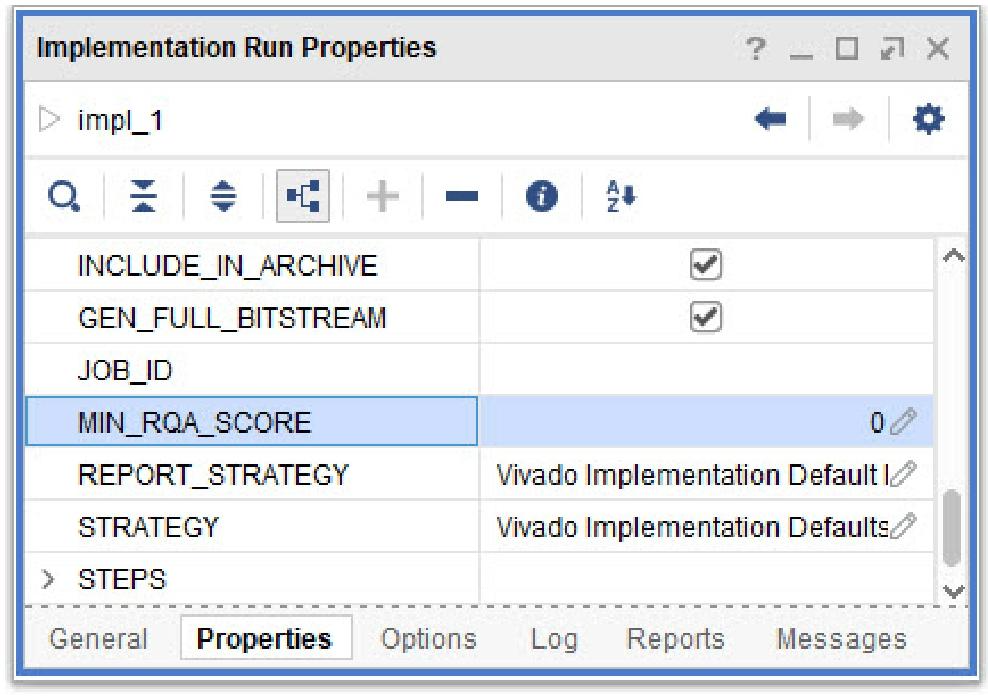

在Design Runs窗口中,选择实现运行,展开属性窗口找到MIN_RQA_SCORE属性,设置后,若RQA评估分数低于该阈值,实现流程将终止(RQA最低分为 1,故需设为2及以上才生效)。

5)要自动生成 QoR 评估报告,请按以下步骤操作:打开实现运行属性窗口、切换到Reports签页、在Report Strategy下拉菜单中,选择Timing Closure Reports Strategy、其他可选配置方式:创建自定义报告策略,在Tcl hook中添加report_qor_assessment命令(注意:该命令需在运行目录下执行才有效)。

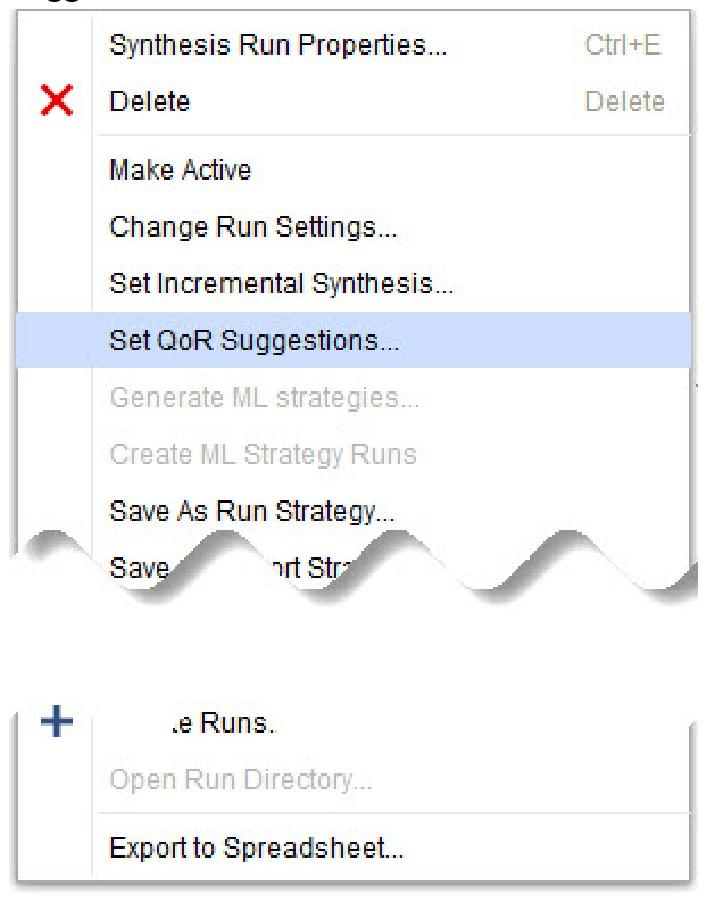

d)report_qor_suggestions(简称RQS)命令可在综合后的任意实现流程阶段(项目模式下通常为综合或实现后;非项目模式下可在synth_design、link_design、opt_design、place_design、phys_opt_design或route_design后),对已打开的设计运行。

1)GENERATED_AT(显示建议生成时的设计阶段,典型值为place_design或route_design)、APPLICABLE_FOR(需重新运行该阶段,建议才能生效)、AUTOMATIC(指示建议是否可自动执行,自动建议包括推荐工具开关(如opt_design -directive Explore)或给单元 / 网线添加属性)、INCREMENTAL FRIENDLY(指示建议是否适配增量流程)、SCOPE(指示目标综合运行层级,GLOBALSCOPE为顶层,否则为子模块)。

2)

在GENERATED视图中,点击RQS_NETLIST_10_1行。从APPLICABLE_FOR列可见,该建议为自动可执行(AUTOMATIC=Yes) 且适用于synth_design,这意味着需重新运行synth_design命令才能应用该建议。

3)

选中该行后,QoR建议属性(QoR Suggestion Properties) 窗口将显示该建议的属性。查看COMMAND属性可确认:该建议将为synth_design生成前向重定时属性(set property RETIMING_FORWARD 2),用于平衡时序路径。

4)

可通过勾选 / 取消勾选建议旁的复选框,筛选需写入文件的建议。例如,取消勾选RQS_XDC_1_1以排除该建议。

可通过勾选 / 取消勾选建议旁的复选框,筛选需写入文件的建议。例如,取消勾选RQS_XDC_1_1以排除该建议。

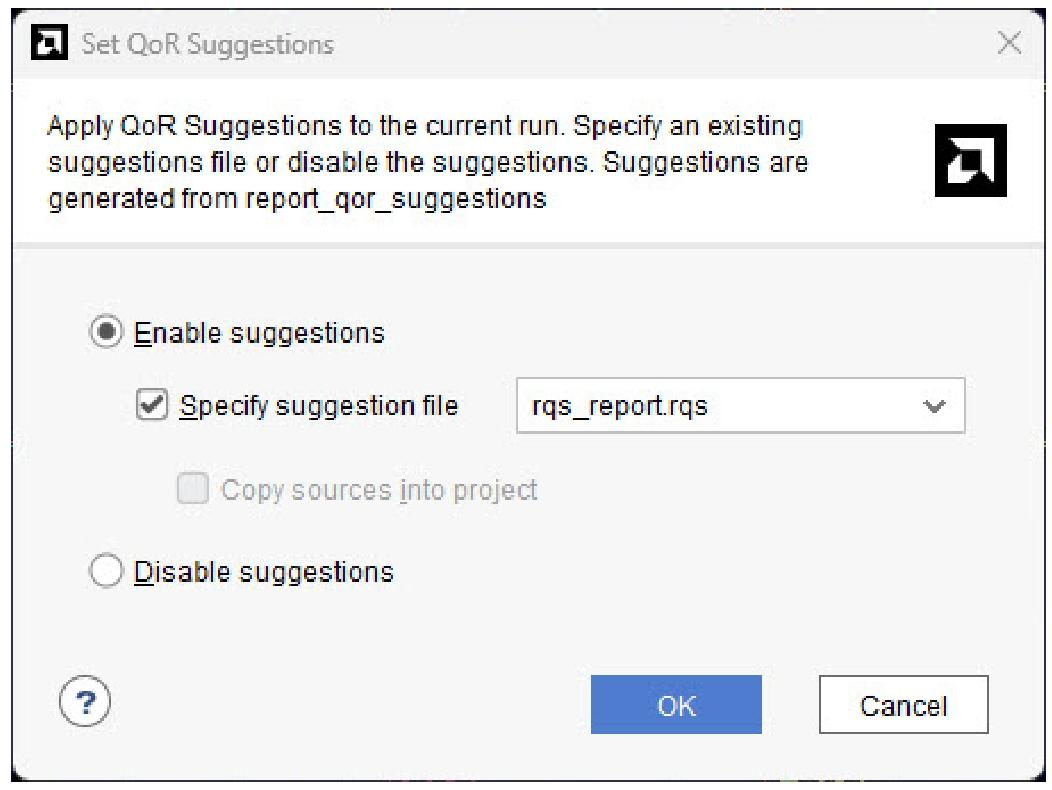

e)Run with Suggestions

1)

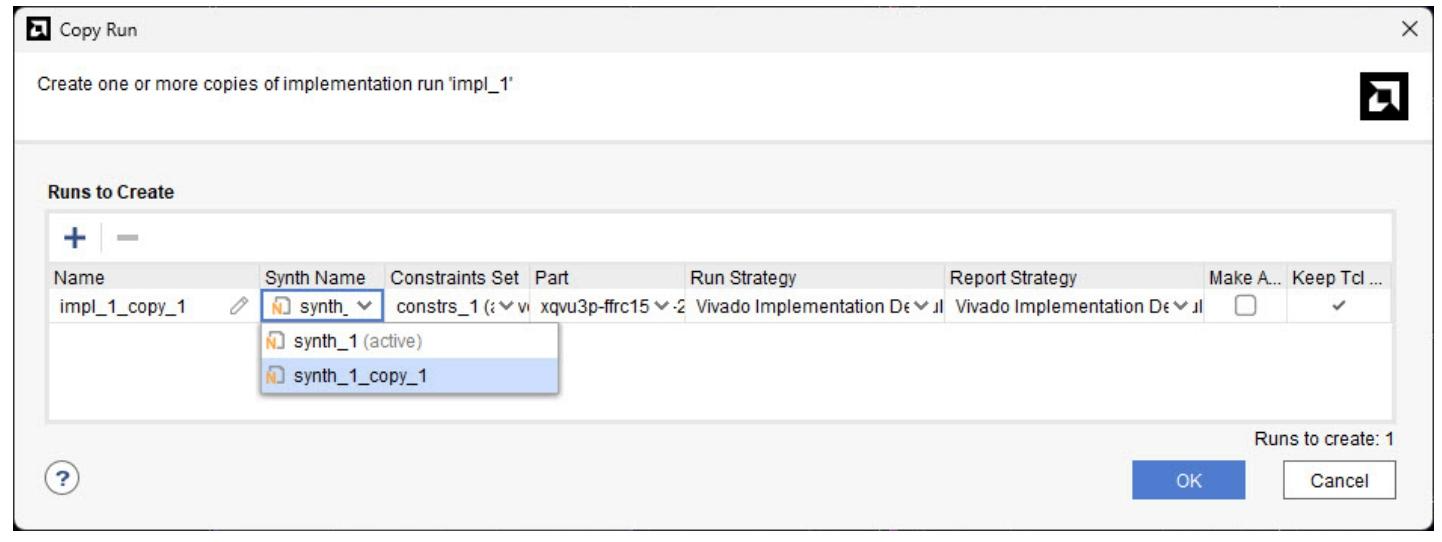

运行打开后,RQA Summary。可见QoR评估分数从2(时序无法满足)提升至 3(设计有小概率成功),证明RQS建议已初步生效。在 QoR评估报告中,选择评估详情,可见原标注为REVIEW的Net/LUT 预算超标问题已消失,仅剩余DONT_TOUCH 对象等非时序类问题。

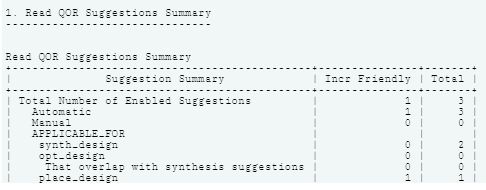

2)当place_design完成后,打开新实现运行的实现日志文件(implementation log),查看文件顶部的QoR建议读取汇总表格。

3)打开布局后检查点并重新生成RQS报告,新报告的建议报告(Suggestion Report)下新增以下章节:GENERATED(当前阶段生成的新建议)、APPLIED(已成功应用的建议,如上一步综合/布局中执行的自动建议)、EXISTING(之前生成但未应用的建议)、FAILED TO APPLY(因设计对象已不存在而应用失败的建议)。

f)建议积累

1)RQS会在设计流程的不同阶段生成不同建议,核心原因是设计状态随流程推进不断更新,RQS可利用更精准的信息生成优化方案。各阶段信息精度变化如下:时钟估计(布局后的时钟延迟、skew等参数估计更准确)、拥塞信息(布局后开始获取拥塞数据,布线后拥塞分析精度进一步提升)、时序估计(时序裕量的计算精度随流程推进逐步提高,且受分析路径数量影响)。

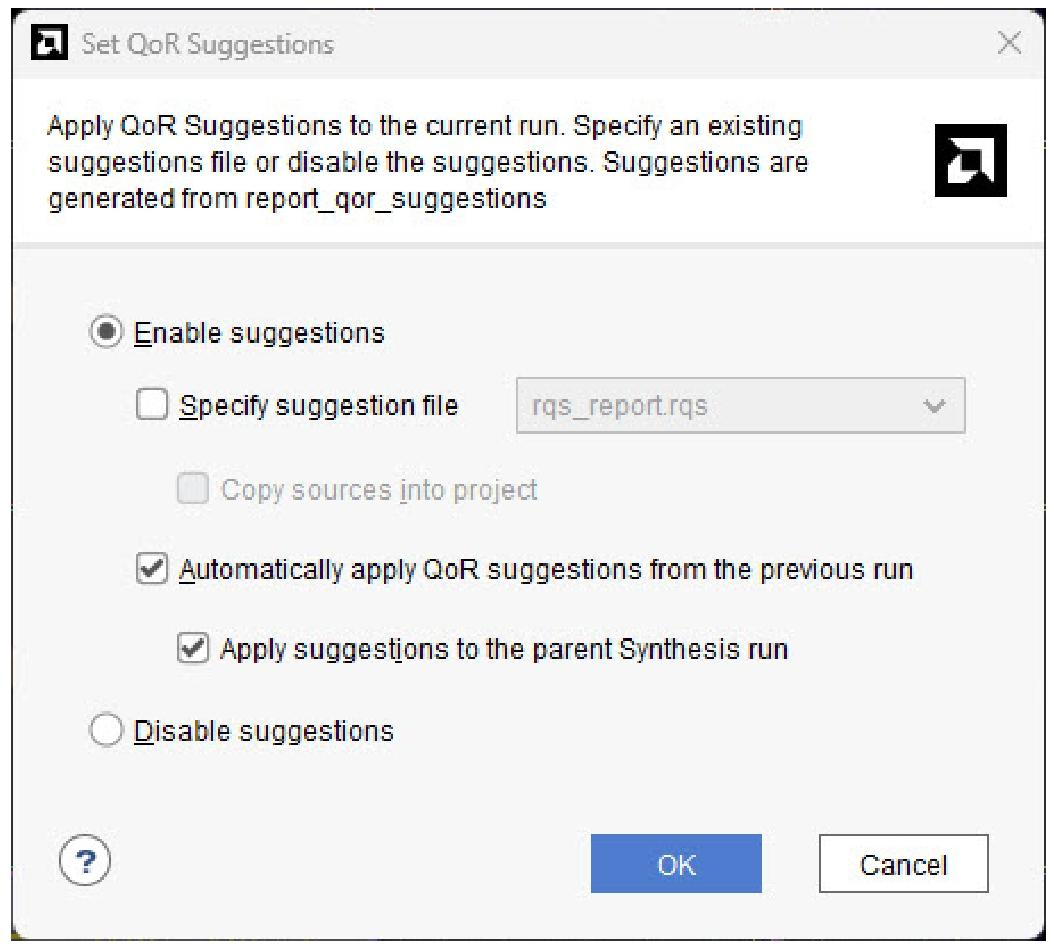

g)自动运行QoR建议

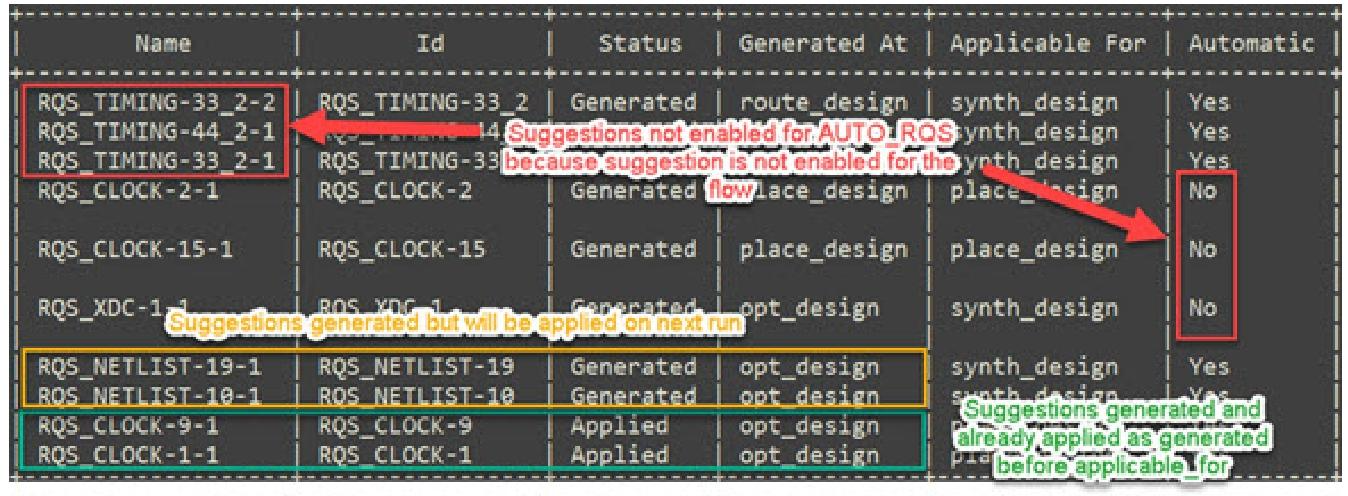

1)AUTO_RQS流程会在opt_design、place_design以及实现运行结束时(route_design或post_route_phys_opt_design)自动生成QoR建议,并完成生成→应用→积累的全流程,无需用户手动干预。

2)在 AUTO_RQS 流程中,优化后的建议列表分三个阶段生成,所有建议始终以最大化QoR提升为目标。各阶段建议的生成时机和功能如下:阶段1在opt_design后,基于优化后的设计生成建议,如果建议的生效阶段(APPLICABLE_FOR)属于后续流程(如place_design),则自动在当前运行中启用并在后续阶段应用;阶段2在place_design后,利用布局后的精准信息(如时钟偏差、初步拥塞情况)生成新建议;阶段3在最终步骤后(route_design或post_route_phys_opt_design),结合布线后的完整信息(如实际路径延迟、拥塞分布)生成最终建议,将此阶段建议与阶段2的布局建议、阶段1的优化建议进行合并,最终将所有建议写入RQS文件。当运行被重置(Reset Runs)时,合并后的RQS文件会自动写入utils_1源文件集;在下一次运行中,所有建议将被自动应用。

3)

4)

运行完成后,在实现运行属性窗口中,切换到报告标签,在报告列表中选择QoR Suggestions(QoR 建议报告),该报告由AUTO_RQS流程自动生成,包含以下关键信息:报告生成时机(分别在opt_design、place_design、route_design后生成)、建议状态(标注每条建议的 GENERATED_AT、APPLICABLE_FOR、APPLIED/FAILED TO APPLY)。

使用dataflow

a)DFV能够帮助深入理解设计中影响布局布线质量的关键部分,实现方式如下:在经过数据流优化的简化网表中,识别宽总线、高带宽总线;识别与这些总线相关的单元 ,此类单元的布局对设计的布局质量有显著影响;生成与目标宽总线相关的多单元路径,为布局分析提供更全面的视角;生成布局规划(floorplan),将总线上的关联单元整合放置,优化布线效率。

b) (未完待续)