FPGA教程系列-Vivado IP核BMG核

FPGA教程系列-Vivado IP核BMG核

Xilinx® LogiCORE™ IP Block Memory Generator(BMG)核是一款高级存储器构建工具,它利用 Xilinx FPGA 内部的嵌入式块 RAM 资源,生成在面积和性能上都经过优化的存储器。BMG 核支持 Native 接口和 AXI4 接口两种配置方式。其中,AXI4 接口配置是在 Native 接口基础上扩展而来,为核增加了业界标准的总线协议接口。

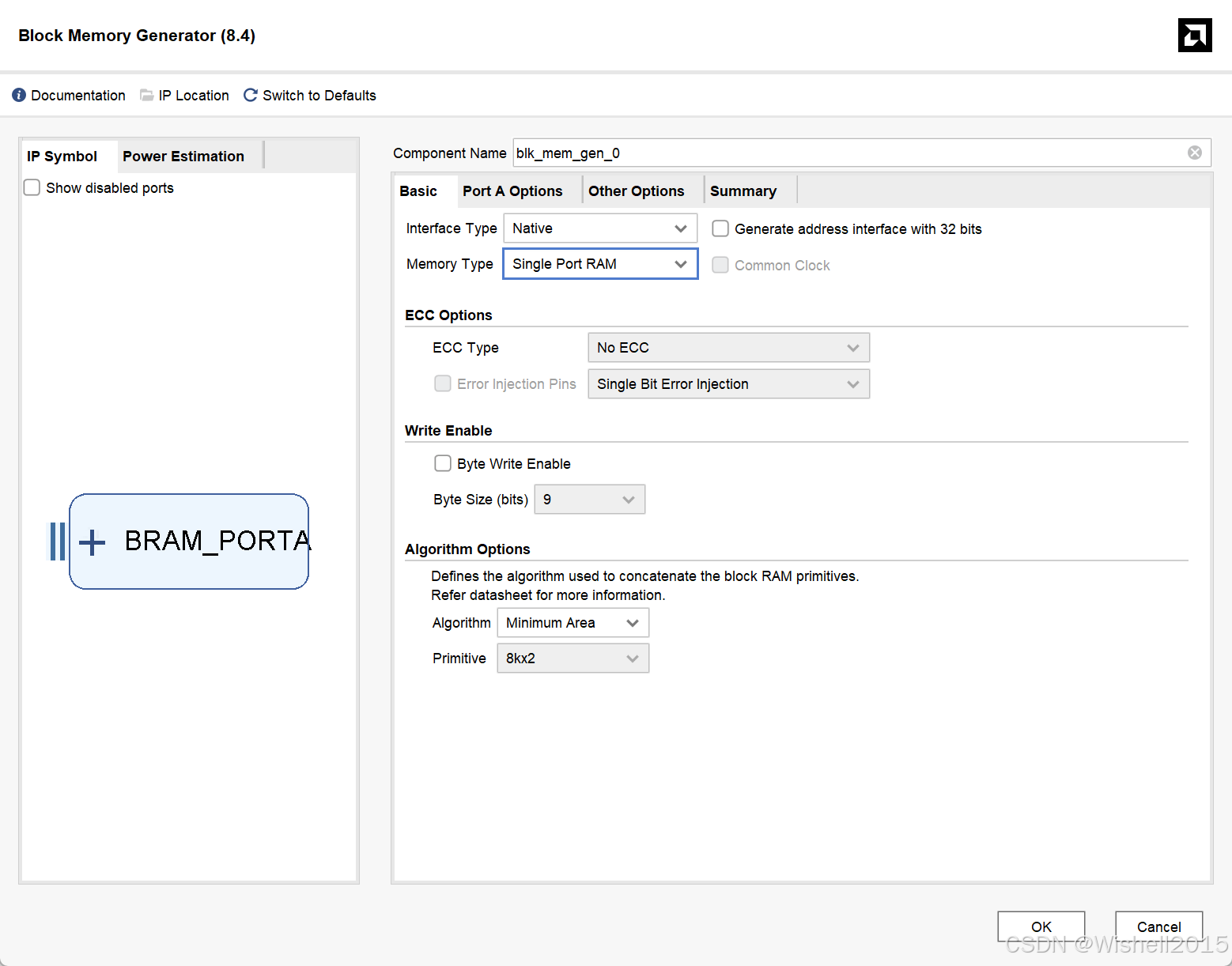

- lnterface Type (接口模式) :有两种接口模式可选,分别为Native(常规)接口和AXI4 接口。AXI4 模式一般是在处理器中的数据需要和BRAM 交互(如ZYNQ 中的PS 和PL 交互)时才会使用,当不需要与处理器数据进行交互时,一般采用Native 模式。

- Generate address interface with 32 bits 选项: 是否生成位宽为32 的地址接口,勾选后内存的数据位宽必须设置成32 的整数倍,在实际应用中,一般不做勾选。

- Memory Type (存储类型) :有五种类型可选,分别为 Single Port RAM 单端口RAM 、Simple Dual Port RAM伪双端口RAM 、 True Dual Port RAM 真双端口RAM 、 Single Port ROM单端口ROM 和 Dual Port ROM(双端口ROM)。

- Common Clock 选项: 是否启用同步时钟,在单端口模式下不需要考虑这个问题,所以该选项也无法进行设置。

- ECC(全称Error Correcting Code ,即纠错码) Options :纠错码选项只有在伪双端口RAM类型下才可以进行配置。

- Write Enable (写使能) :可以选择是否使用字节写使能功能,启用后可设置字节大小为8位(无奇偶校验)或9 位(包括奇偶校验),需要注意的是启用后内存的数据位宽必须设置为所选字节大小的整数倍。

- Algorithm Options (算法选项) :算法选项主要用于决定BRAM 的拼接的方式,一般在BRAM深度、宽度较大的时候起作用,有三种算法可选,分别为 Minimum Area 最小面积算法 、 Low Power 低功耗算法 和 Fixed Primitives 固定单元算法 。

-

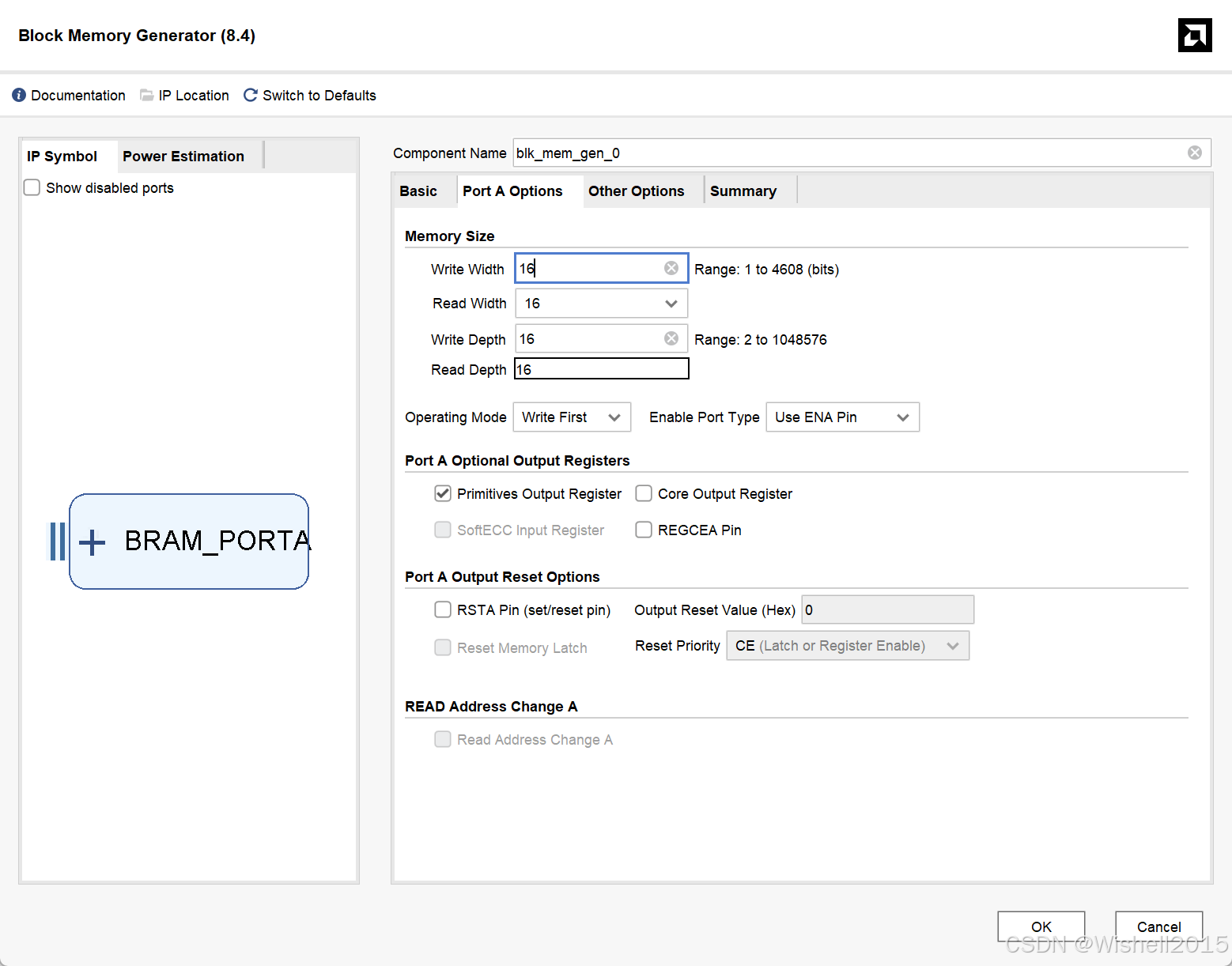

Memory Size Size(内存大小),用于指定端口读 写宽度和深度、运行模式和使能端口类型,具体描述如下:

Write Width:写数据位宽,单位bitRead Width:读数据位宽,其位宽设置必须与写数据位宽存在倍数关系通常情况下读 写数据位宽保持一致 。

Write DepthDepth:写深度,设置成32代表RAM 所能访问的地址范围为0-31 。

Read Depth:读深度,当写数据位宽、读数据位宽和写深度的值确定后,读深度的值就会自动确定。

Operating Mode:运作模式。该选项决定了我们在进行写操作期间,DOUT(读数据线)上的数据变化,有三种模式可选,分别为:

• Write First(写优先模式):对某个地址进行写操作时,会将写入的数据传递到读数据线上。

• Read First(读优先模式):对某个地址进行写操作时,会将上次写入该地址的数据递到读数据线上。

• No Change(不变模式):在该模式下,进行写操作时,读数据线上的数据保持不变。Enable Port Type:使能端口类型。有两种可选,分别为Use ENA pin(添加使能端口A 信号)和Always Enabled(取消使能信号,端口A 一直处于使能状态)。

-

Port A Optional Output Register 用于为RAM 的输出端添加寄存器。其作用是提高BRAM的运行频率和改善时序,当然为此付出的代价就是每勾选一个寄存器,输出就会延迟一拍。其中:

• Primitives Output Register,使用BRAM 内部的寄存器打拍输出。

• Core Output Register,使用SLICE 的寄存器打拍输出。

• SoftECC Input Register,当使用软ECC 的时候,用SLICE 的寄存器打拍。

• REGCEA,当使用Primitives Output Register 或者Core Output Register 时,可以用REGCEA 来使能相应的输出。 -

Port A Output Reset Options 用于设置端口的复位信号,可以添加一个复位信号(RSTA Pin)、设置复位时ram 输出总线上的数据值(Output Reset Value )、设置是否复位内置锁存器(Reset Memory Latch)和设置复位信号与时钟使能之间的优先级(Reset Priority)。

-

READ Address Change A 用于更改端口的读地址,这个功能只在UltraScale 设备上使用,一般在某些低功耗场景中会应用到。

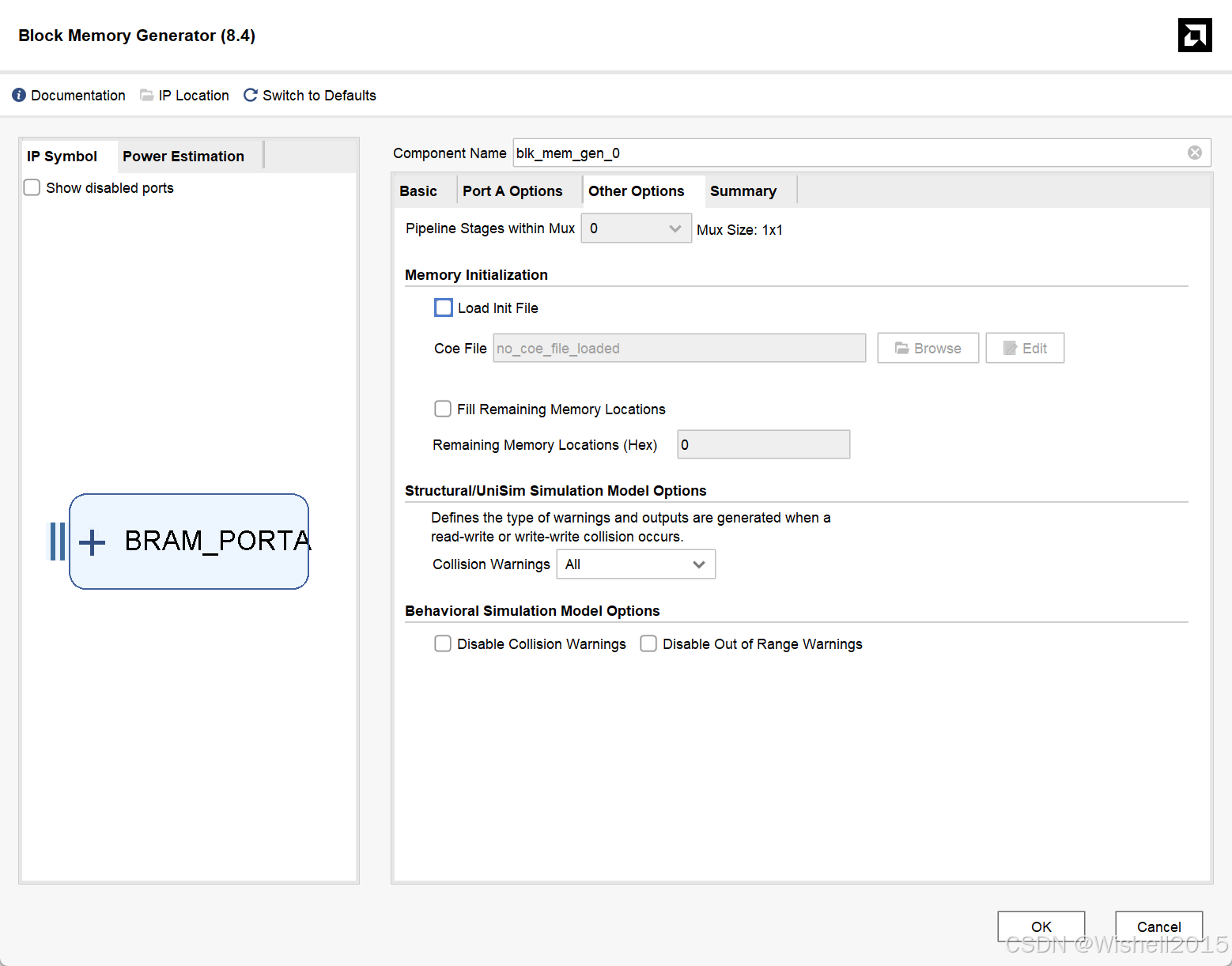

- Pipeline Stages within Mux 输出端Mux 选择器的流水线级数。在大位宽、大深度的BRAM拼接场景中,用MUX 来选择输出地址所对应的数据,勾选该选项后可以使输出数据具有更好的时序。

- Memory Initialization Initialization(初始化文件),选择是否使用本地初始化文件(.coe 文件)来对存储空间进行初始化。(用于生成ROM)

- Structural/UniSim Simulation Model Options ,用于选择结构仿真模型发生碰撞时生成的警告消息和输出的类型。

- Behavioral Simulation Model Options ,用于关闭仿真时的冲突告警和超出范围告警。

以上是对BMG核的一个简单介绍,在实际的使用过程中还是要根据需求进行设置。