【1.11】基于FPGA的costas环开发5——环路滤波器模块开发

目录

1.理论回顾

2.基于FPGA的环路滤波器模块实现

2.1 环路滤波器理论分析

2.2 环路滤波器的FPGA实现

3 环路滤波器的FPGA仿真测试

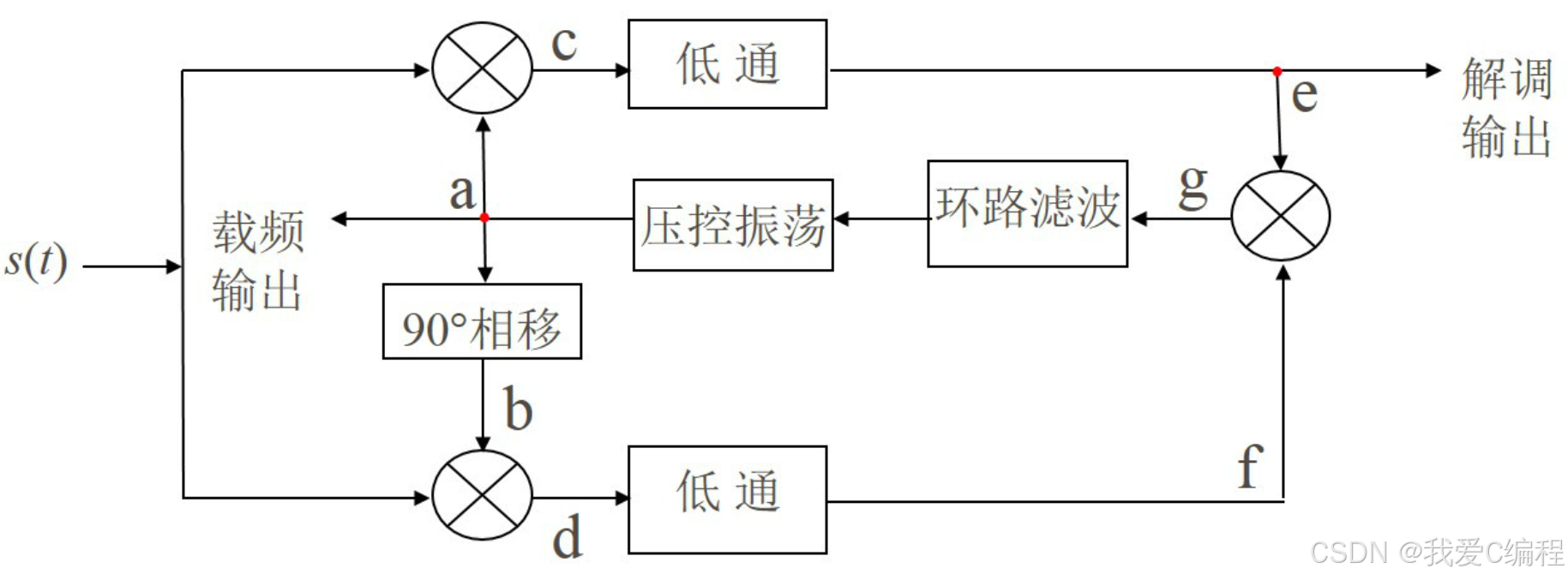

本文介绍了锁相环(PLL)中环路滤波器的FPGA实现方法。首先从理论角度分析了PI型环路滤波器的连续域模型及其离散化处理,详细说明了鉴相器输出信号的处理流程。然后给出了基于Verilog的FPGA实现代码,包括比例项和积分项的计算电路设计。最后通过测试平台验证了模块功能,展示了开环状态下滤波器输出信号的特性变化。该实现采用32位定点数处理,包含乘法运算和数据截取等关键操作。

1.理论回顾

根据本章节第二小节的学习成果可知:

https://blog.csdn.net/hlayumi1234567/article/details/154012294

其在接收端的处理过程如下: