Xilinx Aurora 8B/10B IP核(1):时钟架构线速率Lane配置--使用与选择详解

引言

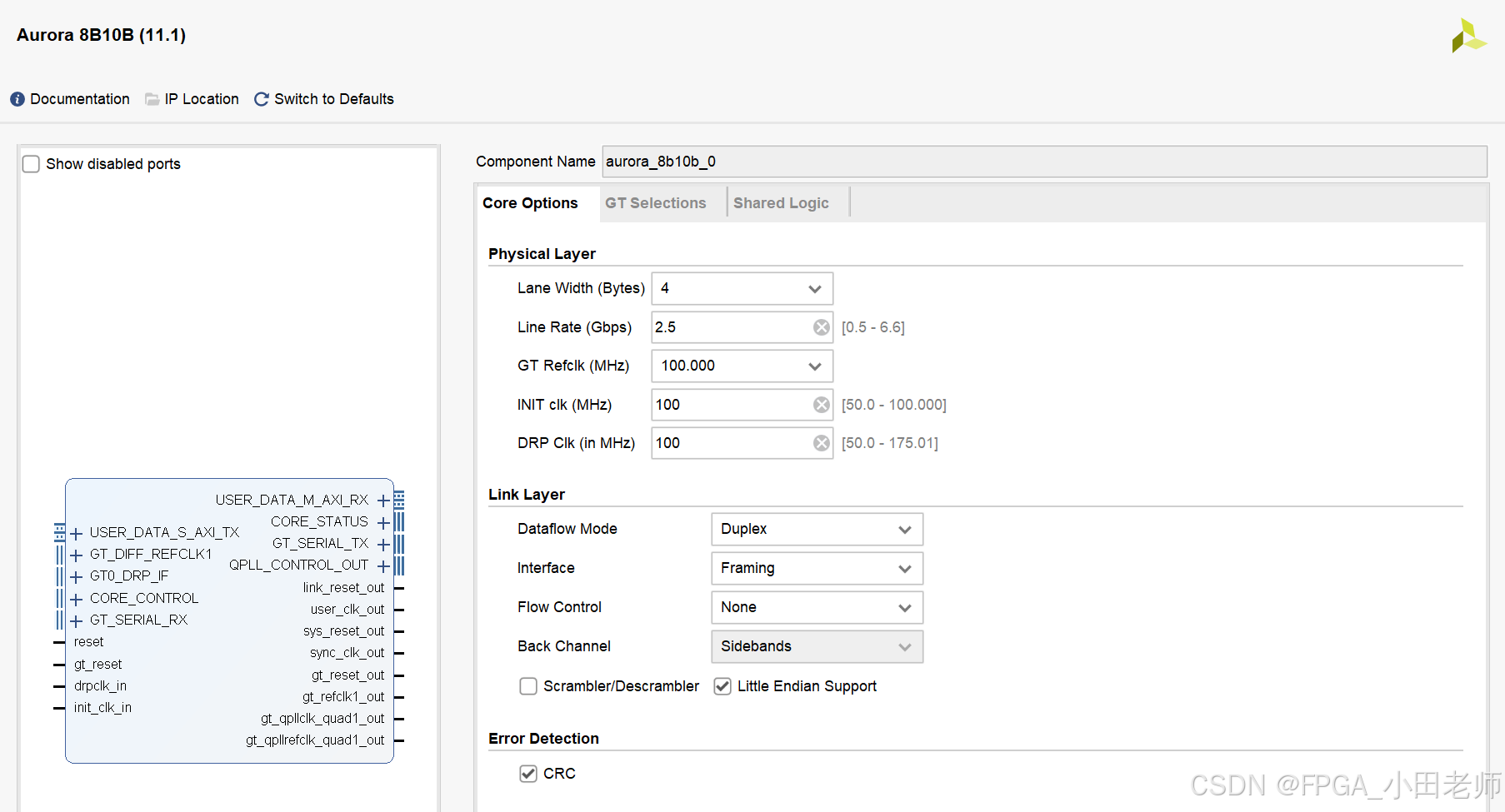

在高速FPGA系统设计中,Xilinx Aurora 8B/10B IP核作为一种轻量级、可扩展的链路层协议,已成为点对点高速数据传输的首选方案。然而,如何正确配置线速率和Lane数量,平衡性能、功耗和复杂度,是每个工程师面临的关键挑战。本文将从理论基础到工程实践,全面解析Aurora IP核的配置艺术。

1. Aurora IP核时钟架构深度解析

理解时钟架构是正确配置Aurora的基础,四种时钟各司其职,共同确保链路稳定运行。

1.1 GT参考时钟 - 物理层的心脏

功能:驱动GT收发器锁相环,产生高速串行时钟

来源:外部晶振/时钟芯片,通过专用时钟管脚输入

质量要求:低抖动(<1ps RMS)、高稳定性

决定性关系:线速率 = GT_Ref_Clk × 整数倍频系数

工程实践要点:

- 必须连接到GT Bank的专用时钟管脚

- 时钟质量直接决定链路稳定性

- 建议使用专用时钟芯片(如SI5345)而非普通晶振

// 举例

GT_Ref_Clk频率 = 100 MHz

目标线速率 = 2.5 Gbps

倍频系数 = 2.5 Gbps / 100 MHz = 25 // 25是个整数1.2 INIT时钟 - 初始化控制时钟

功能:控制GT收发器初始化和复位序列

来源:通常与参考时钟同源或FPGA逻辑时钟

频率范围:50-150 MHz

关键特性:只在初始化和重配置时使用,正常数据传输时不活跃

配置建议:

- 可与参考时钟(GT_Ref_Clk)使用相同源,简化设计

- 确保在IP核配置中正确设置频率

1.3 DRP时钟 - 动态重配置时钟

功能:动态重配置接口时钟,用于实时调整GT参数

来源:FPGA逻辑时钟

频率:与用户逻辑兼容(通常50-250 MHz)

应用场景:

- 实时优化均衡器设置

- 监控链路性能指标

- 动态调整发送预加重和接收均衡

工程提示:

在初始调试阶段特别有用,可通过DRP接口微调参数优化眼图

1.4 User时钟 - 用户接口时钟

功能:Aurora IP核与用户逻辑交互的时钟域

来源:由GT收发器恢复时钟或参考时钟派生

核心计算公式:

User_Clk频率 = 有效数据速率 / 总数据位宽

有效数据速率 = 线速率 × (8/10)

8/10 --> 8B/10B编码开销

线速率 = 2.5 Gbps// 单Lane配置计算:

有效数据速率 = 2.5 Gbps × 0.8 = 2.0 Gbps

单Lane数据位宽 = 32位(4字节)

User_Clk频率 = 2.0 Gbps / 32 bit = 62.5 MHz// 4-Lane配置计算:

总有效数据速率 = 2.0 Gbps × 4 = 8.0 Gbps

总数据位宽 = 32位 × 4 = 128位

User_Clk频率 = 8.0 Gbps / 128 bit = 62.5 MHz2. 典型线速率值及其工程背景

线速率的选择不是随意的,而是基于行业标准、时钟规整性和硬件能力的综合考量。

2.1 基于规整时钟的速率

| 参考时钟 | 倍频系数 | 线速率 | 有效速率 | User Clk(32位) | 适用场景 |

|---|---|---|---|---|---|

| 125 MHz | ×16 | 2.0 Gbps | 1.6 Gbps | 50 MHz | 低成本应用 |

| 125 MHz | ×20 | 2.5 Gbps | 2.0 Gbps | 62.5 MHz | 平衡型设计 |

| 125 MHz | ×25 | 3.125 Gbps | 2.5 Gbps | 78.125 MHz | 10G以太网相关 |

| 125 MHz | ×32 | 4.0 Gbps | 3.2 Gbps | 100 MHz | 高性能应用 |

| 156.25 MHz | ×16 | 2.5 Gbps | 2.0 Gbps | 62.5 MHz | 替代125MHz方案 |

| 156.25 MHz | ×40 | 6.25 Gbps | 5.0 Gbps | 156.25 MHz | 10G以太网XAUI |

2.2 行业标准协议速率

// 网络通信协议

1.25 Gbps // 千兆以太网 (1GbE)

2.5 Gbps // 2.5GbE

3.125 Gbps // 10GbE基础速率 (4×3.125G=10G)

10.3125 Gbps // 10GbE (64B/66B)// 存储协议

3.0 Gbps // SATA 2.0

6.0 Gbps // SATA 3.0// 系统接口

2.5 Gbps // PCIe Gen1

5.0 Gbps // PCIe Gen2

8.0 Gbps // PCIe Gen32.3 线速率选择的黄金法则

// 不是越快越好!需要考虑:if (首次设计 || PCB设计经验不足) {推荐速率 = 2.5 Gbps; // 稳健起步

}

else if (带宽需求明确 && PCB设计优秀) {推荐速率 = 基于计算的需求速率;

}

else {推荐速率 = 参考行业标准速率;

}// 风险评估清单:

- [ ] PCB材料是否支持目标速率?

- [ ] 电源设计是否有足够余量?

- [ ] 是否有SI仿真结果支持?

- [ ] 团队是否有高速调试经验?3. 带宽需求分析与线速率计算

基于实际应用需求科学计算所需线速率,避免过度设计或性能不足。

3.1 我们的应用场景分析

给定参数:

单次突发数据量 = 2 KB × 12 = 24 KB = 196,608 bit

允许的传输时间窗口 = 100 μs (根据实际应用调整)

基础带宽计算:

所需数据速率 = 196,608 bit / 100 μs = 1.966 Gbps

考虑实际因素:

协议开销余量 = 20% (推荐保留20-30%余量)

目标有效数据速率 = 1.966 Gbps × 1.2 ≈ 2.36 Gbps

所需线速率 = 目标有效数据速率 / 0.8 ≈ 2.95 Gbps (8b/10b)

3.2 多Lane配置的性能跃升

单Lane与多Lane配置的对比分析:时间=数据量/带宽=24KB/2.0Gbps

| 性能指标 | 单Lane @2.5G | 2-Lane @2.5G | 4-Lane @2.5G | 单Lane @3.125G |

|---|---|---|---|---|

| 总有效带宽 | 2.0 Gbps | 4.0 Gbps | 8.0 Gbps | 2.5 Gbps |

| 传输24KB时间 | 98.3 μs | 49.2 μs | 24.6 μs | 78.6 μs |

| User Clk频率 | 62.5 MHz | 62.5 MHz | 62.5 MHz | 78.125 MHz |

| PCB复杂度 | 低 | 中 | 高 | 低 |

| 功耗估算 | 基准 | ~2×基准 | ~4×基准 | ~1.3×基准 |

3.3 配置决策矩阵

// 基于24KB突发传输的配置推荐// 方案1: 单Lane @3.125Gbps (推荐度: ★★★★★)

有效带宽: 2.5 Gbps | 传输时间: 78.6 μs | 复杂度: 低// 方案2: 2-Lane @2.5Gbps (推荐度: ★★★★☆)

有效带宽: 4.0 Gbps | 传输时间: 49.2 μs | 复杂度: 中// 方案3: 4-Lane @2.5Gbps (推荐度: ★★★☆☆)

有效带宽: 8.0 Gbps | 传输时间: 24.6 μs | 复杂度: 高// 选择逻辑:

if (时间要求宽松 && 成本敏感) {选择方案1;

} else if (需要性能预留 && 有PCB经验) {选择方案2;

} else if (极致性能需求 && 丰富高速经验) {选择方案3;

}4. 实际性能与优化策略

Aurora帧结构开销:

每帧开销 = SCP(开始4字节) + ECP(结束4字节) = 8字节

对于24KB数据传输策略:

策略1: 单帧传输24KB

开销比例 = 8/24576 ≈ 0.032%

优点: 开销最小化

缺点: 需要大缓冲区,增加延迟

策略2: 分多帧传输,每帧1KB

帧数量 = 24帧

总开销 = 24 × 8 = 192字节

开销比例 = 192/24576 ≈ 0.78%

优点: 降低延迟,减少缓冲区需求

5. 完整配置实施方案

对于多Lane高速设计,推荐分阶段实施:

阶段1: 单Lane原型验证(2-3周)

目标: 验证基础功能和硬件稳定性 配置: 1-Lane @ 2.5 Gbps 重点: - 硬件基础功能验证- 参考时钟质量测试- 基础误码率测试

阶段2: 性能基线建立(1-2周)

目标: 建立性能基准和稳定性测试 配置: 1-Lane @ 3.125 Gbps 重点:- 不同速率下的稳定性对比- 功耗和温度监控- 信号完整性初步评估

阶段3: 多Lane扩展(2-3周)

目标: 实现多Lane配置和通道绑定 配置: 2-Lane @ 2.5 Gbps → 4-Lane @ 2.5 Gbps 重点:- 通道绑定机制验证- 多Lane同步性能测试- 系统级稳定性压力测试

6. 结论与最佳实践

6.1 配置选择总结

对于24KB突发数据传输需求,在XC7K325T + 100MHz参考时钟平台上的最终推荐:

首选方案:2-Lane @ 2.5 Gbps

有效带宽:4.0 Gbps

传输时间:49.2 μs(满足100μs要求且有100%余量)

复杂度适中,成功率高

为未来需求增长提供预留

备选方案:单Lane @ 3.125 Gbps

有效带宽:2.5 Gbps

传输时间:78.6 μs(刚好满足要求)

硬件设计最简单

适合成本敏感应用

6.2 核心设计原则

稳健性原则:在满足需求的前提下选择最稳定的配置

可扩展性原则:为未来带宽需求预留升级空间

经济性原则:避免过度设计,平衡性能与成本

可调试性原则:设计阶段就考虑调试和测试的便利性

通过本文的全面分析,您应该能够为特定的应用场景选择最优的Aurora 8B/10B IP核配置,在性能、功耗、成本和复杂度之间找到最佳平衡点。记住,最好的设计不是性能最高的设计,而是最适合项目需求的设计。