【FPGA+DSP系列】——PWM电平光耦转换电路实验分析----电路原理分析,器件选型

【FPGA+DSP系列】——PWM电平转换电路实验分析

- 前言

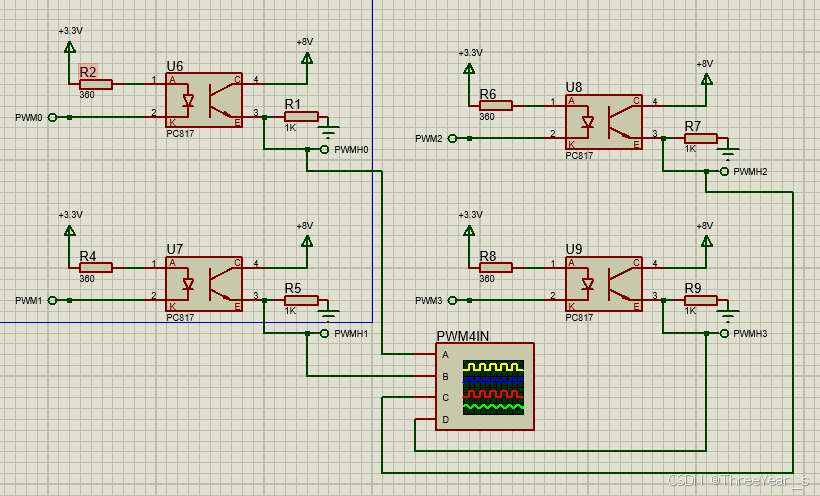

- 一、光耦电平转换电路原理分析

- 二、器件选型

- 三、proteus仿真电路搭建

- 四、CCS代码创建

- 五、波形分析

- 总结

前言

无论是DSP还是fpga或者是arm产生的pwm信号本身电平大多都是3.3V,然而这个电平太低,驱动不了晶闸管等一些大功率控制器件,所以说需要将PWM信号的电平转换为更高电平,进而满足驱动器件的驱动要求。

我这边主要将四路PWM信号由3.3V转换为8v的电平信号,进而完成对驱动信号的转变。

一、光耦电平转换电路原理分析

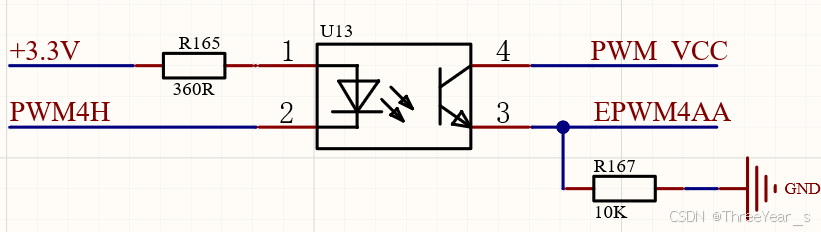

首先整体电路组成就是光耦/电阻,主要原理就是当左边二极管导通后,二极管发光触发右边电路导通,其中PWMVCC多大你转换后的电平信号就是多大。

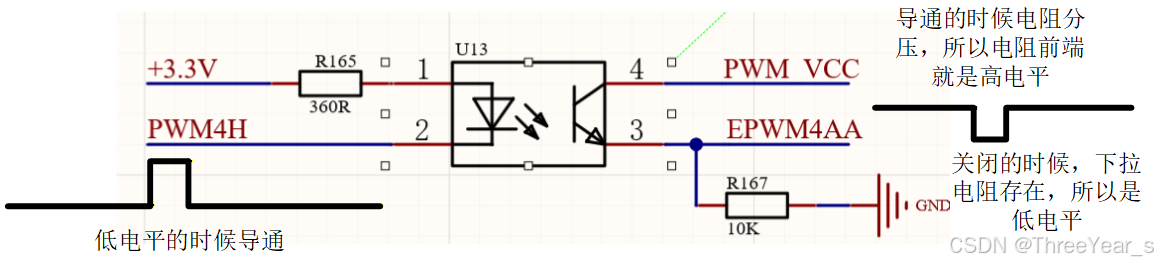

其次就是PWM信号与电平转换后的电平信号高低电平是相反的。什么意思呢看下图:

然后其实现在这个图里面部分参数是有问题的,下面先展示几个光耦电路注意的要点。,这时候就需要阅读光耦手册了。

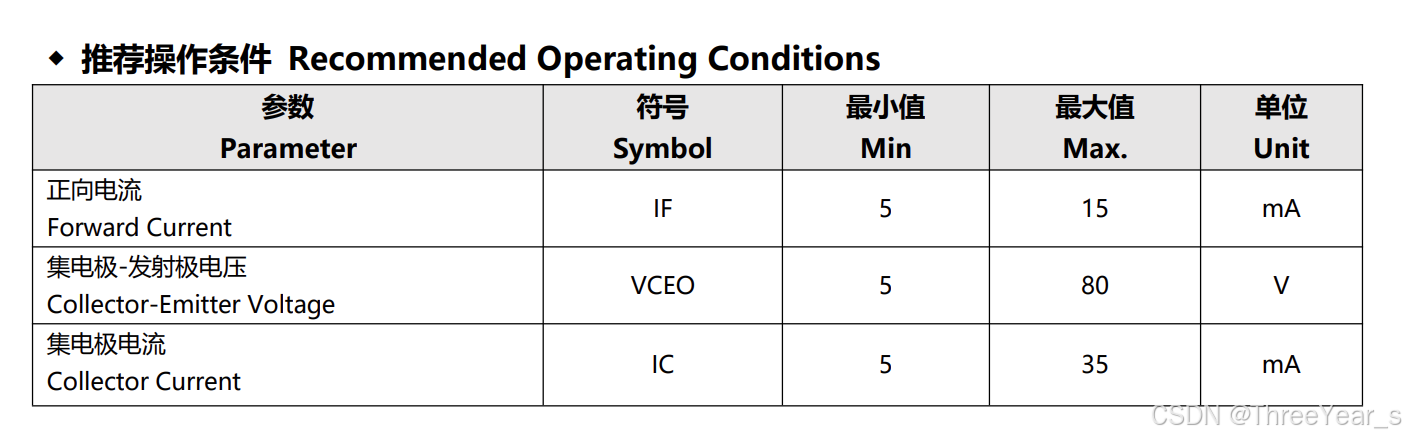

这是几个要点,其中正向电流就是左端二极管的电流,这个电流要在5ma到15ma之内,因为这边的电平是3.3V,所以结合我们常见电阻选型,选择360Ω,这个电流大概就是9.16ma左右,满足这个范围。

其次就是集电极以及发射机的电压,这个电压值在5V-80V之内,也就是说你3.3V的电平,只能转换为为这个电压范围内的电压信号。

最后就是集电极电流,这个电流就是右端的电流要去,整体要求在5ma到35ma之内,现在我们选择的电阻是10KΩ,电压选择的是8V,这两个算出来的电流值是0.8ma,明显不在这个范围之内。

你们可以试一下,仿真中用10k电阻来试一下,会发现驱动不了晶闸管,因为他主要看电流,也不是完全看电压。(我觉得是这样)

二、器件选型

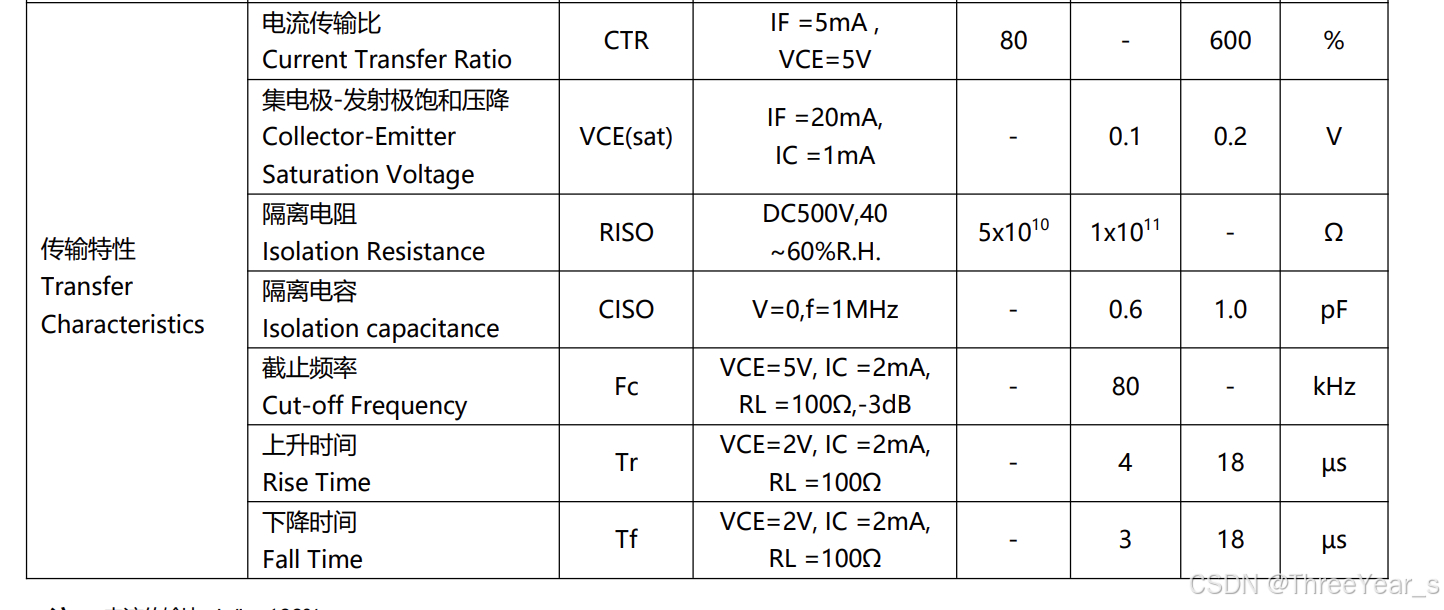

主要是开你的开关频率要求,光耦电平切换的上升时间以及下降时间都有写,频率比较高的时候推荐选择PWM芯片,但是成本会增高。

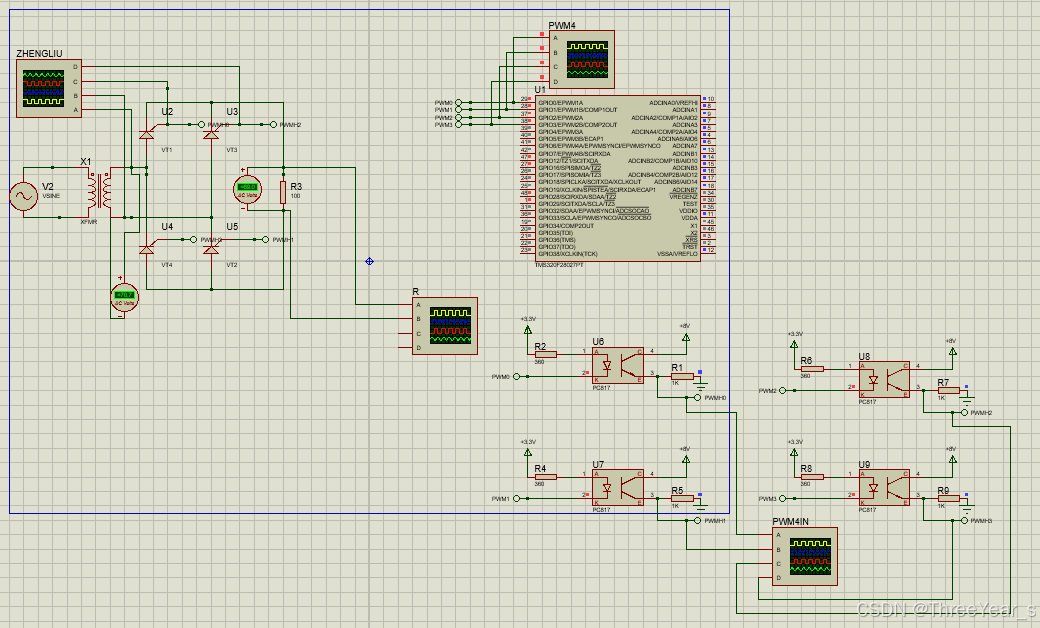

三、proteus仿真电路搭建

这个电路是在上一节中的基础上进行修改的,具体可以查看这个文章proteus仿真epwm电路

四、CCS代码创建

相对于上一节,只替换了epwm.c里面的内容,主要是将发送pwm波,改为空闲高电平,触发低电平,这样光耦另一端才能出来高电平的脉冲信号。

#include "epwm.h"void EPWM1_Init(Uint16 tbprd)

{EALLOW;SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the ePWMSysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; // ePWM1EDIS;InitEPwm1Gpio();EALLOW;SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Stop all the TB clocksEDIS;// Setup Sync - EPWM1作为主定时器EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // 在计数器为零时产生同步信号EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 主定时器不需要相位使能EPwm1Regs.TBPHS.half.TBPHS = 0; // 主定时器相位为0EPwm1Regs.TBCTR = 0x0000; // Clear counterEPwm1Regs.TBPRD = tbprd;EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count upEPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV4;EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV16;// Setup shadow register load on ZEROEPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;// Set Compare values - 10%占空比Uint16 duty_10percent = tbprd * 10 / 100; // 计算10%占空比对应的比较值EPwm1Regs.CMPA.half.CMPA = duty_10percent; // PWM1A 10%占空比EPwm1Regs.CMPB = duty_10percent; // PWM1B 10%占空比// Set actionsEPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR; // Clear PWM1A on ZeroEPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM1A on event A, up countEPwm1Regs.AQCTLB.bit.ZRO = AQ_CLEAR; // Clear PWM1B on ZeroEPwm1Regs.AQCTLB.bit.CBU = AQ_SET; // Set PWM1B on event B, up countEPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero eventEPwm1Regs.ETSEL.bit.INTEN = 1; // Enable INTEPwm1Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

}void EPWM2_Init(Uint16 tbprd, Uint16 phase_offset)

{EALLOW;SysCtrlRegs.PCLKCR1.bit.EPWM2ENCLK = 1; // ePWM2EDIS;InitEPwm2Gpio();// EPWM2作为从定时器,接收EPWM1的同步信号EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // 同步输入模式,接收EPWM1的同步EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // 使能相位加载EPwm2Regs.TBPHS.half.TBPHS = phase_offset; // 设置180°相位延迟EPwm2Regs.TBCTR = 0x0000; // Clear counterEPwm2Regs.TBPRD = tbprd; // 周期与EPWM1相同EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Count upEPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV4;EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV16;// Setup shadow register load on ZEROEPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;// Set Compare values - 10%占空比Uint16 duty_10percent = tbprd * 10 / 100; // 计算10%占空比对应的比较值EPwm2Regs.CMPA.half.CMPA = duty_10percent; // PWM2A 10%占空比EPwm2Regs.CMPB = duty_10percent; // PWM2B 10%占空比// Set actionsEPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR; // Clear PWM2A on ZeroEPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // Set PWM2A on event A, up countEPwm2Regs.AQCTLB.bit.ZRO = AQ_CLEAR; // Clear PWM2B on ZeroEPwm2Regs.AQCTLB.bit.CBU = AQ_SET; // Set PWM2B on event B, up countEPwm2Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero eventEPwm2Regs.ETSEL.bit.INTEN = 1; // Enable INTEPwm2Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

}void EPwm1A_SetCompare(Uint16 val)

{EPwm1Regs.CMPA.half.CMPA = val;

}void EPwm1B_SetCompare(Uint16 val)

{EPwm1Regs.CMPB = val;

}void EPwm2A_SetCompare(Uint16 val)

{EPwm2Regs.CMPA.half.CMPA = val;

}void EPwm2B_SetCompare(Uint16 val)

{EPwm2Regs.CMPB = val;

}五、波形分析

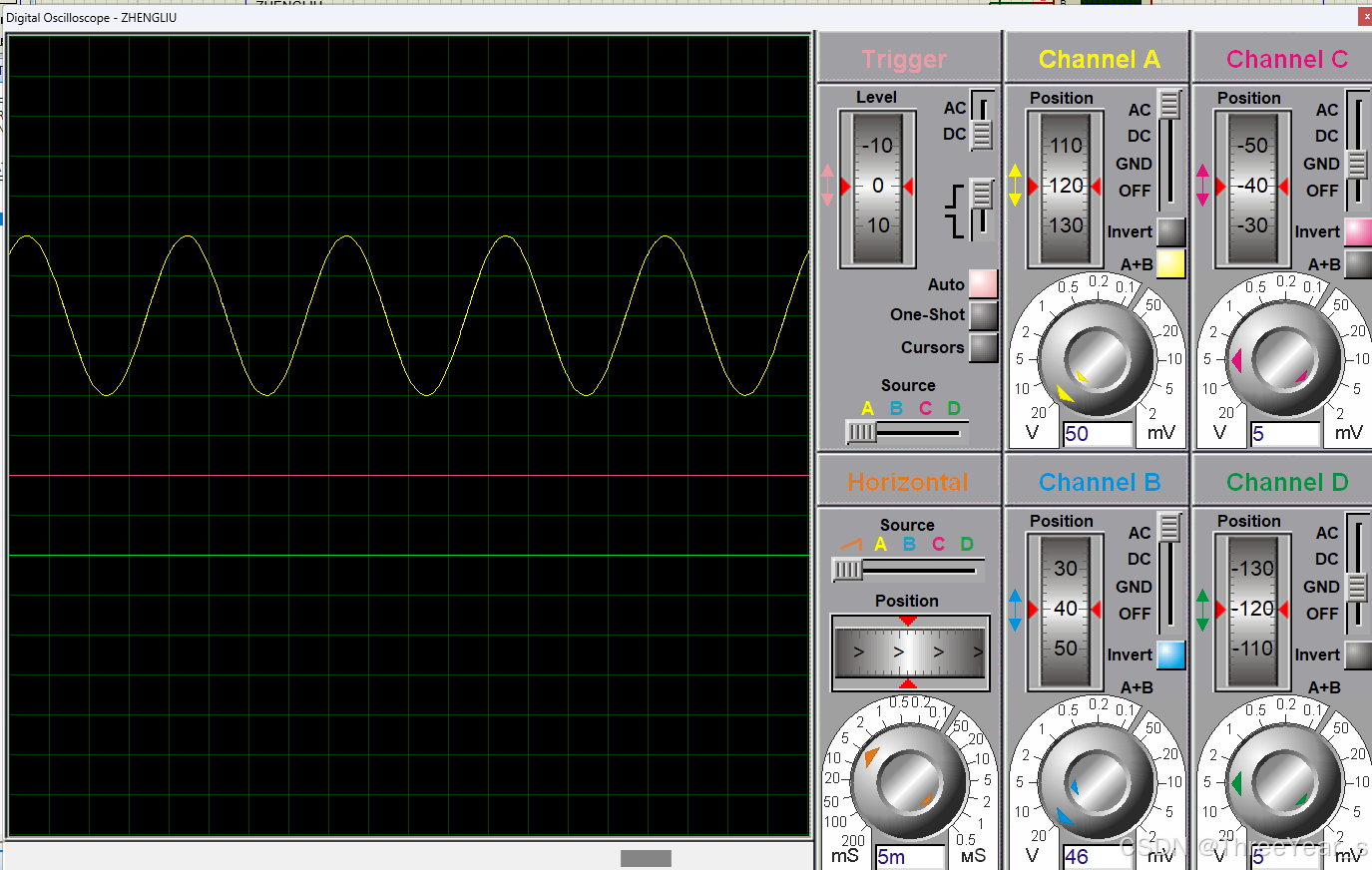

整流前:

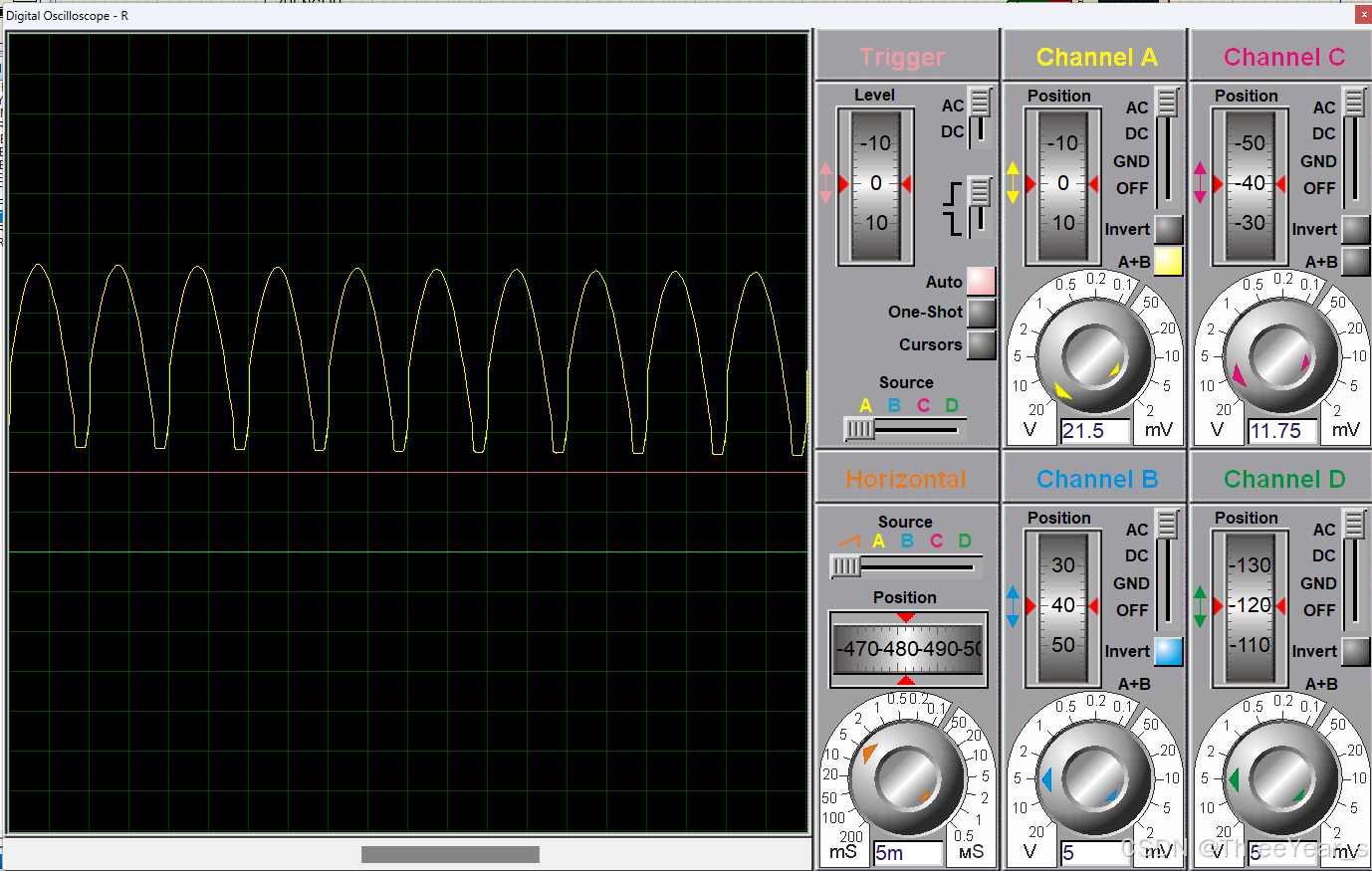

整流效果如下:

总结

自己的小分析,肯定有很多问题和漏洞,希望大家能指出来错误,非常感谢!!!

本文介绍了利用光耦电路将3.3V PWM信号转换为8V电平信号的方法,以满足大功率器件的驱动需求。重点分析了光耦电平转换电路的工作原理,指出输出信号与输入信号反相的特性,并详细讨论了器件选型的关键参数(如正向电流5-15mA、集电极电流5-35mA)。通过Proteus仿真验证了电路设计,并提供了基于DSP的CCS代码实现方案,其中特别调整了PWM输出为"空闲高电平、触发低电平"以匹配光耦转换要求。该方案适用于晶闸管等需较高驱动电平的功率器件控制。