峰值保持电路与峰值提取算法实现放射性核脉冲信号峰值提取

在提取信号参数的过程中,信号中混杂着噪声与干扰,存在幅值大小不一、脉冲尖顶等问题,若直接利用ADC采样,系统能量分辨率较差。调理电路的设计则在于降低 上述问题对测量系统的影响。滤波成形器用作提升信号的信噪比;峰值保持器的设计可 以保持信号的幅度不变,降低ADC的采样难度。因此,调理电路的作用对整个测量系 统而言极其重要。

1.高斯滤波成形器

常见的高斯成形方法包括传统的滤波成形和SK高斯滤波成形。传统的滤波成形电 路主要通过多级RC网络来实现近似高斯脉冲的成形,虽然能够达到顶部平坦、弹道亏损小的效果,但存在结构复杂、元器件使用过多以及电路冗余等问题。相比之下,高斯 滤波成形具有以下优势:网络结构简单,信噪比提升约17%至19%,能量分辨率提高, 成形宽度减小约22%至52%,从而节省了系统死时间并改善了脉冲通过率。鉴于这些优点,本设计采用了高斯滤波成形方案。

2.峰值保持器

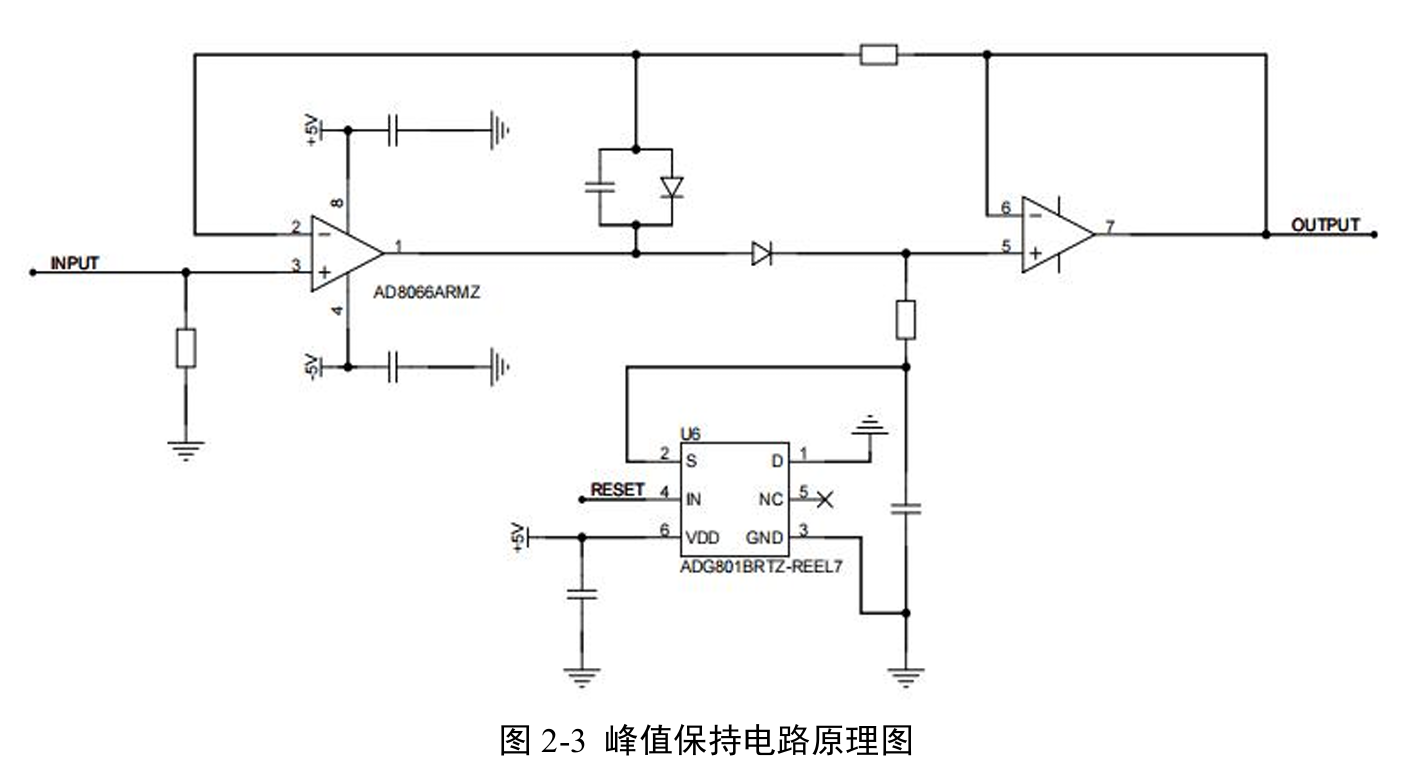

核脉冲信号经过SK滤波成形后,虽然脉冲顶端变平坦,且拥有良好的信噪比,但 是峰值持续时间不够长,对于低速ADC而言采集幅值仍然存在很大困难,而使用高速 ADC 会增加系统成本,以及带来布局复杂、驱动算法复杂等问题。所以需要设计峰值 保持器将核脉冲信号的峰值保持一定时间直至 ADC 采样完成。 峰值保持器由峰值检波电路和电压跟随器组成。峰值检波电路利用二极管的单向导 通性来保持脉冲峰值;电压跟随器用于稳定脉冲峰值。电路图如下:

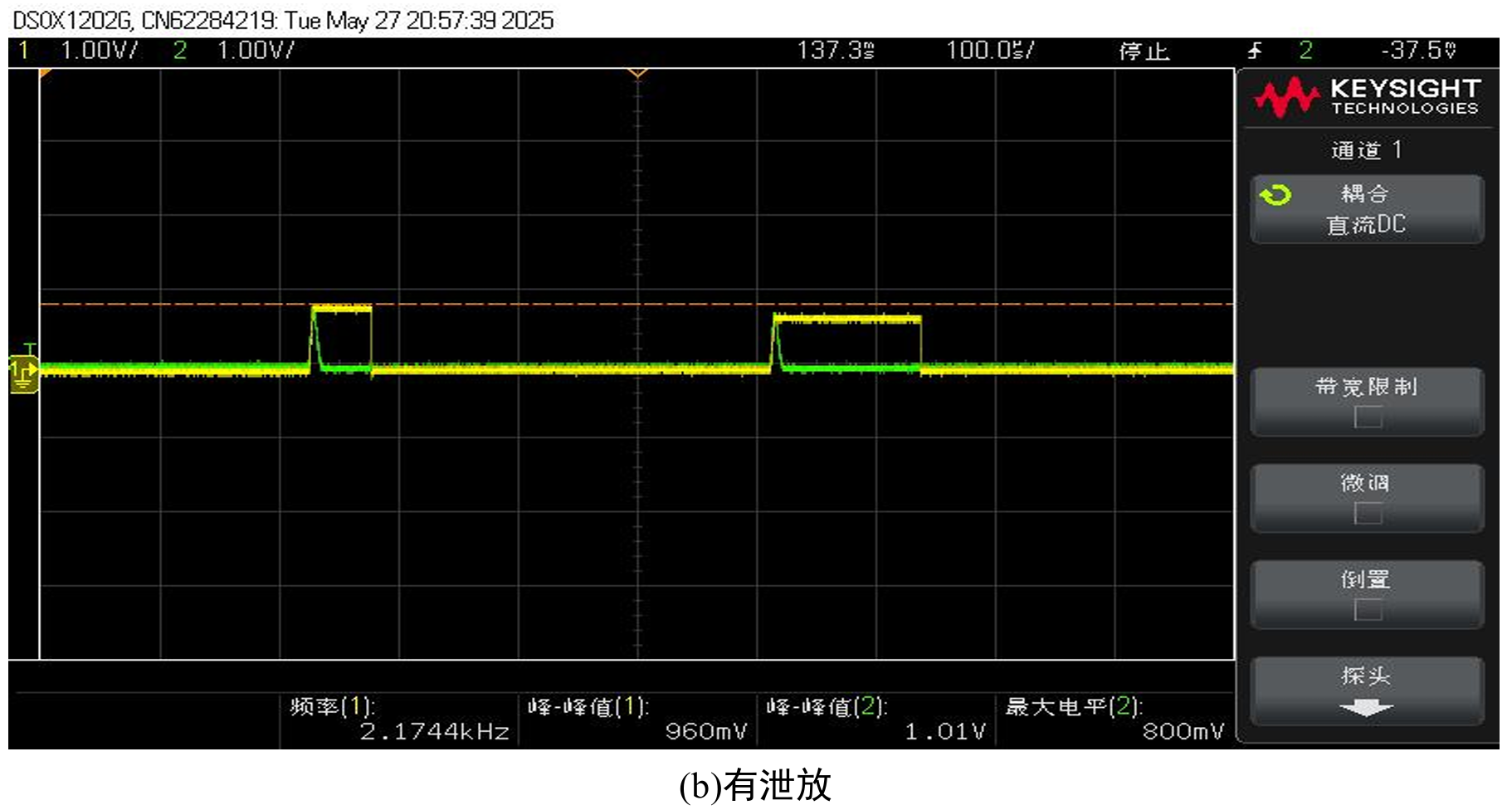

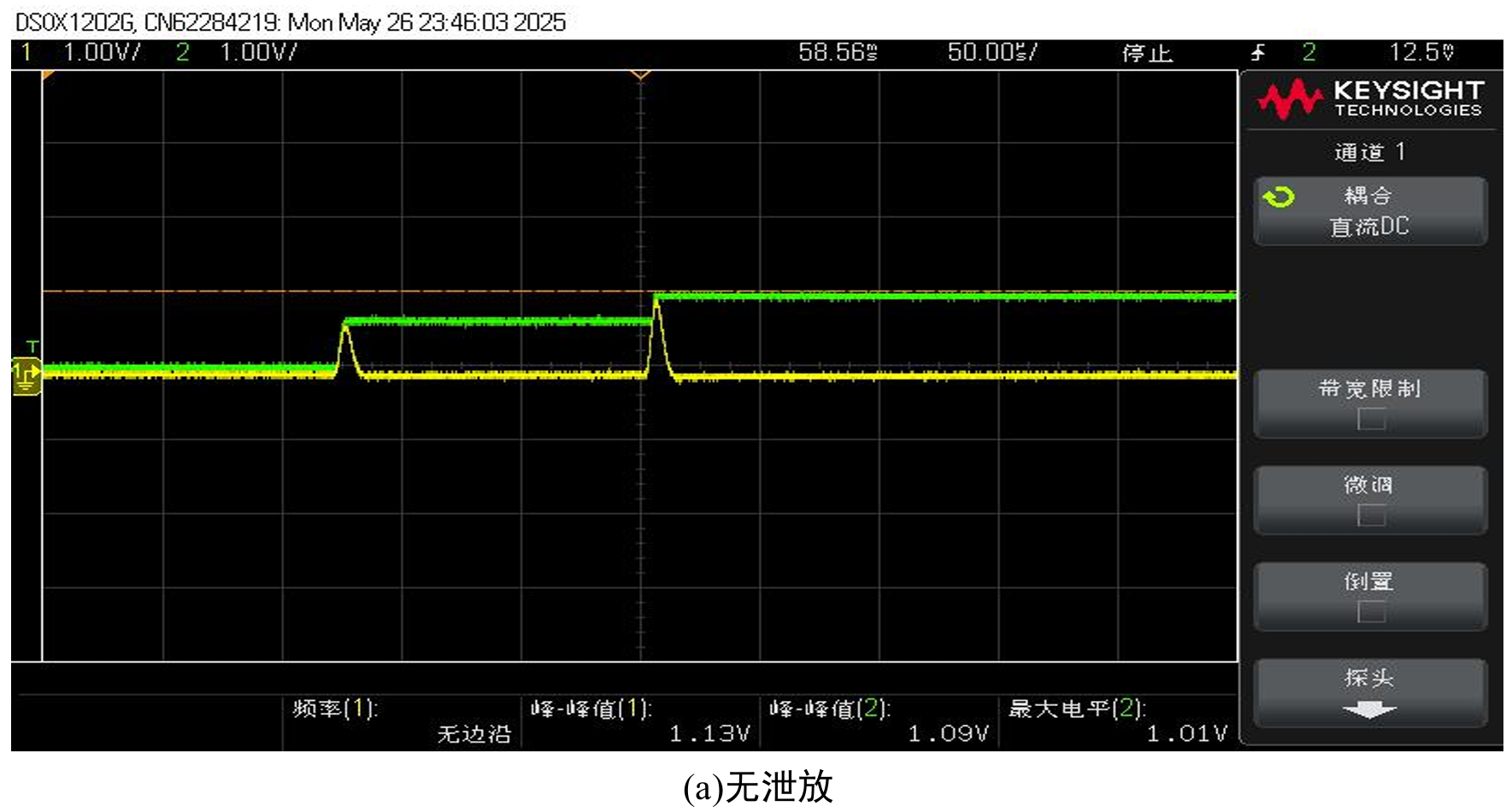

效果如下:

3.峰值提取算法

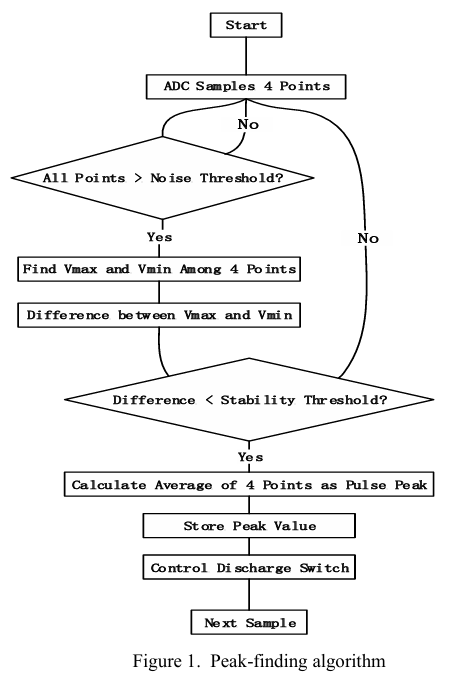

经峰值保持器后,如果不及时泄放电容两端的电压,便会出现上图所示峰值叠加的现象,所以我们需要我们准确的识别峰值后然后控制泄放开关。

信号有效性判决:ADC对输入信号连续进行4次高速采样。首先,将采样值与预设 的噪声阈值进行比较,此步骤旨在滤除基线噪声,确保算法只处理有效的核脉冲事件。

峰值状态识别:在确认信号有效后,算法于4个样本点中寻找最大值(V_max)与 最小值(V_min)。通过计算二者之差(ΔV = V_max - V_min),判断信号是否已达到稳 定峰值。若ΔV小于一个预设的稳定判据(ε),则表明信号已进入峰值保持阶段。

峰值计算与存储:一旦判定信号达到峰值,即取这4个样本点的算术平均值Va作 为本次核脉冲事件的最终幅值。该平均化处理有助于平滑微小波动,获得更可靠的峰值 结果。该结果随即被存储,用于后续能谱构建。

系统快速复位:峰值锁定后,控制器立即驱动泄放开关,将峰值保持电路中的积分电容 电压清零。此操作确保了探测器能够即刻响应下一个到来的核脉冲,是保证系统在高通 量下测量线性度的关键。

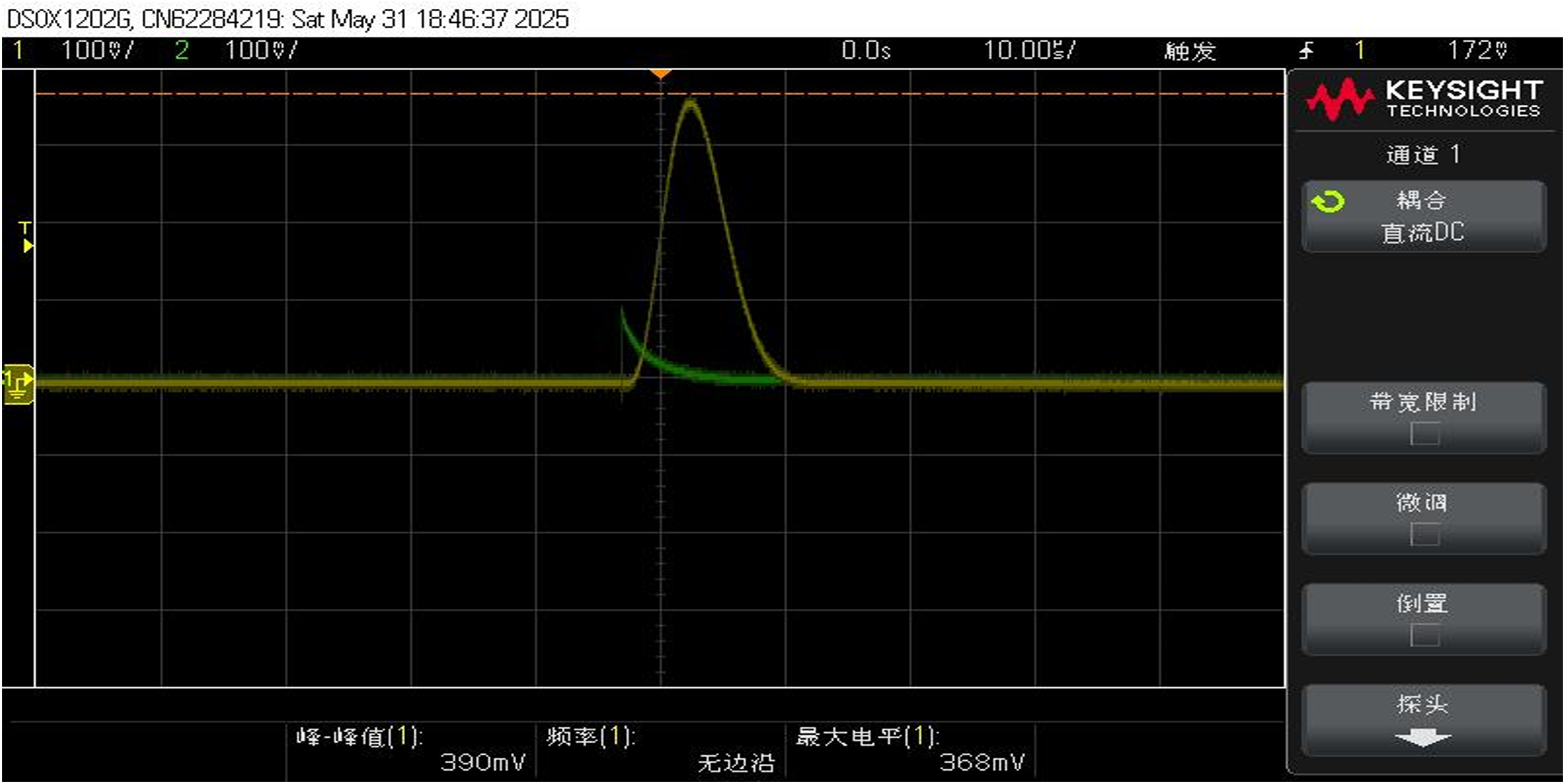

效果如下: