// 双缓冲控制寄存器

reg [31:0] current_w_addr, next_w_addr;

reg [31:0] current_w_length, next_w_length;

reg current_valid, next_valid;// 写入侧 - 更新下一组寄存器

always @(posedge w_clk) beginif (w_frame_start) begin // 帧开始信号next_w_addr <= w_addr;next_w_length <= w_length;next_valid <= 1'b1;end

end// 读取侧 - 切换当前使用的寄存器

always @(posedge r_clk) beginif (current_frame_done) begin // 当前帧读取完成current_w_addr <= next_w_addr;current_w_length <= next_w_length;current_valid <= next_valid;next_valid <= 1'b0; // 清除下一组有效标志end

end

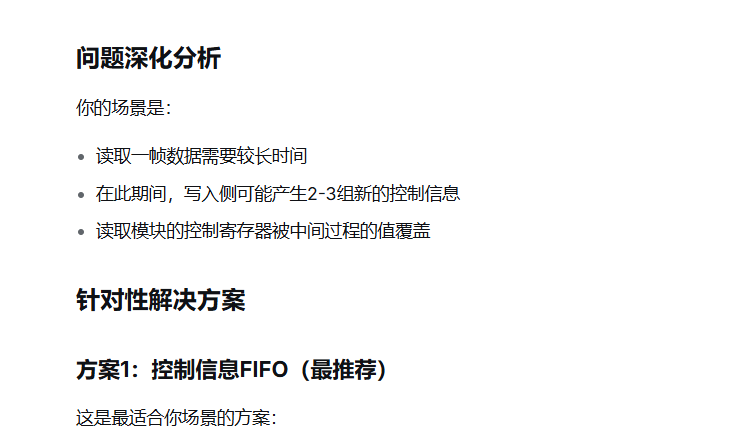

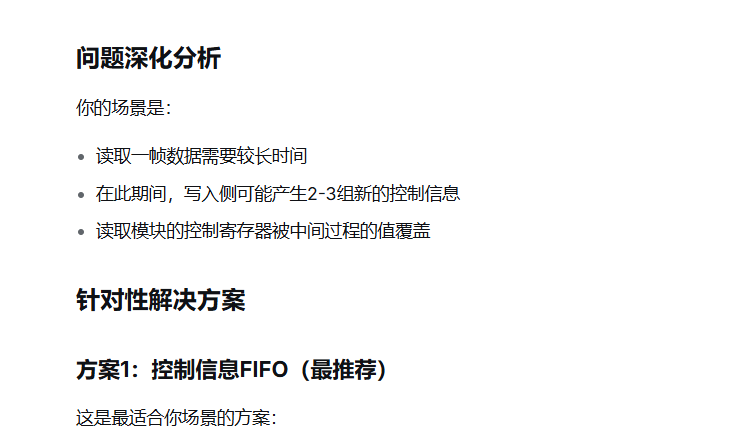

// 控制信息FIFO - 深度根据最大堆积量设计

fifo #(.DATA_WIDTH(64), // 32位地址 + 32位长度.DEPTH(16) // 深度足够容纳堆积的控制信息

) ctrl_fifo (.wr_clk(w_clk),.wr_en(w_frame_start), // 每帧开始时写入控制信息.din({w_addr, w_length}),.rd_clk(r_clk),.rd_en(r_frame_start), // 读取模块开始处理新帧时取出.dout({current_addr, current_length}),.empty(ctrl_fifo_empty),.full(ctrl_fifo_full),.data_count() // 可选的,用于监控堆积情况

);// 读取模块状态机

localparam IDLE = 2'b00;

localparam READING = 2'b01;

localparam DONE = 2'b10;reg [1:0] read_state;always @(posedge r_clk) begincase(read_state)IDLE: if (!ctrl_fifo_empty) beginr_frame_start <= 1'b1;read_state <= READING;endREADING:if (frame_read_done) beginread_state <= DONE;endDONE:beginr_frame_start <= 1'b0;read_state <= IDLE;endendcase

end

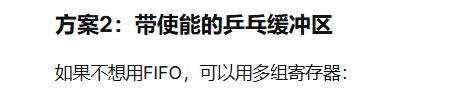

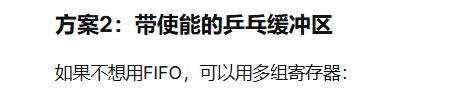

// 三组缓冲区,防止溢出

reg [31:0] addr_buf[0:2];

reg [31:0] len_buf[0:2];

reg [1:0] wr_ptr = 2'b00;

reg [1:0] rd_ptr = 2'b00;

reg [2:0] buf_valid = 3'b000;// 写入侧

always @(posedge w_clk) beginif (w_frame_start && (wr_ptr != rd_ptr || !buf_valid[rd_ptr])) beginaddr_buf[wr_ptr] <= w_addr;len_buf[wr_ptr] <= w_length;buf_valid[wr_ptr] <= 1'b1;wr_ptr <= wr_ptr + 1; // 循环递增end

end// 读取侧

always @(posedge r_clk) beginif (frame_read_done && buf_valid[rd_ptr]) beginbuf_valid[rd_ptr] <= 1'b0;rd_ptr <= rd_ptr + 1; // 循环递增end

end// 当前使用的控制信息

assign current_addr = addr_buf[rd_ptr];

assign current_length = len_buf[rd_ptr];

方案3:基于计数器的同步机制

// 帧计数器同步

reg [7:0] w_frame_cnt = 8'd0;

reg [7:0] r_frame_cnt = 8'd0;

reg [7:0] sync_frame_cnt = 8'd0;// 控制信息RAM

reg [31:0] ctrl_ram [0:255];

reg [7:0] wr_index = 8'd0;// 写入侧

always @(posedge w_clk) beginif (w_frame_start) beginctrl_ram[wr_index] <= {w_addr, w_length}; // 合并存储w_frame_cnt <= w_frame_cnt + 1'd1;wr_index <= wr_index + 1'd1;end

end// 同步计数器到读取时钟域

always @(posedge r_clk) beginsync_frame_cnt <= w_frame_cnt;

end// 读取侧

always @(posedge r_clk) beginif (sync_frame_cnt != r_frame_cnt) begin// 有新的帧信息current_ctrl <= ctrl_ram[r_frame_cnt[7:0]];r_frame_cnt <= r_frame_cnt + 1'd1;end

end