数字上变频DUC与数字下变频DDC的介绍

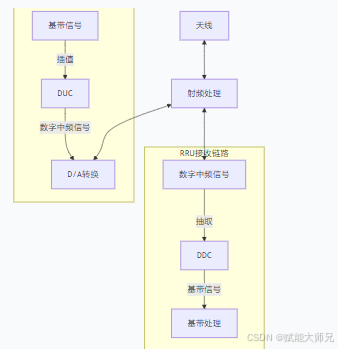

在无线通信,特别是分布式基站(BBU+RRU)架构中,数字上变频(DUC)和数字下变频(DDC)是两项非常关键的技术,它们如同数字信号的“翻译官”,在基带和射频之间搭建起一座桥梁。

分为模拟变频与数字变频两大类:

数字变频:

FPGA中的上变频与下变频称为数字变频,包括,数字上变频DUC(Digital Up Converters)和数字下变频DDC(Digital Down Converters)。

模拟变频:

RFIC中的混频调制和混频解调称为模拟变频,包括模拟上变频和模拟下变频。

一、什么是数字上变频DUC与 数字下变频DDC

- 上变频:

这里是指,通过FPGA数字处理:

频谱搬移:把基带信号从0频附近变换到中频载波上,实现的是频谱向更高频率的搬移,实际上的一种幅度调制。

频谱合并:如果一个天线上需要发送多个载波,需要把多路基带信号(如10M和20M)合并成一路更高带宽(如30M)的中频信号。

- 下变频:

这里是指,通过FPGA数字处理,

频谱分离:如果一个天线上需要发送多个载波,需要把高带宽(如30M)的中频信号,分离成多路不同带宽的基带信号(如10M和20M)。

频谱搬移:把基带信号从中频载波上变换到0频附近,实现的是频谱向更低频率的搬移,实际上是一种解调调制。

二、数字上变频(DUC)

数字上变频主要工作在RRU的发射(下行)链路中。它的核心任务是将低速率的基带信号转换为适合无线发射的高速率中频信号。

核心步骤与关键技术

DUC的实现主要依赖三个核心步骤,它们共同协作,完成信号的“升频”之旅:

-

插值滤波:这是DUC的第一步。由于基带信号的采样率较低,直接上变频会导致频谱混叠。插值滤波器通过在原始采样点之间插入新的采样点,将信号的采样率提高N倍(N为插值因子),为后续的频率搬移准备足够的“空间”。

-

数字混频:插值后的基带信号与一个数字本地振荡器(NCO)产生的正弦/余弦波进行乘法运算。这个乘法过程在频域上相当于将基带信号的频谱从0频附近搬移到中频载波的位置。

-

数字本地振荡器:NCO负责产生高精度、高稳定度的数字正余弦样本,作为混频的“载波”。为了优化性能,常采用泰勒校正算法来提高NCO的杂散抑制比,或者使用CORDIC算法来动态计算振荡器输出,节省硬件资源。

高效的实现策略

在实际的FPGA实现中,为了高效地处理高速数据流,DUC通常采用多级滤波的结构。例如,可以将一个大的插值因子分解为若干个小因子的级联(如2、2、4),并在每一级后接入半带滤波器或CIC滤波器。这种结构能显著降低对单一滤波器性能的要求,从而减少计算量和硬件资源消耗。

三、数字下变频(DDC)

数字下变频是DUC的逆过程,主要工作在RRU的接收(上行)链路中。它的核心任务是将天线接收到的高采样率数字中频信号转换为低速率基带信号,以便后续进行信道解调等处理。

核心步骤与关键技术

DDC的信号处理流程与DUC形成镜像:

-

数字混频:首先,接收到的实数字中频信号与NCO产生的正交本振信号相乘,将信号的频谱从载波频率搬移到基带,输出复数的I、Q两路信号。

-

低通滤波:混频后的信号除了我们需要的基带信号外,还包含高频噪声和其他频段的干扰信号。低通滤波器的作用就是滤除这些带外噪声和干扰,防止它们在后续的降采样过程中发生混叠,污染有用信号。

-

抽取滤波:这是DDC的最后一步。既然信号带宽已经降低,那么采样率也无需保持那么高。抽取滤波器每N个输入样本中只保留一个输出样本,将采样率降低N倍(N为抽取因子),从而大幅降低数据速率,减轻后端DSP的处理压力。

高效的实现策略

与DUC类似,DDC也广泛采用多级抽取的方案。常见的做法是首先使用计算简单的CIC滤波器进行高速率的初步抽取,然后再用半带滤波器或高阶FIR滤波器进行精细滤波和进一步的降采样。这种多级结构在保证性能的同时,极大地优化了资源利用和功耗。

四、什么是模拟上变频与模拟下变频

模拟上变频与模拟下变频简称上变频与下变频。

上变频:这里是指,通过模拟电路(混频),把基带信号从中频载波上变换到高频载波上,实现的是频谱向更高频率的搬移,实际上的一种幅度调制。

下变频:这里是指,通过模拟电路(混频),把基带信号从高频载波上变换到中频载波上,实现的是频谱向更低频率的搬移,实际上是一种解调调制。

模拟变频只负责把一定带宽的模拟信号,从N个连在一起的基带信号,整体上从中频搬移到高频,或从高频搬移到中频。

模拟变频只关注整个带宽,不关注带宽由多少个不同子带宽的基带信号组成。模拟变频只关注,在天线上发送的信号,占据多大的带宽!

五、总结

总而言之,DUC和DDC是现代无线通信,尤其是软件无线电(SDR)理念在RRU中的核心体现。它们通过纯数字信号处理的方式,替代了传统模拟电路繁琐的变频过程,带来了高灵活性、高稳定性和易于重构的巨大优势。