静态时序分析:门控时钟建立时间检查

相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

在静态时序分析中,门控时钟建立时间检查约束了门控单元的门控引脚和时钟引脚之间的时序关系,以满足门控单元的建立时间要求。简单来说就是,如果使用与门作为门控单元,门控时钟建立时间要求门控信号在时钟信号的上升沿到达之前提前到达且稳定一段时间,这是为了不在时钟路径上产生毛刺;如果使用或门作为门控单元,门控时钟建立时间要求门控信号在时钟信号的下降沿到达之前提前到达且稳定一段时间,这也是为了不在时钟路径上产生毛刺。

通常来说,在检查一条时序路径时会有一个发射触发器,即发射数据的触发器(就算是输入端口也会有一个假想的发射触发器);还有一个捕获触发器,即捕获数据的触发器(就算是输出端口也会有一个假想的捕获触发器),进行门控时钟建立时间检查时,我们会使用最大路径即延迟最大的时序路径。

有一点需要特别注意,发射触发器和捕获触发器的时钟并不一定是同一个时钟,虽然在同步设计中常常能保证这一点。门控时钟建立时间检查是从发射时钟的某个有效沿到其后捕获时钟的最近上升/下降沿(不包括同时),这里的先后并不考虑时钟延迟(包括时钟网络延迟和时钟源延迟)、时钟不确定度的,即考虑理想情况。在同步设计中,由于理想情况下时钟是对齐的,因此发射(捕获)时钟的任何一个沿的检查都是等效的·。

对于Design Compiler,是否进行门控时钟建立时间检查和门控时钟建立时间的大小取决于门控时钟的单元是否有相应的属性(gated_fall_clock_setup和gated_rise_clock_setup)(对于离散门控单元)或是能否从逻辑库中获取门控时钟建立时间(对于集成门控单元(ICG)),在门控时钟综合(-gate_clock)后,如果在此之前使用了set_clock_gating_style命令设置了门控时钟建立时间,集成和离散门控时钟单元的相应属性值会被重新设置,否则离散门控单元的相应属性值默认被设置为0,还可以使用set_clock_gating_check命令设置相应属性值。需要注意的是,如果将设计保存为Verilog格式的网表,则其会丢失所有属性,重新读取后必须使用set_clock_gating_check命令设置相应属性值才能对离散门控单元进行门控时钟建立时间检查(集成门控单元可以从逻辑库中获取门控时钟建立时间,因此不需要)。

对于PrimeTime,默认进行门控时钟建立时间检查,集成门控单元从逻辑库中获取相应的属性值而离散门控单元的默认属性值为0,可以使用set_clock_gating_check命令设置相应属性值。

发射时钟和捕获时钟相同

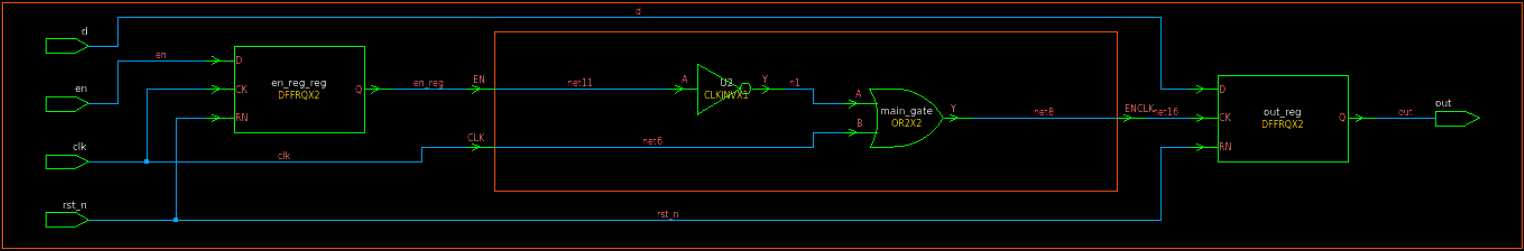

例如对于图1,假设使用离散门控单元或门,其中左边的en_reg_reg是发射触发器而右边的out_reg是捕获触发器。

图1 一个简单的例子

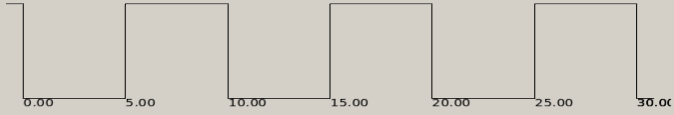

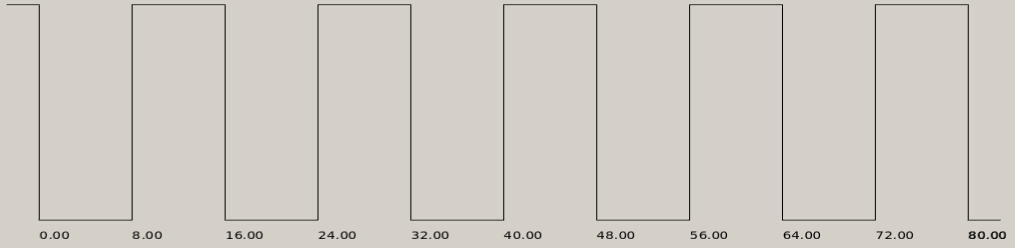

图2是时钟的波形图,周期为10ns,假设D触发器是上升沿触发,则发射触发器会在5ns、15ns、25ns...发射数据,而捕获触发器则相应的会在10ns、20ns、30ns...检查门控时钟建立时间是否满足要求。

图2 时钟波形图

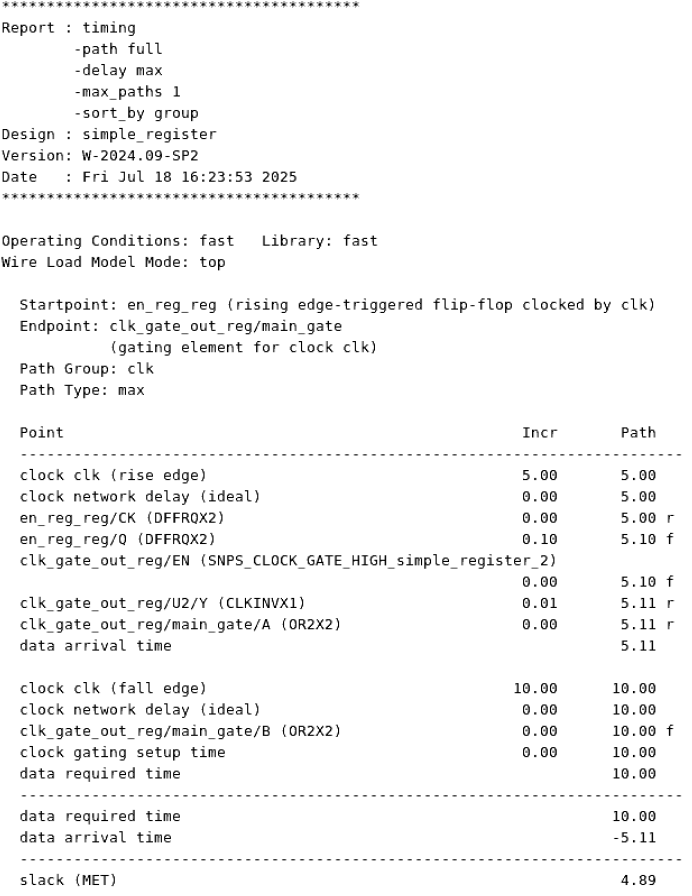

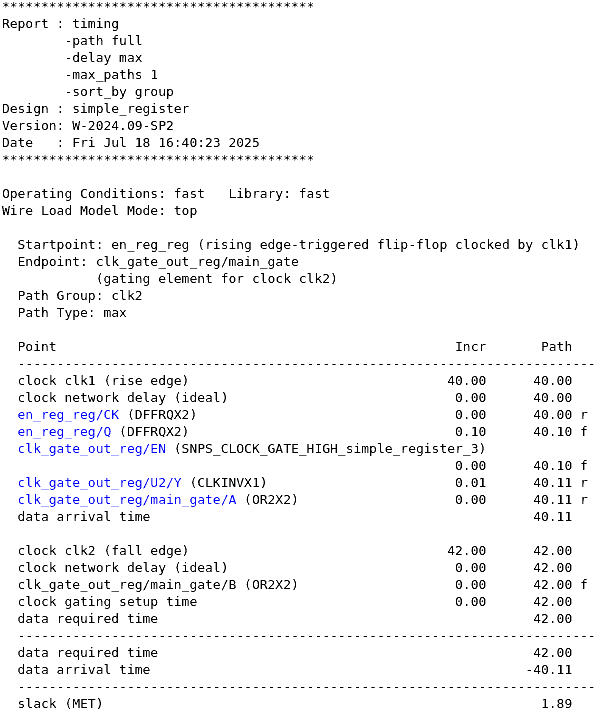

使用report_timing命令可以报告时序检查结果,如图3所示就是从en_reg_reg触发器的时钟引脚CK到门控单元的输入引脚B的时序路径的报告。

图3 门控时钟建立时间时序报告

图3中Path_type为max,表示这是一个门控时钟建立时间检查(或最大延迟时间检查),注意将其与其他SDC命令中的-max和-min选项区分开,并不代表着-max指定的参数就只用于门控时钟建立时间检查,也不代表着-min指定的参数就只用于门控时钟保持时间检查(这取决于工作模式是否为bc_wc模式还是on_chip_variation模式)。

从图3中可以看出,发射时钟选择了5ns时的上升沿而捕获时钟选择了10ns时的下降沿,在报告的最后给出了时序检查的裕度(slack),在满足时序要求的设计中,裕度应该是正的并且留有一定的余量。

发射时钟和捕获时钟不同

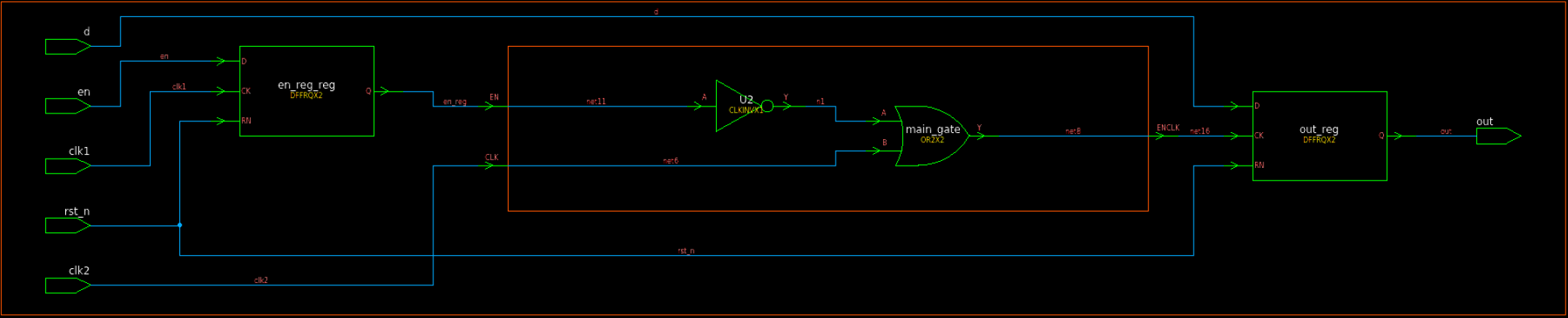

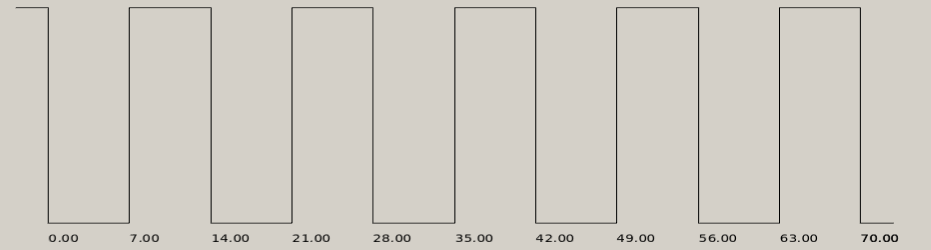

下面来看一个发射时钟和捕获时钟不是同一个时钟的例子。以图4为例,此时en_reg_reg触发器的时钟改为clk1,周期为16,如图5所示;而out_reg触发器的时钟改为clk2,周期为14,如图6所示。

图4 发射时钟和捕获时钟不同的例子

图5 时钟clk1的波形图

图6 时钟clk2的波形图

根据我们的规则,易知发射时钟的有效沿在8ns、24ns、40ns、56ns...,而捕获时钟需要检查的相应有效沿在14ns、28ns、42ns、70ns...。在进行建立时间检查时,会对最难满足条件的时钟沿时刻组合进行检查,即相隔最短的一组时刻,在本例中为发射时钟在40ns而捕获时钟在42ns时。图7的时序报告证明了这一分析。

图7 门控时钟建立时间时序报告