硬核电子工程:从硅片到系统的全栈实战指南—— 融合电路理论、嵌入式开发与PCB设计的工程艺术

一、电路基础:硬件设计的底层逻辑

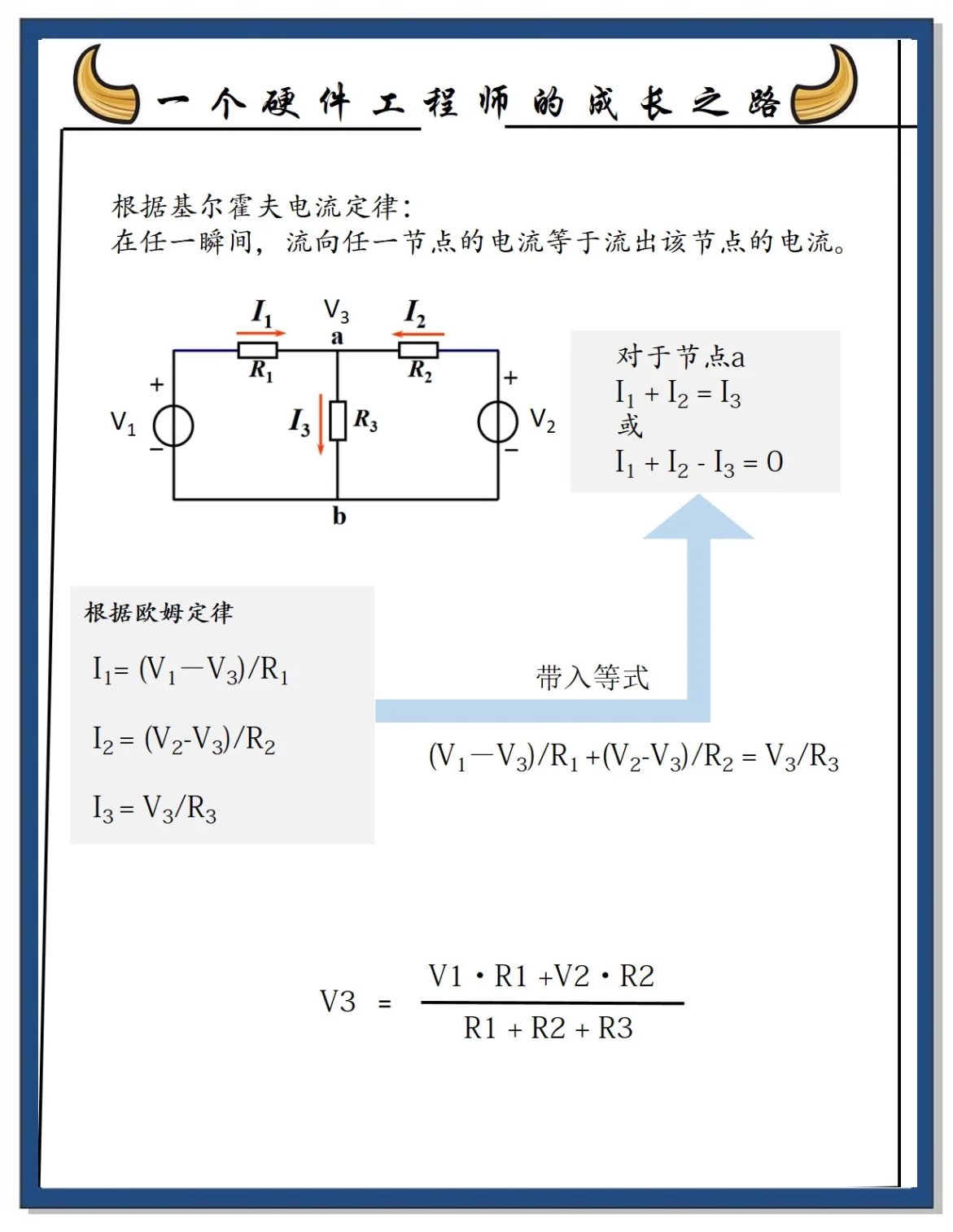

1.1 基尔霍夫定律的硬件实现

// STM32验证KVL定律(ADC采样法)

void verify_kvl() {ADC_Enable(ADC1); // 启用ADCfloat Vr1 = read_ADC(PA0) * 3.3 / 4096; // 读取R1电压float Vr2 = read_ADC(PA1) * 3.3 / 4096; // 读取R2电压float Vsrc = 3.3; // 电源电压// KVL验证: ΣV = Vsrc - Vr1 - Vr2 ≈ 0if(fabs(Vsrc - Vr1 - Vr2) < 0.05) {UART_Send("KVL验证通过!误差<50mV\n");} else {UART_Send("警告:电路存在异常损耗!\n");}

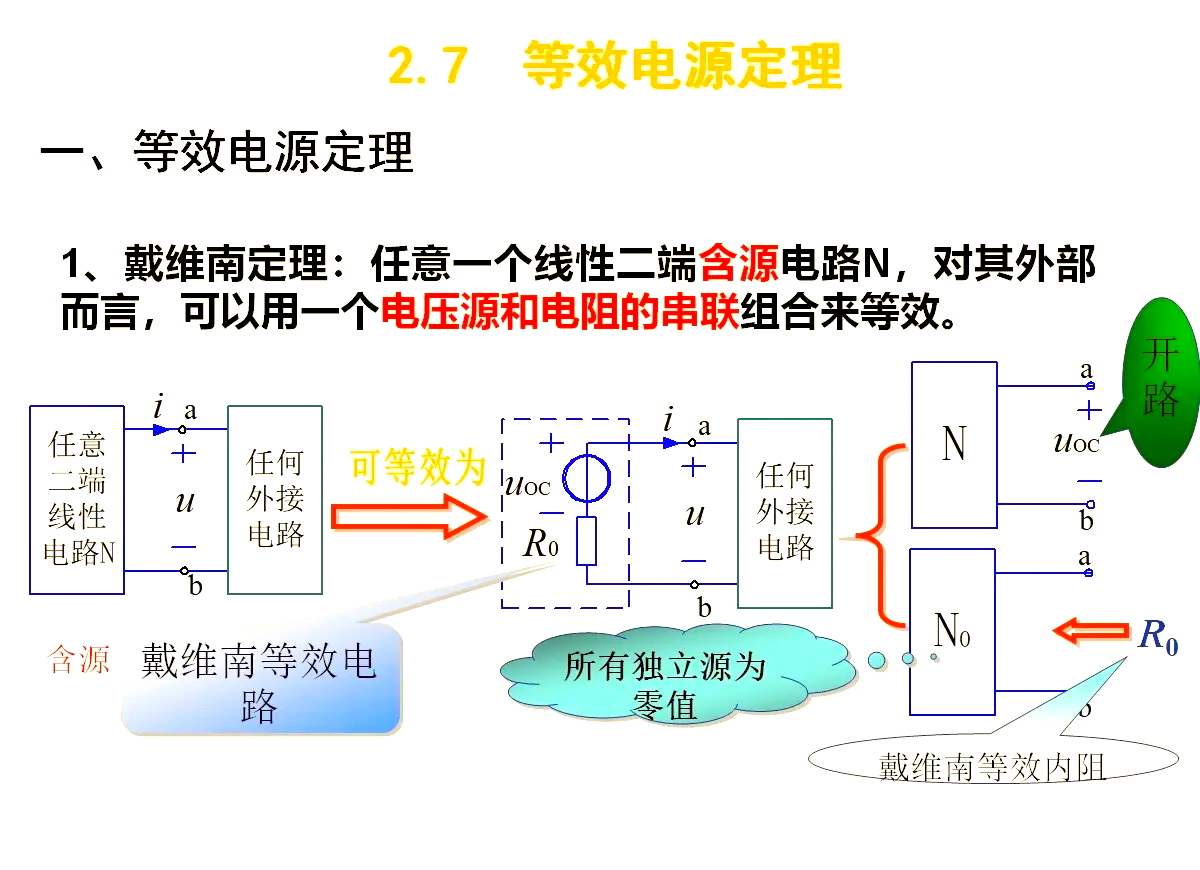

}1.2 戴维南等效的工程应用

锂电池供电系统等效模型:

+-----------------+

[18650 3.7V]─┤ 内阻Rint=80mΩ ├───┬──[负载]+-----------------+ │[C=100μF] // 去耦电容│GND设计公式:

# Python计算最大输出功率

def max_power(V_oc, R_int):return (V_oc**2) / (4 * R_int) # 当R_load = R_int时print(f"18650最大功率: {max_power(3.7, 0.08):.2f}W") # 输出: 42.91W二、模拟电子:信号链设计精髓

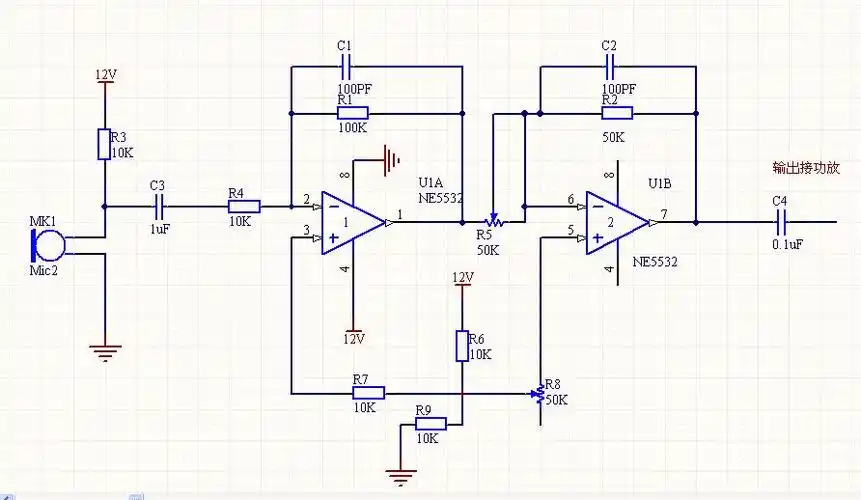

2.1 多级放大系统设计

麦克风→前置放大→功率放大→扬声器:

text

复制

下载

[Mic]─┬─[2.2kΩ]─┐│ ▼├─[OPA2171]───[10kΩ]─┬─[LM386]─┬─[SPK]└───[1MΩ]◄───[100nF]─┘ │[220μF]─┘

2.2 有源滤波器实战

// Verilog实现数字滤波器 (FPGA版本)

module lowpass_filter(input clk, input [11:0] adc_data,output reg [11:0] filtered

);reg [31:0] accumulator;

parameter ALPHA = 0.05; // 截止频率调整因子always @(posedge clk) beginaccumulator <= accumulator + (adc_data - accumulator) * ALPHA;filtered <= accumulator >> 16; // 位宽调整

end

endmodule三、数字系统:硬件加速之道

3.1 高速计数器设计

FPGA实现32位100MHz计数器:

module high_speed_counter(input clk_100m,input reset_n,output reg [31:0] count

);always @(posedge clk_100m or negedge reset_n) beginif(!reset_n) count <= 32'd0;else count <= count + 1'b1;

end// 时序约束(XDC文件)

create_clock -period 10 [get_ports clk_100m]

set_input_delay -clock clk_100m 2 [all_inputs]3.2 状态机硬件实现

电机控制状态机:

// C语言实现状态机(ARM Cortex-M)

typedef enum {STOP, ACCEL, RUN, BRAKE

} MotorState;void motor_control() {static MotorState state = STOP;switch(state) {case STOP:if(start_btn) {PWM_SetDuty(10);state = ACCEL;}break;case ACCEL:if(current_speed >= target) {state = RUN;} else {PWM_Increase(1);}break;// ...其他状态}

}四、电源设计:硬件系统的生命线

4.1 高效Buck电源设计

PCB布局关键点:

+---------+ +------------+│ Vin ├────►│ SW Node │◄─[注意最小回路面积!]+---------+ +------┬-----+[10μF陶瓷] ▼[电感]▼+---------+ +------┴-----+│ GND ◄─────┤ 输出电容 │◄──[3×22μF陶瓷]+---------+ +------------+4.2 电源完整性分析

# Python计算目标阻抗

def calc_target_impedance(dv, di, dt):return dv / (di/dt) # 瞬态响应要求# 示例:CPU核心供电需求

dv = 0.05 # 允许纹波50mV

di = 15 # 负载瞬变15A

dt = 1e-6 # 响应时间1μs

print(f"目标阻抗: {calc_target_impedance(dv, di, dt):.3f}Ω") # 3.33mΩ五、综合项目:智能温控系统

硬件架构:

[DS18B20]───[STM32]───[OLED]│ ├───[继电器]─[加热器]│ └───[ESP32]─┬─[手机APP]│ └─[云平台][ADC]─[NTC热敏电阻]关键代码实现:

// 温度控制PID核心算法

void PID_Update(float setpoint, float actual) {static float integral = 0;static float last_error = 0;float error = setpoint - actual;// PID参数const float Kp = 2.0, Ki = 0.01, Kd = 1.0;// 抗积分饱和处理if(fabs(error) < 5.0) {integral += error;}float derivative = error - last_error;float output = Kp*error + Ki*integral + Kd*derivative;// 输出限幅output = constrain(output, 0, 100);PWM_SetDuty(output);last_error = error;

}硬件工程师生存法则

信号完整性(SI)黄金三原则:

关键信号:阻抗控制 ±10%

时钟走线:长度匹配 ±50mil

高速差分:等长 ±5mil

电磁兼容(EMC)设计:

# EMC优化层级 1. 源头抑制 → 2. 路径阻断 → 3. 受体保护│ │ │▼ ▼ ▼[斜率控制] [屏蔽罩] [滤波电路][展频技术] [地分割] [布局优化]热设计公式:

T_j = T_a + (P_d × θ_ja) ▏ ▏ T_j:结温(℃) ▏ T_a:环境温度(℃) ▏ P_d:器件功耗(W) ▏ θ_ja:热阻(℃/W)

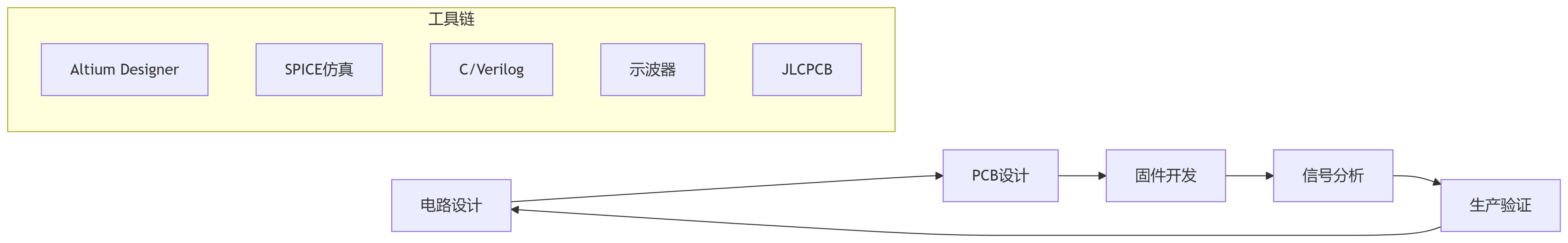

硬件开发技术栈

硬件工程师的终极信条:

“示波器不会说谎,但只有理解电磁场本质的人才能听懂它的语言。真正的硬件大师,既能在SPICE仿真中预测纳秒级的信号振铃,也能在PCB上雕刻出满足EMC标准的艺术品,更能用C语言赋予硅片以智能生命。”