改进的霍尔迁移率测量方法区分4H-SiC反型沟道中的界面俘获效应

标题

Improved Hall Mobility Measurement Distinguishing Interface Capturing Effect in 4H-SiC Inversion Channel

文章的研究内容

本文的研究内容是提出一种改进的霍尔迁移率(μHall)测量方法,用于区分4H-SiC反型通道中界面陷阱对电子迁移率的影响,并准确提取反型通道中可移动电子的迁移率。以下是文章的核心研究内容和主要发现:

- 研究背景

4H-SiC(碳化硅)作为一种宽禁带半导体材料,因其在高效率、高功率和高温电子应用中的优势而受到广泛关注。然而,4H-SiC MOSFET的特定电阻受到反型通道电子迁移率的严重限制。目前,商业4H-SiC MOSFET产品的反型通道电子迁移率通常较低(15 - 25 cm²/(V·s)),远低于4H-SiC材料的理想电子迁移率(约900 cm²/(V·s))。因此,准确评估反型通道电子迁移率并提升其性能具有重要意义。 - 研究目的

传统的场效应迁移率(μFE)测量方法假设所有诱导的电子都是可移动的,但实际上,由于4H-SiC/SiO₂界面处的陷阱捕获效应,反型层中75% - 90%的电子被固定,导致μFE测量值偏低且不准确。本文旨在通过改进的霍尔迁移率测量方法,区分界面陷阱的影响,准确提取反型通道中可移动电子的迁移率(μHall)。 - 研究方法

(1)改进的霍尔迁移率测量方法

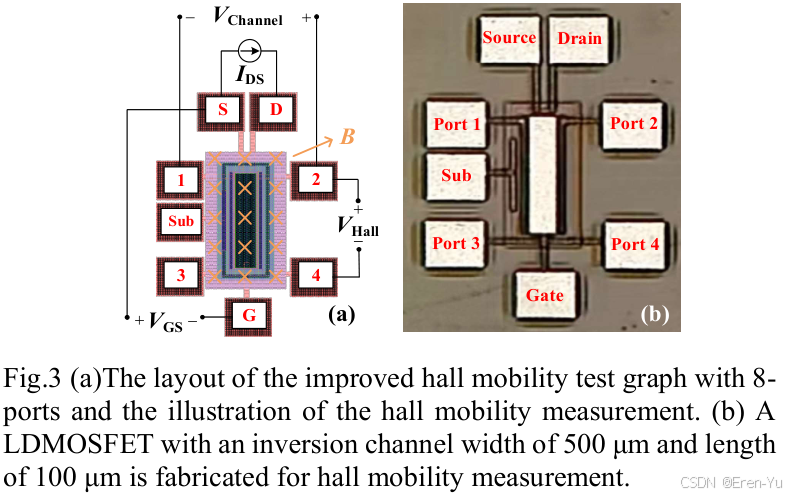

文章设计了一种改进的霍尔迁移率测量方法,通过在4H-SiC LDMOSFET中施加正栅压(VGS)诱导反型通道电子,同时施加正漏压(VDS)使N⁺源区的可移动电子漂移到漏极。当施加垂直于电子电流平面的磁场(B)时,可移动电子会受到洛伦兹力(fL)的作用而偏转,并在通道下侧(端口3和4)积累,从而产生霍尔电压(VHall)。通过测量VHall,可以计算出μHall。

(2)实验设计

文章设计并制备了两种类型的SiC LDMOSFET:一种用于霍尔迁移率测量(通道宽度500 μm,长度100 μm,8个端口,包括4个霍尔探针),另一种用于场效应迁移率测量(通道宽度160 μm,长度740 μm)。实验中,通过改变VGS、IDS和B的值,研究μHall的变化规律。

(3)测量平台

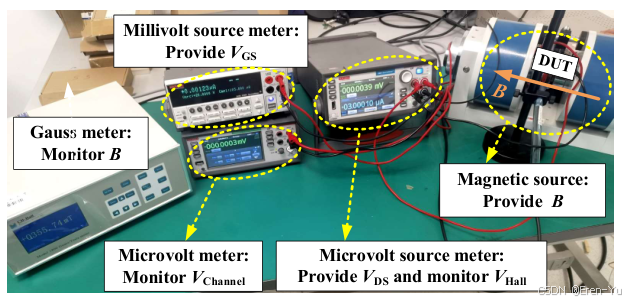

文章构建了一个霍尔迁移率测量平台,能够提供最大1特斯拉的磁场,并测量低至1微伏的VHall。该平台允许测量低至10 cm²/(V·s)的μHall,测量误差小于0.1 cm²/(V·s)。 - 实验结果与讨论

(1)μHall与μFE的对比

实验结果显示,μHall和μFE分别为92.3 cm²/(V·s)和20.6 cm²/(V·s),μHall显著高于μFE。这表明,由于界面陷阱的存在,μFE低估了反型通道中可移动电子的真实迁移率。

(2)μHall的影响因素

VGS的影响:随着VGS的增加,μHall增加。这是因为更高的VGS可以释放被界面陷阱捕获的电子,减少库仑散射,从而提高迁移率。

IDS的影响:随着IDS的增加,μHall降低。这是因为LDMOSFET进入夹断区,VDS在反型通道中非均匀分布,导致VChannel被高估,μHall被低估。

B的影响:随着B的增加,μHall增加。这是因为较大的磁场会导致电子反向运动并最终离开通道,导致实际可移动电子数量被低估,从而μHall被高估。

(3)电子密度的提取

通过μHall和总反型电子密度(Qtotal),文章提取了可移动电子密度(Qmobile = 31.80 nC/cm²)和被界面陷阱捕获的电子密度(Qit = 109.28 nC/cm²)。结果表明,反型通道中77.46%的电子被界面陷阱捕获,只有22.54%的电子是可移动的。 - 研究结论

本文提出的改进霍尔迁移率测量方法能够有效区分4H-SiC/SiO₂界面陷阱的影响,并准确提取反型通道中可移动电子的迁移率。实验结果表明,μHall显著高于μFE,且大部分反型通道电子被界面陷阱捕获。这些发现为改进4H-SiC反型通道电子迁移率问题提供了重要的指导。 - 研究意义

本文的研究不仅提供了一种准确测量4H-SiC反型通道电子迁移率的新方法,还揭示了界面陷阱对电子迁移率的影响机制,为优化4H-SiC MOSFET的性能和提高其电子迁移率提供了理论依据和实验支持。

文章的研究方法

文章提出了一种改进的霍尔迁移率(μHall)测量方法,用于区分4H-SiC反型通道中界面陷阱对电子迁移率的影响,并准确提取反型通道中可移动电子的迁移率。以下是文章中详细描述的研究方法:

- 改进的霍尔迁移率测量方法

文章的核心是通过霍尔效应测量来区分界面陷阱的影响,并提取反型通道中可移动电子的迁移率(μHall)。具体步骤如下:

(1)实验设计

器件结构:设计并制备了两种类型的SiC LDMOSFET器件:

霍尔迁移率测量器件:通道宽度为500 μm,长度为100 μm,包含8个端口(4个霍尔探针)。这种结构用于测量μHall。

场效应迁移率测量器件:通道宽度为160 μm,长度为740 μm,用于测量传统的场效应迁移率(μFE)。

器件参数:两种器件的氧化层厚度均为40 nm,P-well浓度为1×10¹⁸ cm⁻³。

(2)测量原理

当施加正栅压(VGS)时,4H-SiC反型通道中诱导出电子。

施加正漏压(VDS)使N⁺源区的可移动电子漂移到漏极。

施加垂直于电子电流平面的磁场(B),可移动电子在洛伦兹力(fL)作用下偏转,并在通道下侧(端口3和4)积累,形成霍尔电压(VHall)。

通过测量VHall,根据公式计算μHall:

μHall=B⋅VChannel⋅L12VHall⋅W

其中,W为通道宽度,VChannel为端口1和2之间的电压,L12为端口1和2之间的距离。

(3)测量平台

构建了一个霍尔迁移率测量平台,能够提供最大1特斯拉的磁场,并测量低至1微伏的VHall。

平台包括:

高斯计:用于监测磁场强度。

微伏表:用于监测VChannel。

微伏源表:用于提供VDS并监测VHall。

毫伏源表:用于提供VGS。

该平台允许测量低至10 cm²/(V·s)的μHall,测量误差小于0.1 cm²/(V·s)。 - 实验过程

(1)测量条件

在不同VGS(栅源电压)、IDS(漏源电流)和B(磁场强度)条件下测量μHall。

实验中,VGS范围为10 V到20 V,IDS范围为0.1 μA到5 μA,B范围为377 mT到573 mT。

(2)数据采集

通过改变VGS、IDS和B的值,记录不同条件下的VHall。

根据公式计算μHall,并分析其随VGS、IDS和B的变化规律。 - 对比方法

文章还对比了传统的场效应迁移率(μFE)测量方法。μFE通过测量器件的转移特性计算得出,公式如下:

μFE=W⋅Cox⋅VDSL⋅dVGSdIDS

其中,L和W分别为通道长度和宽度,Cox为氧化层电容,VDS为漏源电压。 - 关键改进点

(1)几何结构优化

为了提高VHall的测量精度,文章优化了器件的几何结构。选择通道宽度为500 μm、长度为100 μm的LDMOSFET,以在VHall的幅度和稳定性之间取得平衡。

在小IDS(如0.1 μA)条件下,VHall可达到0.1 mV以上,且波动小于几微伏,便于精确测量。

(2)磁场影响分析

文章首次详细分析了磁场强度(B)对μHall的影响。实验发现,随着B的增加,μHall增加,这是由于磁场导致电子反向运动并最终离开通道,导致实际可移动电子数量被低估,从而μHall被高估。

(3)电子密度提取

通过μHall和总反型电子密度(Qtotal),提取了可移动电子密度(Qmobile)和被界面陷阱捕获的电子密度(Qit):

Qmobile=μHallσQit=Qtotal−Qmobile

其中,σ为反型通道电导率。 - 研究方法总结

文章通过改进的霍尔迁移率测量方法,结合优化的器件结构和高精度测量平台,成功区分了4H-SiC反型通道中界面陷阱对电子迁移率的影响,并准确提取了可移动电子的迁移率(μHall)。这种方法克服了传统场效应迁移率测量方法的局限性,为研究和改进4H-SiC器件的反型通道电子迁移率提供了新的技术手段。

文章的创新点

- 改进的霍尔迁移率测量方法

文章提出了一种新的霍尔迁移率(μHall)测量方法,专门用于区分4H-SiC反型通道中界面陷阱对电子迁移率的影响。这种方法能够准确提取反型通道中可移动电子的迁移率,而传统方法(如场效应迁移率μFE)由于界面陷阱的存在而无法准确测量。

创新点:

传统方法假设所有诱导的电子都是可移动的,但实际上大部分电子被界面陷阱捕获。本文通过霍尔效应测量,成功区分了可移动电子和被捕获电子的贡献。

提出了一种新的测量平台和方法,能够测量低至10 cm²/(V·s)的μHall,测量误差小于0.1 cm²/(V·s),精度远高于传统方法。 - 磁场对霍尔迁移率影响的详细分析

文章首次详细研究了磁场强度(B)对μHall的影响,并揭示了其物理机制。实验发现,随着磁场强度的增加,μHall显著增加,这是由于磁场导致电子的反向运动,最终使部分电子离开通道,从而导致可移动电子数量被低估。

创新点:

以往研究中,磁场对μHall的影响未被充分探讨。本文通过实验和理论分析,揭示了磁场强度对μHall的定量影响,为准确测量μHall提供了新的指导。

提出了在小磁场和小漏源电流(IDS)条件下测量μHall的建议,以获得更准确的结果。 - 器件结构和测量平台的优化

文章设计并制备了专门用于霍尔迁移率测量的SiC LDMOSFET器件,并构建了一个高精度的测量平台。通过优化器件的几何结构,成功提高了霍尔电压(VHall)的测量精度和稳定性。

创新点:

设计了一种具有500 μm通道宽度和100 μm通道长度的LDMOSFET,包含8个端口(4个霍尔探针)。这种结构在VHall的幅度和稳定性之间取得了良好平衡。

构建了一个能够提供最大1特斯拉磁场的测量平台,能够测量低至1微伏的VHall,显著提高了测量精度。 - 界面陷阱电子密度的定量提取

通过对比μHall和μFE,文章成功提取了反型通道中可移动电子密度(Qmobile)和被界面陷阱捕获的电子密度(Qit)。实验结果表明,反型通道中77.46%的电子被界面陷阱捕获,只有22.54%的电子是可移动的。

创新点:

通过改进的霍尔迁移率测量方法,定量分析了界面陷阱对反型通道电子迁移率的影响,为理解4H-SiC/SiO₂界面特性提供了新的视角。

提供了一种定量评估界面陷阱密度的方法,有助于指导4H-SiC器件的界面工程和性能优化。 - 对4H-SiC器件性能优化的指导意义

本文的研究结果为改进4H-SiC反型通道电子迁移率问题提供了重要的指导。通过揭示界面陷阱对电子迁移率的影响机制,文章为优化4H-SiC MOSFET的性能和提高其电子迁移率提供了理论依据和实验支持。

创新点:

提供了一种新的技术手段,用于评估和改进4H-SiC器件的界面质量。

为未来4H-SiC功率器件的设计和制造提供了有价值的参考,特别是在提高器件效率和降低导通电阻方面。

总结

本文的创新点在于提出了一种改进的霍尔迁移率测量方法,能够准确区分界面陷阱的影响,并提取反型通道中可移动电子的迁移率。通过优化器件结构和测量平台,文章不仅提高了测量精度,还揭示了磁场对μHall的影响机制,并定量分析了界面陷阱对电子迁移率的影响。这些创新为4H-SiC器件的性能优化提供了重要的理论和实验基础。

文章的结论

文章的结论部分总结了改进的霍尔迁移率(μHall)测量方法的主要成果和意义,以下是其核心内容:

结论

本文提出了一种改进的霍尔迁移率测量方法,用于区分4H-SiC/SiO₂界面处陷阱对反型通道电子迁移率的影响。通过设计和制备两种类型的SiC LDMOSFET器件(一种用于测量μHall,另一种用于测量传统的场效应迁移率μFE),并基于自建的测量平台,得到了以下关键结论:

μHall与μFE的差异

实验测得的反型电子的μHall为92.3 cm²/(V·s),而μFE仅为20.6 cm²/(V·s)。这表明,由于界面陷阱的存在,μFE显著低估了反型通道中可移动电子的真实迁移率。μHall的测量结果揭示了更高的电子迁移率,反映了界面陷阱对电子迁移率的显著影响。

界面陷阱的影响

通过提取反型通道中的可移动电子密度(Qmobile = 31.80 nC/cm²)和总反型电子密度(Qtotal = 141.08 nC/cm²),计算出被界面陷阱捕获的电子密度(Qit = 109.28 nC/cm²)。结果表明,反型通道中77.46%的电子被界面陷阱捕获,只有22.54%的电子是可移动的。这一发现解释了μFE的低值及其正温度系数现象,即温度升高时,被捕获的电子释放进入导带,导致μFE增加。

测量方法的指导意义

本文的μHall测量方法能够准确反映4H-SiC/SiO₂界面的质量,并为改进反型通道电子迁移率问题提供了重要指导。通过优化器件结构和测量条件(如小磁场和小漏源电流下测量μHall),可以更准确地评估反型通道的电子迁移率。

对器件性能优化的启示

研究结果表明,界面陷阱是限制4H-SiC MOSFET性能的关键因素之一。通过减少界面陷阱密度,有望显著提高反型通道电子迁移率,从而降低器件的导通电阻,提升其在高功率和高温应用中的性能。

总结

本文提出的改进霍尔迁移率测量方法为准确评估4H-SiC反型通道电子迁移率提供了一种新的技术手段。通过揭示界面陷阱对电子迁移率的影响机制,本文为优化4H-SiC MOSFET的界面质量和提升器件性能提供了重要的理论依据和实验支持。